# Investigation of TSV induced thermo-mechanical stress: implementation of piezoresistive sensors and correlation with simulation

Online: 2014-08-11

Komi Atchou EWUAME<sup>1,2,a\*</sup>, Vincent FIORI<sup>1,b</sup>, Karim INAL<sup>2,c</sup>,

Pierre-Olivier BOUCHARD<sup>2,d</sup>, Sébastien GALLOIS-GARREIGNOT<sup>1,e</sup>,

Sylvain LIONTI<sup>1,f</sup>, Clément TAVERNIER<sup>1,g</sup>, Hervé JAOUEN<sup>1,h</sup>

<sup>1</sup>STMicroelectronics, 850 rue Jean Monnet, 38926 Crolles Cedex, France <sup>2</sup>CEMEF, Mines ParisTech, rue Claude Daunesse CS 10207, 06904 Sophia Antipolis Cedex, France

<sup>a</sup>komiatchou.ewuame@st.com, <sup>b</sup>vincent.fiori@st.com, <sup>c</sup>karim.inal@mines-paristech.fr, <sup>d</sup>pierre-olivier.bouchard@mines-paristech.fr, <sup>e</sup>sebastien.gallois-garreignot@st.com, <sup>f</sup>sylvain.lionti@st.com, <sup>g</sup>clement.tavernier@st.com, <sup>h</sup>herve.jaouen@st.com

**Keywords**: Residual stress, Piezoresistive stress sensor, TSV, Thermomechanics, FEM Simulation

**Abstract:** This work deals with a methodology to evaluate residual stresses within microelectronic devices by using MOS (Metal Oxide Semiconductor) rosette stress sensors. The stress tensor was evaluated by carrying out electrical measurements on test vehicle: the bridge from electrical to stress values was ensured by the piezoresistive relations and, prior to further in-house calibration, coefficients from literature were employed. For correlation purpose, numerical simulations were performed in order to evaluate stresses induced by TSV (Through Silicon Via). In this paper, the whole framework is described, and stress fields evaluated from in-situ electrical measurements on CMOS65 rosette sensor are compared to simulated ones. Some of the ultimate targets of this work are to develop a validated framework to deeply understand TSV induced thermo-mechanical stresses and to allow design rules definitions for products reliability and transistor performances.

### Introduction

Aiming at getting more and more efficient integrated circuits (ICs), and following Moore's law, new designs and new processes emerge. However, this race to performance and downscaling leads to higher stresses into the products [1]. Among other causes, these stresses are due to the CTE (Coefficient of Thermal Expansion) mismatch of materials, high temperature and off equilibrium deposit. Dedicated strategies to lower stresses within the chips are employed to face these concerns and various evaluation techniques were developed [2]. One method consists in embedding MOS sensors into chips. Several works were carried out to evaluate the impact of different technological bricks such as underfilling, copper pillar bumping, wire bonding and TSV assembly [3, 4] on the performance of ICs. The present paper focuses on the methodology to determine stresses induced by the TSV process in a CMOS65 technology node by using piezoresistive rosette sensors. As a reminder, the number "65" stands for the length (in nm) of the MOS gate.

The relations between the piezoresistive coefficients, the drain current variation measured on samples with and without TSV, and the stress variation enable evaluating the impact of TSV. Simulation is also performed to evaluate numerically the stress induced by TSV. Finally, numerical and experimental results are compared and discussed.

#### Piezoresisitive stress sensor formalism

Piezoresistivity formalism describes the change in the electrical resistivity while mechanical stress is applied. This effect particularly occurs in semiconductor materials, making piezoresistive devices

an attractive mean for stress sensoring in the microelectronic industry. In this part, the relations describing piezoresistivity are defined and its application is presented.

## Piezoresistive relations

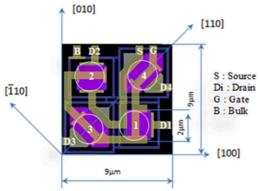

Figure 1- MOS rosette stress sensor

The MOS stress sensor (Fig. 1) is made up of four transistors in which channels are oriented in different directions. As is always the case, MOS are made into the silicon, stress field is hence evaluated in a thin region of the chip, near the rosette. A tensor relation comes from the material properties and the "theory of piezoresistivity". According to this theory, the resistivity variation  $\Delta \rho$ , as well as the resistance ( $\Delta R$ ) and the drain current  $(\Delta I_{DS})$  variations, is related to the applied stress by the relation [5]:  $\frac{\Delta R}{R} = -\frac{\Delta I_{DS}}{I_{DS}} = \frac{\Delta \rho}{\rho} = \pi \Delta \sigma$

$$\frac{\Delta R}{R} = -\frac{\Delta I_{DS}}{I_{DS}} = \frac{\Delta \rho}{\rho} = \pi \Delta \sigma \tag{1}$$

with  $\pi$  the tensor of piezoresistive coefficients and  $\Delta \sigma$  the applied mechanical stress tensor. For the silicon cubic crystal, the three independent coefficients  $(\pi_{11},\pi_{12})$  and  $\pi_{44}$  are written in a shortened matrix (6x6) form, in ([100], [010], [001]) coordinate system (Eq. 2).

$$[\pi] = \begin{bmatrix} \pi_{11} & \pi_{12} & \pi_{12} & 0 & 0 & 0 \\ \pi_{12} & \pi_{11} & \pi_{12} & 0 & 0 & 0 \\ \pi_{12} & \pi_{12} & \pi_{11} & 0 & 0 & 0 \\ 0 & 0 & 0 & \pi_{44} & 0 & 0 \\ 0 & 0 & 0 & 0 & \pi_{44} & 0 \\ 0 & 0 & 0 & 0 & 0 & \pi_{44} \end{bmatrix} .$$

(2)

The tensor  $\frac{\Delta \rho}{\rho}$  (respectively the tensors  $\frac{\Delta R}{R}$  and  $\frac{\Delta I_{DS}}{I_{DS}}$ ) is built from scalar measurements of resistivity (respectively of resistance and drain current) in different directions.

Note that the resistance variation is often preferred for passive serpentines or doped active sensors ([3, 4]). In our transistor based ones, the drain current variation is rather used.

## Stress determination

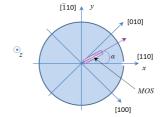

Thus, it is possible to evaluate stresses within a device thanks to electrical measurements. Two types of wafer are commonly used for chip manufacturing in the microelectronic industry: the socalled rotated and not rotated wafers. For a rotated or <100> wafer, the x axis (respectively y axis) corresponds to the [100] (respectively [010]) direction (Fig. 2). For a not rotated or <110> wafer, the x axis (respectively y axis) corresponds to the [110] (respectively [ $\bar{1}$ 10]) direction (Fig. 3). So, for a <110> wafer, the coordinate system transformation (rotation of 45° around the z axis) of  $[\pi]$ leads to the following piezoresistive coefficients matrix (Eq. 3):

$$[\pi'_{45^{\circ}}] = \begin{bmatrix} \frac{1}{2}(\pi_{11} + \pi_{12} + \pi_{44}) & \frac{1}{2}(\pi_{11} + \pi_{12} - \pi_{44}) & \pi_{12} & 0 & 0 & 0\\ \frac{1}{2}(\pi_{11} + \pi_{12} - \pi_{44}) & \frac{1}{2}(\pi_{11} + \pi_{12} + \pi_{44}) & \pi_{12} & 0 & 0 & 0\\ \pi_{12} & \pi_{12} & \pi_{11} & 0 & 0 & 0\\ 0 & 0 & 0 & \pi_{44} & 0 & 0\\ 0 & 0 & 0 & 0 & \pi_{44} & 0\\ 0 & 0 & 0 & 0 & 0 & \pi_{11} - \pi_{12} \end{bmatrix} .$$

(3)

Figure 2- Stress coordinate system for <100> wafer

Figure 3- Stress coordinate system for a <110> wafer

$\alpha$  is the angle between the MOS channel axis and the *x* axis. By combining equations Eq. 1, Eq. 2 and Eq. 3, one can write:

$$\begin{cases} a_{1}\sigma_{xx} + b_{1}\sigma_{yy} + c_{1}\sigma_{zz} + d_{1}\sigma_{xy} = -\frac{\Delta I_{d1}}{I_{d1}^{0}} & (\alpha = 0^{\circ}) \\ a_{2}\sigma_{xx} + b_{2}\sigma_{yy} + c_{2}\sigma_{zz} + d_{2}\sigma_{xy} = -\frac{\Delta I_{d2}}{I_{d2}^{0}} & (\alpha = 90^{\circ}) \\ a_{3}\sigma_{xx} + b_{3}\sigma_{yy} + c_{3}\sigma_{zz} + d_{3}\sigma_{xy} = -\frac{\Delta I_{d3}}{I_{d3}^{0}} & (\alpha = 45^{\circ}) \end{cases},$$

$$(4)$$

$$a_{4}\sigma_{xx} + b_{4}\sigma_{yy} + c_{4}\sigma_{zz} + d_{4}\sigma_{xy} = -\frac{\Delta I_{d4}}{I_{d4}^{0}} & (\alpha = -45^{\circ})$$

with  $a_i$ ,  $b_i$ ,  $c_i$  and  $d_i$ , the coefficients defined in Appendix for each wafer type.

$\Delta I_{di}$  is the drain current variation measured in the transistor number *i* of the rosette (see Fig. 1),  $I_{di}^0$  being the nominal value. The above relations are similar for n-MOS and p-MOS, since only the piezoresistive coefficients are distinct for electron and hole carriers.

## TSV induced stress analysis

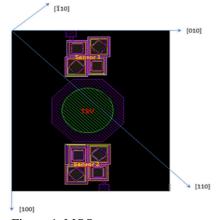

## Test vehicle, description and sensors location

In this part, MOS rosette sensors, of both n and p types were used to evaluate the stress induced by the TSV. Two types of CMOS65 samples were manufactured: a wafer with TSVs and a one without TSVs. Note that designs are similar, and the presence of TSVs is managed by process routes: one sample followed the whole flow, whereas the other skipped the TSVs related steps. As shown in Fig. 4, the sensors were embedded into the wafers near the TSVs (i.e. at  $12\mu m$  away from the center of the TSVs). Their size is given in Fig. 1. Electrical measurements from the two wafers were subtracted to evaluate the sole effect of the TSV.

Figure 4- MOS rosette stress sensor and TSV location in test vehicle

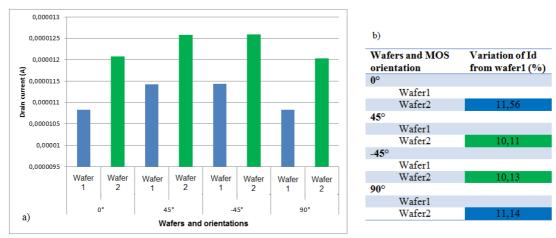

Drain currents variations were measured on the aforementioned two wafers and the difference should correspond to the impact of TSV. The evaluation of stresses components requires four equations. As, there are four n-MOS and four p-MOS, two configurations were considered: two p-MOS oriented at 0° and 90° and two n-MOS at 45° and -45° (config1), or two n-MOS at  $0^{\circ}$  and  $90^{\circ}$  and two p-MOS at  $45^{\circ}$  and  $-45^{\circ}$  (config2). As an alternative to our own four points bending calibration, which is planned to be carried out later on, piezoresistive coefficients taken from the literature [5] were used for this study. Results of the direct calculation of stresses from Eq. 4, for the two configurations are presented in Table 1-b. However, preliminary internal studies showed that, independently to any stress variation, the current values of transistors are not the same between two similar wafers: this is related to the intrinsic variability of the CMOS process (Fig. 5-a).

Figure 5- Representative diagram of process variability

#### Stress identification

So, in order to get only the TSV contribution, measurements were averaged and an optimization calculation was performed. Since the sensors provide a limited amount of equations and considering the whole unknowns of the system to solve, some assumptions had to be made: the drain currents for the process variability in [100] (0°) (respectively in [110] (45°)) direction are found to be the same as in [010] (90°) (respectively in  $[\bar{1}10]$  (-45°)) direction (Fig. 5-b). The simplified system is then expressed by (Eq. 5):

$$\begin{cases} a_{1}\sigma_{xx} + b_{1}\sigma_{yy} + c_{1}\sigma_{zz} + d_{1}\sigma_{xy} = -\frac{\Delta I_{d1}}{I_{d1}^{0}} + \frac{\Delta I_{dv1}}{I_{dv1}^{0}} \\ a_{2}\sigma_{xx} + b_{2}\sigma_{yy} + c_{2}\sigma_{zz} + d_{2}\sigma_{xy} = -\frac{\Delta I_{d2}}{I_{d2}^{0}} + \frac{\Delta I_{dv1}}{I_{dv1}^{0}} \\ a_{3}\sigma_{xx} + b_{3}\sigma_{yy} + c_{3}\sigma_{zz} + d_{3}\sigma_{xy} = -\frac{\Delta I_{d3}}{I_{d3}^{0}} + \frac{\Delta I_{dv3}}{I_{dv3}^{0}} \\ a_{4}\sigma_{xx} + b_{4}\sigma_{yy} + c_{4}\sigma_{zz} + d_{4}\sigma_{xy} = -\frac{\Delta I_{d4}}{I_{d4}^{0}} + \frac{\Delta I_{dv3}}{I_{dv3}^{0}} \end{cases}$$

(5)

with  $\Delta I_{dvi}$  the drain current variation related to process variability in the transistor number i of the rosette (see Fig. 1) and  $I_{dvi}^0$  its nominal value. For this work, the so-called evolutionary optimization excel solver was used. This class of optimization method is particularly well adapted for avoiding local minima [6]. Based on the system of equations (Eq. 5), a global cost function is built as the sum of the cost functions associated with each equation. By minimizing this global cost function, a set of stress values is found. The optimization initial conditions, boundaries and the results are summarized in the following table (Table 1-a):

Table 1- a) Table summarizing the initial conditions, boundaries and results from optimization, b) direct calculation

| a)                                | Initial<br>values<br>[MPa] | Lower<br>limits<br>[MPa] | Upper<br>limits<br>[MPa] | Obtained<br>values<br>[MPa] | b)               | Stress values<br>[MPa]<br>config1 | Stress values<br>[MPa]<br>config2 |

|-----------------------------------|----------------------------|--------------------------|--------------------------|-----------------------------|------------------|-----------------------------------|-----------------------------------|

| $\sigma_{xx}$                     | 75                         | -100                     | 100                      | 66                          | $\sigma_{xx}$    | 19                                | 95                                |

| $\sigma_{yy}$                     | -75                        | -100                     | 100                      | -23                         | $\sigma_{ m vv}$ | -51                               | 6                                 |

| $\sigma_{zz}$                     | -25                        | -100                     | 100                      | -13                         | $\sigma_{zz}$    | -51                               | -109                              |

| $\sigma_{xy}$                     | 25                         | -50                      | 50                       | -5                          |                  |                                   |                                   |

| Cost function (% of ld variation) |                            |                          |                          | 0,01306                     | $\sigma_{ m xy}$ | 0,3                               | <b>-</b> 7                        |

The comparison of these results shows that the whole methodologies do not give similar stress fields, which is not suitable. Considering the direct approach (Table 1-b), differences between configurations 1 and 2 would be attributed to piezoresistive coefficients inaccuracy and also to the fact that process variability is neglected. Hence, this method cannot be used as it and four point bending calibration is mandatory. As a consequence, it is needed to include the process variability and the measurements from the eight MOS in the equation system: the optimization method (Table

1-a) should then provide more relevant estimation of the stress fields, with an estimate error of 7MPa:

$\sigma_{xx}$  = 66 MPa;  $\sigma_{yy}$  = -23 MPa;  $\sigma_{zz}$  = -13 MPa;  $\sigma_{xy}$  = -5 MPa.

#### TSV stress 3D simulation

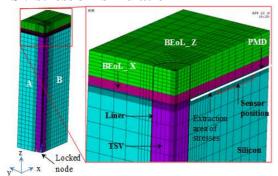

Figure 6- One fourth of the meshed model

This section deals with the numerical evaluation of stress fields induced by an isolated TSV in the silicon. Finite element numerical simulations were performed with and without TSV using the ANSYS 14.5.R finite elements software. The copper TSV has a diameter of  $10\mu m$  and a height of  $80\mu m$ . The silicon oxide liner surrounding TSV has a thickness of  $0.2\mu m$  and a height of  $80\mu m$ . The model is  $48\mu m$  long and  $40\mu m$  wide. The PMD (Pre-Metal Dielectric), the low-k and the  $SiO_2$  based interconnects have respectively thicknesses of  $0.4\mu m$ ,  $1.67\mu m$  and  $4.74\mu m$ .

Figure 7- Stress induced by TSV, experimental and numerical results

Due to geometrical symmetries, only one fourth of the stack was modeled (Fig. 6). Hexahedral quadratic elements (20 nodes) were used. Regarding boundary conditions, the node (x=0, y=0, z=0) was locked and the normal displacements of the areas A, B and the bottom base (z=0) were set to zero. The loading condition was a thermal cooling from stress free temperature (i.e. 260°C) [7] to room temperature. No material property variation during cooling was also assumed. Materials were considered as isotropic and perfect adhesion of the model interfaces was assumed. Hence, simulations were performed under linear elastic hypothesis. The interconnects being patterned layers, analysis of the designed metal densities of the homogenized BEoL showed composition of 70% copper and 30% dielectrics.

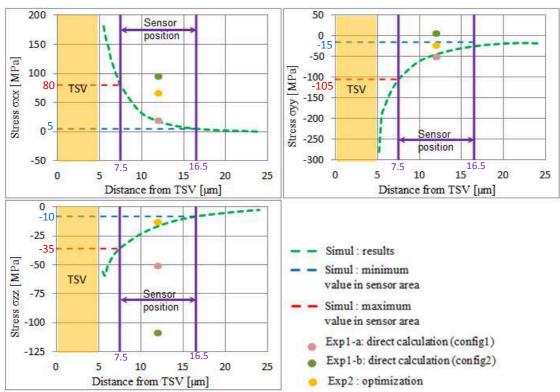

The stress values were extracted along the x axis (for  $z=79.6\mu$ m) as shown in Fig. 6. The stresses induced by TSV were obtained by subtracting stress fields from the model with TSV and those from the model without TSV. Stress variations are plotted in Fig. 7. One can note that, in the silicon material, TSV induces tensile stresses ( $\sigma_{xx}$ ) in the radial (x axis) direction, whereas in tangential (y

axis) and vertical (z axis) directions ( $\sigma_{yy}$ ,  $\sigma_{zz}$ ), the stresses are compressive. As expected, stresses decrease and tend to zero as one moves from the center of the TSV to the model boundaries. According to the position of the sensor (from  $x=7.5\mu m$  to  $x=16.5\mu m$ ), the stress variation, i.e. the difference between maximum and minimum values, is quite large ( $\Delta\sigma_{xx}$  =-75MPa,  $\Delta\sigma_{yy}$  =+90MPa and  $\Delta\sigma_{zz}$  =+25MPa). Hence, the comparison between sensor size and simulated stress fields shows that the accuracy of such sensor is likely to be weak. Averaged simulated stresses values and their variations in the sensor region are:  $\bar{\sigma}_{xx}\approx 42.5MPa\pm 37.5$ ,  $\bar{\sigma}_{yy}\approx -45MPa\pm 60$  and  $\bar{\sigma}_{zz}\approx -12.5MPa\pm 22.5$ . According to Fig. 7, the stress values (except  $\sigma_{zz}$ ) obtained from direct calculation for the first configuration are in the range of stresses obtained by simulation in the sensor area:  $\sigma_{xx} \in [5MPa, 80MPa]$ ,  $\sigma_{yy} \in [-105MPa, -15MPa]$  and  $\sigma_{zz} \in [-35MPa, -10MPa]$ . But the stress values are out of the range for the second configuration. Furthermore, as mentioned before, this method cannot be used and these results must be dismissed. The technique employing the optimization flow seems to be

relevant by taking into account the process variability. However, it is difficult at this stage to confirm stress values calculated from experiments since the exact piezoresistive coefficients for the

#### Conclusion

MOS sensors have not yet been calibrated.

For the purpose of evaluating the stress induced by TSV, MOS rosette stress sensors were used, and the results are reported in this work. Experimental investigations were based on the direct calculation of stresses from electrical measurements data and literature piezoresistive coefficients which gave different values. This is in part related to process variability which led to the use of an optimization calculation in order to get only the TSV contribution. A finite element approach was also adopted to evaluate numerically the stresses induced by TSV. The stress values obtained from the optimization are in the range of stresses obtained by simulation in the sensor area. It can be stated that the methodology is relevant, but the results will be confirmed by extracting the true piezoresistive coefficients for the embedded MOS. Once calibration performed, the piezoresistive coefficients should enable getting more accurate stress values. This calibration will be achieved by performing electrical measurements on sensors embedded into a sample subjected to a uniform uniaxial mechanical stress. A specific four point bending tool is designed for this work. At this stage, the quite good agreement between numerical and experimental results seems promising. Pros and cons of such sensors allow determining a reliable work flow for stress probing. This should enable to provide further design and integration recommendations.

#### **Appendix**

$$\begin{split} & <\mathbf{100} > \mathbf{wafer} \colon a_1 = \pi_{11}; \ a_2 = \pi_{12}; \ a_3 = \frac{1}{2}(\pi_{11} + \pi_{12}); \ a_4 = \frac{1}{2}(\pi_{11} + \pi_{12}); \ b_1 = \pi_{12}; \ b_2 = \pi_{11}; \\ b_3 = \frac{1}{2}(\pi_{11} + \pi_{12}); \ b_4 = \frac{1}{2}(\pi_{11} + \pi_{12}); \ c_1 = c_2 = c_3 = c_4 = \pi_{12}; \ d_1 = 0; \ d_2 = 0; \ d_3 = -\pi_{44}; \ d_4 = \pi_{44} \\ & <\mathbf{110} > \mathbf{wafer} \colon a_1 = \frac{1}{2}(\pi_{11} + \pi_{12} + \pi_{44}); \ a_2 = \frac{1}{2}(\pi_{11} + \pi_{12} - \pi_{44}); \ a_3 = \frac{1}{2}(\pi_{11} + \pi_{12}); \ a_4 = \frac{1}{2}(\pi_{11} +$$

#### Acknowledgments

The authors gratefully acknowledge MTM and TCAD teams of STMicroelectronics. They also acknowledge Nicolas HOTELIER and Process team, Sebastien HAENDLER and ECR team of STMicroelectronics. They appreciate the support of CEMEF, Mines ParisTech.

#### References

- [1] International Technology Roadmap for Semiconductors (ITRS), 2010.

- [2] I. De Wolf, V. Simons, V. Cherman, R. Labie, B. Vandevelde, E. Beyne and IMEC, In-depth Raman Spectroscopy Analysis of Various Parameters Affecting the Mechanical Stress near the Surface and Bulk of Cu-TSVs, IEEE, 978-1-4673-1965-2, 2012.

- [3] K. Aditya, X. Zhang, Q. X. Zhang, M. C. Jong, G. Huang, L. W. S. Vincent, C. Lee, J. H. Lau, D. L. Kwong, R. R. Tummula and G. Meyer-Berg, Residual Stress Analysis in Thin Device Wafer Using Piezoresistive Stress Sensor, IEEE Transactions on Components Packaging and Manufacturing Technology, vol. 1, p. 6, 2011.

- [4] X. Zhang, K. Aditya, Q. Zhanga, Y. Onga, S. Hoa, C. Khonga, V. Kripesha, J. Laua, D.-L. Kwonga, V. Sundaramb, R. Tummulab and G. Meyer-Berg, Application of Piezoresistive Stress Sensors in Ultra Thin Device Handling and Characterization, Sensors and Actuators A156, pp. 2-7, 2009.

- [5] C. S. Smith, Piezoresistance effect in germanium and silicon, Phys. Rev., vol. 94, pp. 42-49, 1954.

- [6] E. Roux, P-O. Bouchard, Kriging metamodel global optimization of clinching joining processes accounting for ductile damage, Journal of Materials Processing Technology, 213(7):1038-1047, 2013.

- [7] M. Gregoire, Properties of Thin Film and Copper Interconnects. Thesis in Science and Engineering of Materials. Grenoble: National Polytechnic Institute of Grenoble, 2006, 248 p.