# High Sensitivity Surface Defect Inspection of SiC and SmartSiC<sup>™</sup> Substrates Using a DUV Laser-Based System

Submitted: 2022-09-01

Revised: 2022-12-02

Online: 2023-05-31

Accepted: 2022-12-04

Enrica Cela<sup>1,a\*</sup>, Sam Shahidi<sup>2,b</sup>, Prasant Parangi<sup>2,c</sup>, Ramesh Shrestha<sup>2,d</sup>, Gavin Simpson<sup>2,e\*</sup>, Julie Widiez<sup>3,f</sup>, Nicolas Daval<sup>1,g</sup>, Audrey Chapelle<sup>1,h</sup>, Séverin Rouchier<sup>1,j</sup>, Walter Schwarzenbach<sup>1,i</sup>

<sup>1</sup>Soitec SA, Chemin des Franques, 38190 Bernin, France

<sup>2</sup>KLA+, 1 Technology Drive, Milpitas, CA USA

<sup>3</sup>CEA-LETI, 17 avenue des Martyrs, 38054 Grenoble, France

a\*enrica.cela@soitec.com, bsam.shahidi@kla.com, prasant.parangi@kla.com,

dramesh.shrestha@kla.com, gavin.simpson@kla.com, fjulie.widiez@cea.fr,

gnicolas.daval@soitec.com, haudrey.chapelle@soitec.com, jseverin.rouchier@soitec.com,

iwalter.schwarzenbach@soitec.com

\*Corresponding authors

**Keywords:** SmartSiC $^{TM}$ , Smart Cut $^{TM}$ , in-line metrology, defects inspection, DUV laser, unpatterned substrates, defects classification

**Abstract.** SmartSiC<sup>TM</sup> technology enables the supply of cost-effective and high-quality substrates to support the manufacturing of Silicon Carbide (SiC) Power Devices and the transition to High Volume Manufacturing (HVM) [1]. As detailed in [2] SmartSiC<sup>TM</sup> is prepared using a polycrystalline handle wafer, it combines the benefit from both an optimized high quality epi-ready 4H-SiC layer and an ultra high conductivity handle material. Smart Cut<sup>TM</sup> technology can be extended to SiC 200mm substrates and first SmartSiC<sup>TM</sup> 200mm sample has been prepared [2].

SmartSiC<sup>TM</sup> substrates crystal quality is inherited by donor wafers [1, 2] and do not require a systematic control, enabling a new defects monitoring strategy, focusing on surface defects.

This paper describes how a commercially available DUV inspection system was utilized for high sensitivity, high-throughput inspections of 150 and 200 mm 4H-SiC and SmartSiC<sup>TM</sup> substrates, for the HVM environment. The KLA Surfscan<sup>®</sup> SP A2 unpatterned wafer inspection system offers the opportunity to complement other inspection technologies to optimize SiC substrate defect control, with low threshold detection, below 150 nm.

# **Introduction: SmartSiC<sup>TM</sup> Defects Inspection Challenges**

4H-SiC defect characterization is crucial to guarantee the epitaxial layers' yield. The link between epitaxial layers' extended defects and devices performances has been investigated since many years [4]. Both crystallographic defects inherited from the substrate (such as Basal Plane Dislocations, Stacking Faults and Micro-Pipes) and surface defects were studied as impacting the epitaxial layers' growth. Surface defects of 4H-SiC substrates, such as particles and scratches, can act as nucleation centers for epitaxial layer crystallographic defects, and propagate to product yield-limiting defects, as triangular stacking faults [3, 5].

Production-grade SiC wafers quality control must include defect inspection, as an early, cost-effective means to control quality and final device yield.

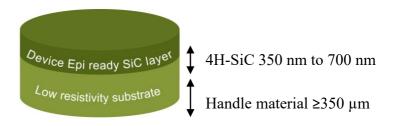

As illustrated in Fig. 1 and Fig. 2, SmartSiC<sup>TM</sup> is a bi-layer SiC engineered substrate composed of a thin layer of 4H-SiC material, ranging from 700 nm to 350 nm, transferred to a specific handle wafer.

Fig. 1.Typical SmartSiC<sup>TM</sup> stack.

Donor wafer (Prime mono-crystalline 4H-SiC)

Poly-crystalline handle wafer

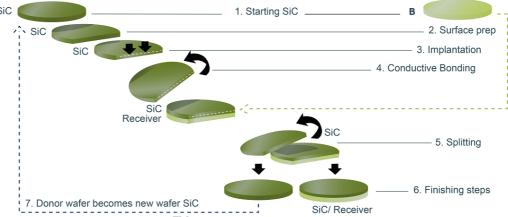

Fig. 2.Smart Cut<sup>TM</sup> process description, as adapted to SiC

Smart Cut<sup>TM</sup> technology enables replicating the high-quality crystal quality of the donor wafers, selected for their excellent grade. The same donors can be reused multiple times. Thus, SmartSiC<sup>TM</sup> requires inspection for only surface defects, similar to Silicon.

Typical inspection tools for SiC substrates include surface microscopy, laser light scattering and photoluminescence data collection, to characterize both surface and crystal defects. A lower system throughput and complex inspection setup, however, can limit the process control sampling volume of SiC wafers in a production environment. On the other hand, specific SmartSiC<sup>TM</sup> design creates the opportunity of using laser scattering-based tools designed for HVM, offering high throughput and high sensitivity.

# Influence of SiC optical properties on inspection systems performance

SiC material exhibits a very low absorption coefficient, resulting in high penetration depth and transparency on a wide portion of the light spectrum. Values reported in the literature for optical penetration depth are extremely high in the UV range (48  $\mu$ m penetration at room temperature for a 355 nm laser, 8.4  $\mu$ m at 325 nm [6]).

These material properties can cause surface defects sensitivity limitation, due to sub-surface signal, and local reflectance variation on thin layers stacks. In order to limit the influence of high penetration depth, we considered the optical behavior of SmartSiC<sup>TM</sup> substrates at 266 nm DUV wavelength.

Most of the reference values for 4H-SiC optical constants are measured in the ultraviolet range, 300 to 360 nm wavelength, commonly used for epitaxial layers characterization. In addition, as shown in [7], dopants concentration strongly influences optical properties. Therefore for our study k extinction coefficient was measured in the DUV range, below 300 nm, on a production grade 4H-SiC wafer used as donor for SmartSiC<sup>TM</sup> manufacturing (n-doped 4H-SiC with dopants concentration  $\sim 5.10^{18}$  at/cm<sup>3</sup>). We calculated the penetration depth based on the fit of n and k optical constants using a variable angle spectroscopy ellipsometer (Woollam, RC2).

At 266 nm DUV wavelength, the extinction coefficient k was measured at 5.10<sup>-2</sup>, lowering the penetration depth into 4H-SiC to 400 nm, reducing the influence of embedded and interface defects for thin layers and limiting local reflectivity variations. The leverage of limiting penetration depth helps to improve surface inspection sensitivity at this wavelength.

To overcome the technical barriers related to high 4H-SiC penetration depth in visible and UV spectral range, a DUV wavelength laser-based inspection system (KLA's Surfscan® SP A2) was used to inspect surface defects on various 4H-SiC and SmartSiC<sup>TM</sup> substrates.

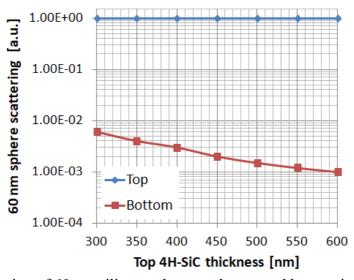

The scattering of a 60 nm silicate sphere on the top and the bottom of the top SiC layer of a SmartSiC<sup>TM</sup> stack was simulated as a function of SiC layer thickness for the Surfscan® SP A2 optical system (Fig.3). The graph is based on numerical simulation of light scattering of a sphere on top of film stack, performed based on Mie scattering theory. The signal from the bottom interface is 2 to 3 orders of magnitude less than the signal from the top surface. As a result, a DUV laser-based system can detect and segregate surface defects to achieve a sensitivity of a few tens of nanometers on a conventional 4H-SiC substrate or a SmartSiC<sup>TM</sup> stack.

Fig. 3. Simulated scattering of 60 nm silicate sphere on the top and bottom interface of the top layer of SmartSiC<sup>TM</sup> substrate.

## **DUV** inspection sensitivity

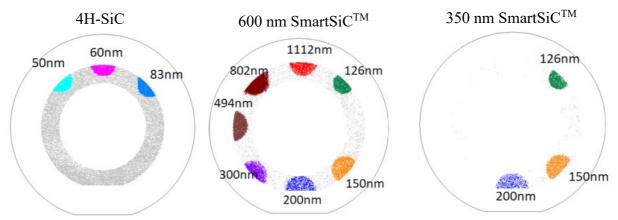

Experimental data confirmed the simulation predictions: deposited 50 nm polystyrene latex (PSL) spheres were successfully detected on a production-grade 4H-SiC substrate and 126 nm spheres were likewise detected on various SmartSiC<sup>TM</sup> stacks (Fig.4).

Fig. 4. Deposited PSL spheres detection using Surfscan® SP A2 on: conventional 4H-SiC (Left) and various SmartSiC<sup>TM</sup> stacks (Center and Right)

Moreover, these results were obtained at a throughput compatible with HVM requirements. For example 150 mm SmartSiC<sup>TM</sup> wafers were measured at 125 wafers per hour throughput.

#### **Real Defects Detection and Classification**

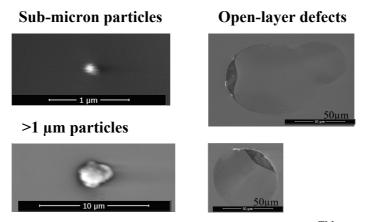

Production grade SmartSiC<sup>TM</sup> substrates, both 150 and 200 mm, were inspected in the same configuration as the wafers deposited with artificial defects, to confirm the sensitivity results on real defects. The defects coordinates issued from the DUV inspection system were reviewed using a scanning electron microscope (SEM, FEI Versa 3D). As illustrated in Fig. 5, surface particles below 300 nm were successfully detected on SmartSiC<sup>TM</sup> substrates.

Fig. 5. SEM review images gallery illustrating SmartSiC<sup>TM</sup> defect types

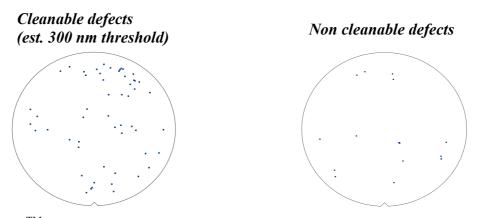

Not all SiC defects types are of equal significance from a manufacturing point of view. The ability to identify and separate "cleanable" versus "non-cleanable" defects is crucial to achieving "defect-free" substrates. Simultaneous brightfield and darkfield data collection channels were used on the Surfscan® SP A2 system to classify defects based on the optical signature. "Non-cleanable" defects showed a stronger signal on the brightfield channel, whereas "cleanable" defects are mostly detected on the darkfield channel. Based on this observation, a classification rule was established to segregate defect categories with no impact on inspection sensitivity or throughput.

Detection and classification results are illustrated in Fig. 6 for a production grade 150 mm SmartSiC<sup>TM</sup> substrate:

Fig. 6. SmartSiC<sup>TM</sup> defects detection and classification using DUV darkfield and visible brightfield inspections: maps of signal-based classification for "cleanable" (Left) and "non-cleanable" defects (Right)

To demonstrate the classification accuracy on a statistic sample of wafers, SmartSiC<sup>TM</sup> substrates were inspected using a Nomarski confocal differential interference contrast microscope (Lasertec, SICA88) and images were manually reviewed. Classification accuracy achieved is above 85%, as summarized in Table 1.

| SmartSiC <sup>TM</sup> substrates group | Total defects count (300 nm threshold) | Non-cleanable defects (classification) | Non-cleanable<br>defects (manual<br>review) | Binning accuracy |

|-----------------------------------------|----------------------------------------|----------------------------------------|---------------------------------------------|------------------|

| A                                       | 598                                    | 46                                     | 51                                          | 90%              |

|                                         | 345                                    | 0.4                                    | 86                                          | 94%              |

### Summary

In this work, a production-worthy, DUV laser-based inspection system, the Surfscan® SP A2 was used to perform high-sensitivity defect inspection on various SiC substrates. Multiple SmartSiC<sup>TM</sup> stacks were inspected at a 126 nm detection threshold. Sub-micron particles detection was confirmed on real particles and defects classification was successfully demonstrated. All the results were obtained at HVM compatible requirements on both 150 and 200 mm substrates.

SmartSiC<sup>TM</sup> technology, replicating the crystal quality of a donor wafer, allows for a new approach for defect monitoring, focusing on surface defects, similar to Silicon. This creates the opportunity of an inspection combining high sensitivity and high throughput. Unique SmartSiC<sup>TM</sup> engineered substrates coupled with well-suited inspection and metrology systems will help to drive lower manufacturing costs to enable the evolving SiC power device market.

## Acknowledgments

The SmartSiC<sup>TM</sup> wafers development has been performed in partnership with CEA-LETI as part of the Soitec and Leti's Substrate Innovation Center.

This work is supported by the H2020 - ECSEL JU programme of the European Union under the grant of the TRANSFORM project 'Trusted European SiC Value Chain for a greener Economy' (ECSEL JU Grant No. 101007237)

#### References

- [1] S. Rouchier et al., "150 mm SiC engineered substrates for high-voltage power devices", **ECSCRM 2021**

- [2] W. Schwarzenbach et al., "SmartSiC<sup>TM</sup>: Boosting SiC performance for high-voltage power applications", ICSCRM 2022

- [3] D. Baierhofer et al., Material Science in Semiconductor Processing, vol 140 (2022), 106414

- [4] T. Kimoto, Japanese Journal of Applied Physics, vol 54 (2015), 040103

- [5] H. Matsuhata et al., Microscopy (2017),pp. 103-109

- [6] S.G. Sridhara et al., Materials Science and Engineering, B61–62 (1999), pp. 229-233

- [7] R. Weingärtner et al., Materials Science and Engineering, B80 (2001), pp. 357-361