# Buffer Layer Dependence of Defectivity in 200mm 4H-SiC Homoepitaxy

Submitted: 2023-09-30

Revised: 2024-04-09

Online: 2024-08-22

Accepted: 2024-04-12

Domenica Raciti<sup>1,a\*</sup>, Ruggero Anzalone<sup>1,b</sup>, Mathias Isacson<sup>2,c</sup>, Nicolò Piluso<sup>1,d</sup> and Andrea Severino<sup>1,e</sup>

<sup>1</sup>STMicroelectronics, Stradale Primosole 50, 95100 Catania, Italy

<sup>2</sup>STMicroelectronics Silicon Carbide AB, Ramshällsvägen 15, SE-602 38 Norrköping, Sweden

<sup>a</sup>domenica.raciti@st.com, <sup>b</sup>ruggero.anzalone@st.com, <sup>c</sup>mathias.isacson@st.com, <sup>d</sup>nicolo.piluso@st.com, <sup>e</sup>andrea.severino@st.com

Keywords: 4H-SiC, homoepitaxy, Buffer Layer, defectivity

**Abstract.** The effect of increasing Buffer Layer (BL) thickness on crystal defectivity has been investigated in 4° off-axis 4H-SiC homoepitaxy on 200mm substrates coming from different suppliers. The results, based on optical microscopy and scatter light methods, show a slight increase in morphological defects in the case of a thicker BL with respect to the standard thickness for both suppliers.

#### Introduction

Owing to its excellent physical properties, the wide-bandgap semiconductor material Silicon carbide (SiC) is an ideal candidate for power electronics devices, enabling fast switching speeds, low leakage currents and high breakdown voltages compared to Silicon [1,2].

Recent years have witnessed a remarkable improvement in 4H-SiC-based device technology, thanks to the availability of large-diameter, high-quality SiC boules. Enlarging the wafer size while reducing defect density is the development tendency of 4H-SiC single-crystal substrates to reduce device costs [3]. For this reason, 200mm (8-inch) SiC substrates are now facing the market to replace the current 150mm (6-inch) technology [4,5].

Buffer layer (BL) formation is a crucial step in Chemical Vapor Deposition (CVD) processes, aimed at suppressing substrate defects (such as dislocations, particles, or stains) to increase the crystal quality of the overgrown epitaxial layer. Indeed, many defects can be highly damaging for power devices, as they increase the leakage current, alter the current-voltage relation and reduce device reliability [2,6,7]. Among other parameters, such as doping or growth rate [8], optimizing the BL thickness can help improve crystal quality in SiC epitaxy [9].

With the aim of optimizing epitaxial growth conditions, we investigated the effect of increasing buffer layer thickness on defectivity, in terms of both morphological and crystallographic defects. The study was conducted on n-doped 8-inch 4H-SiC substrates coming from two different suppliers.

# Method

**Growth.** N-doped epitaxial SiC layers were grown on the Si-face (0001) of 200mm 4H-SiC substrates with 4° off axis on the (11 $\overline{2}0$ ) face, coming from two different suppliers (here denoted as A and B). Growth experiments were carried out in a commercial low-pressure, hot-wall single-wafer CVD reactor based on a trichlorosilane (SiHCl<sub>3</sub>) – ethylene (C<sub>2</sub>H<sub>4</sub>) chemistry, using a Nitrogen-based dopant and Hydrogen as carrier gas. The epitaxial step was carried out at a temperature of about 1650°C with C/Si ratio around 1. The buffer layer doping concentration was ~10<sup>18</sup> at/cm<sup>3</sup>, while the epitaxial layer was grown at ~10<sup>16</sup> at/cm<sup>3</sup>. All the substrates, characterized by ultra-low micropipe density, were epi-ready polished on the Si face and freshly cleaned prior to the growth.

The defects distribution on the epitaxial layer was investigated for two BL thicknesses: the so-called thin-BL samples were grown with the standard thickness used for commercial purposes, while thick-BL samples by doubling the BL deposition time (and hence the BL thickness), while keeping all the other growth parameters constant. The experiments were carried out to ensure that each thin-

BL vs thick-BL wafer couple eligible for comparison would come from closely related substrates with comparable crystal quality, grown in consecutive CVD runs.

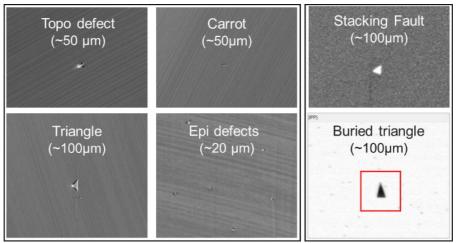

Characterisation. The defectivity characterisation was mainly conducted using a Candela® tool from KLA-Tencor. The tool, based on scattered light method at different laser incident angles and equipped with a photoluminescence channel, enables monitoring of both crystallographic and morphological defects with high spatial resolution and sensitivity. An example of typical post-epi defects detected by Candela is given in Fig.1, the characteristic sizes being reported within parentheses.

Wafer defectivity was further monitored via Bright-Field optical microscopy, using a KLA Altair® tool. The method, sensitive to morphological defects only, allows to validate the distinction between crystallographic and morphological defects made based on the Candela inspection.

Control measurements of thickness and doping concentration profiles were performed via FT-IR and Hg-probe Capacitance Voltage, respectively (data not shown). No correlation was observed between the thickness or doping profiles and the BL thickness or the observed defectivity patterns.

**Fig. 1.** Examples of typical post-epitaxy defects on 4H-SiC samples, as detected by KLA Candela, and their characteristic sizes. *Left panel*: surface morphological defects, detected exploiting the normal/oblique scatter intensity. *Right panel*: bulk crystallographic defects, detected via visible or near-UV photoluminescence (PL). Notice that the scales differ from one image to another for visualization purposes; the characteristic size of each defect is reported inside parentheses.

### **Results**

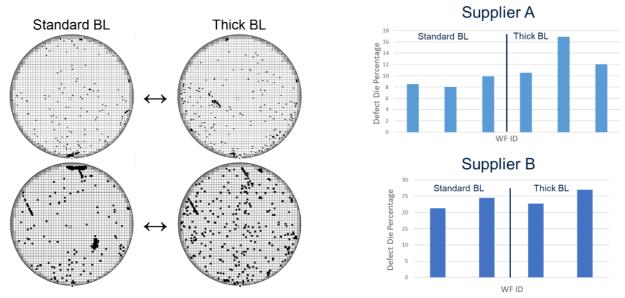

**Bright-Field optical microscopy (KLA Altair®).** As an example, Fig. 2, *left* shows the morphological (Altair) defect distribution maps for two couples (thin-BL vs thick-BL) of samples, each coming from closely related substrates from the same supplier with comparable crystal quality, grown in consecutive CVD runs. Fig. 2, *right* shows the trend of morphological defect die percentages of thin-BL vs thick-BL epitaxies for the two suppliers. In all cases the wafer defectivity is higher in the thick-BL samples.

**Fig. 2.** *Left*: Examples of morphological defect distribution maps (die size:5x5mm), detected by Altair, relative to two couples of samples from Supplier A (thin-BL vs thick-BL). *Right*: Defect die percentages as estimated from Altair maps, relative to sample couples (thin-BL vs thick-BL, to be read in order of wafer ID) obtained from two different suppliers, denoted as A and B. Each couple comes from closely related substrates with comparable crystal quality, grown in consecutive CVD runs (differing only in the BL deposition time).

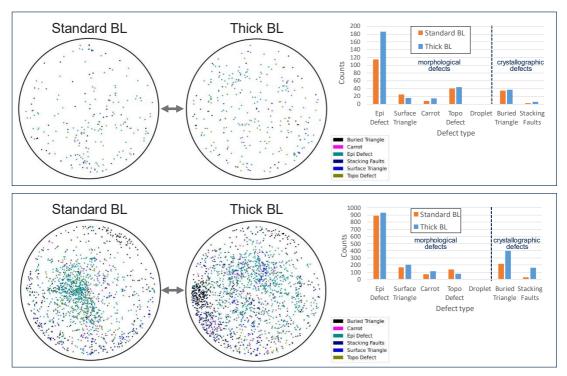

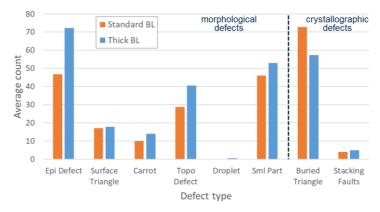

Scattered light method (KLA Candela®). Fig. 3 reports, as an example, the Candela inspection results relative to two thin-BL/thick-BL wafer couples from the two substrate suppliers (top panel: supplier A; bottom panel: supplier B). For each couple, the image shows the defect distribution maps of the two wafers, as well as the relative defect counts per defect type. The diagram in Fig. 4 reports the average defect counts observed in the thin-BL (orange) vs thick-BL (blue) wafer couples from Supplier A (5 couples), sorted by defect type. Defect types have been further grouped into morphological (detected by scatter light) and crystallographic (detected by photoluminescence) defects. Despite the limited statistics (5 wafer couples), the results seem to suggest an increase in surface morphological defects in the case of a thicker BL with respect to the standard value. The trend has been observed in all wafer couples for all defect types, except for surface triangles (see Fig. 4), where the averages are comparable for the two BL thicknesses. For crystallographic defects, the observed trend is variable.

**Fig. 3.** Examples of Candela inspections on two thin-BL vs thick-BL wafer couples. *Top panel*: couple of samples from supplier A; *bottom panel*: couple of samples from supplier B. Each panel reports on the left the defect distribution maps of the thin-BL and thick-BL samples with their respective color legend; the diagram on the right reports the defect count in the two samples (orange: thin BL, blue: thick BL) sorted by defect type, defect types being grouped as morphological or crystallographic based on the detection channels (the latter are detected via the photoluminescence channel).

**Fig. 4.** Average defect counts observed in the thin-BL (orange) vs thick-BL (blue) wafer couples from Supplier A (5 couples) sorted by defect types being grouped as morphological or crystallographic based on the detection channels (the latter are detected via the photoluminescence channel).

## Conclusion

In this study, aimed at optimizing the epitaxial growth conditions on n-doped, 200mm 4H-SiC substrates, we investigated the impact of increasing buffer layer thickness on the crystal quality of the drift layer, in terms of both morphological and crystallographic defects. The study was conducted on substrates coming from two different suppliers (A and B).

The study is part of a larger evaluation campaign on 200mm epitaxy that is still ongoing. Albeit preliminary, our results suggest a dependence of crystal quality on the buffer layer thickness, as observed for both suppliers in repeated experiments. In particular, the data show an increase in morphological defects in the case of a thicker BL with respect to the standard thickness, as emerging from

both optical microscopy (Altair) and scatter light (Candela) measurements. The trend is more evident in supplier A due to better crystal quality (also meaning a lower defect variability).

More experiments have been planned to improve the statistics on supplier B and to better understand the impact of BL thickness on crystallographic defects, as well as on the electrical performance of the final devices.

#### References

- [1] S.E. Saddow, A.K. Agarwal, Advances in silicon carbide processing and applications, Artech House, Boston, 2004.

- [2] T. Kimoto, J. A. Cooper, Fundamentals of Silicon Carbide Technology, Wiley, Hoboken, 2014.

- [3] St.G. Muller, R.C. Glass, H.M. Hobgood, V.F. Tsvetkov, M. Brady, D. Henshall, J.R. Jenny, D. Malta, C.H. Carter Jr., The status of SiC bulk growth from an industrial point of view, *J. Cryst. Growth* 211 (2000) 325–332.

- [4] S. Parthasarathy, Shifting to 200 mm silicon carbide, *Compound Semiconductor*, Vol. 27 issue 7 (2021).

- [5] M. Musolino, X. Xu, H. Wang, V. Rengarajan, I. Zwieback, G. Ruland, D. Crippa, M. Mauceri, M. Calabretta, A. Messina, Paving the way toward the world's first 200mm SiC pilot line, *Mater. Sci. Semicond. Process.* 135 (2021) 106088.

- [6] H. Das, S. Sunkari, J. Justice, H. Pham, G. Park, Y.H. Seo, Statistical analysis of killer and non-killer defects in SiC and the impacts to device performance, *Mater. Sci. Forum* 1004 (2020), pp. 458-463.

- [7] K. Nakayama, A. Tanaka, K. Asano, T. Miyazawa, H. Tsuchida, Influence of in-Grown Stacking Faults on Electrical Characteristics of 4H-SiC Pin Diode with Long Carrier Lifetime, *Mater. Sci. Forum* 740-742 (2013), pp. 903-906.

- [8] T. Rana, J. Wu, G. Chung, K. Moeggenborg, M. Gave, Study of Defects in 4H-SiC Epitaxy at Various Buffer Layer Growth Conditions, *Defect Diffus. Forum* 425 (2023), pp. 63-68.

- [9] N. Piluso, A. Severino, R. Anzalone, M.A. Di Stefano, E. Fontana, M. Salanitri, S. Lorenti, A. Campione, P. Fiorenza, F. La Via, Growth of 4H-SiC epitaxial layer through optimization of buffer layer, *Mater. Sci. Forum* 924 (2018), pp. 84-87.