# SiC MOSFET Gate Oxide Quality Improvement Method in Furnace Thermal Oxidation with Lower Pressure Control

Submitted: 2023-09-07

Revised: 2024-04-15

Online: 2024-08-22

Accepted: 2024-04-15

Youngbin Im<sup>a\*</sup>, Inkyu Kim<sup>b\*</sup>, Seongpil Son<sup>c\*</sup>, Youngkwon Kang<sup>d</sup>, Chungjung Kim<sup>e</sup>, Junhyoung Lee<sup>f</sup>, Jungho Lee<sup>g</sup>, Jesung Lim<sup>j</sup> and Changbeom Jeong<sup>i</sup>

ONSEMI, 55 Pyeongcheon-ro 850beon-gil Bucheon-si Gyeonggi-do, Republic of Korea

<sup>a\*</sup>youngbin.im@onsemi.com, <sup>b\*</sup>inkyu.kim@onsemi.com, <sup>c</sup>seongpil.son@onsemi.com, <sup>d</sup>youngkwon.kang@onsemi.com, <sup>e</sup>chungjung.kim@onsemi.com, <sup>f</sup>Junhyoung.lee@onsemi.com, <sup>g</sup>jungho.lee@onsemi.com, <sup>j</sup>jesung.lim@onsemi.com, <sup>i</sup>chang.jeong@onsemi.com

**Keywords:** SiC thermal oxidation, SiO<sub>2</sub>/SiC interface carbon reduction, lower pressure oxidation, interface carbon defect, carbon in oxide

**Abstract.** We have investigated carbon behavior resulting from pressure control in furnace thermal oxidation process and evaluated the effect on gate oxide quality resulting from this pressure control. In order to investigate the potential reduction of carbon defects by reducing CO and CO<sub>2</sub>, an analysis of oxidized SiC wafers was conducted. To evaluate the effect of pressure control related carbon component change during thermal oxidation, Q<sub>BD</sub> characteristic was evaluated in SiC MOS Capacitance. The analysis results revealed on observable decrease in carbon at the SiO<sub>2</sub>/SiC interface and the SiO<sub>2</sub> layer. The Q<sub>BD</sub> results shown that improved at lower pressure better than those obtained in the general pressure.

## Introduction

The gate oxide is an insulating layer that separates the gate terminal from the channel of a MOSFET(metal-oxide-semiconductor field-effect transistor). It is responsible for controlling the flow of current through the channel, and thus plays a key role in determining the device's electrical characteristics such as its on-state resistance and switching speed. Overall, gate oxide integrity is a crucial factor in the performance and reliability of SiC MOSFETs, and it requires careful attention and expertise to ensure that it meets the high standards required for power electronics applications. Numerous research findings have been reported regarding the reduction of carbon related defect at the interface between the oxide and SiC to achieve better gate oxide quality in SiC MOSFET [1]. In this paper, we will verify carbon behavior from pressure control in furnace thermal oxidation process and evaluate the effect to gate oxide quality from this pressure control.

# **Results and Discussion**

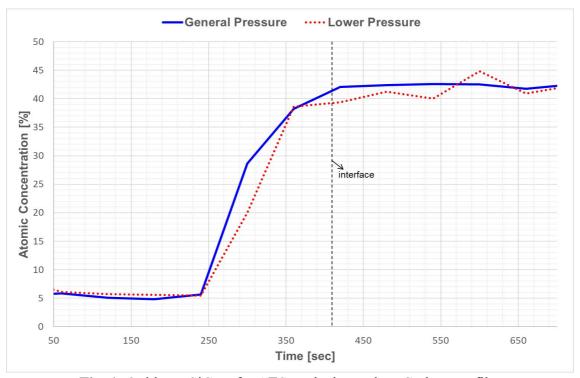

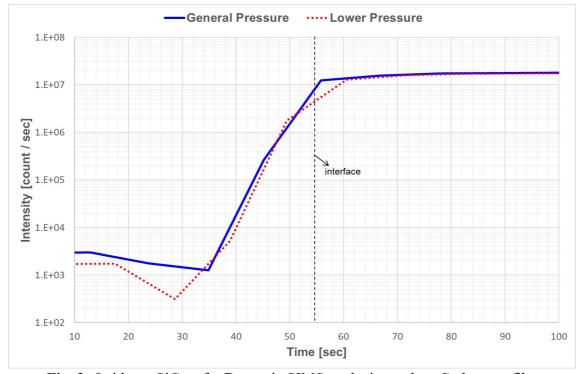

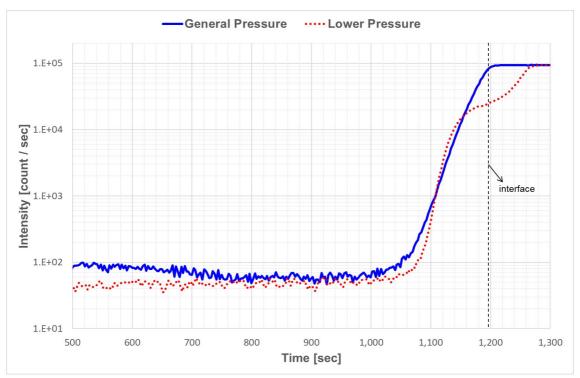

According to the kinetic model of SiC oxidation based on the interfacial silicon and carbon emission phenomenon, during SiC oxidation, the encounter between SiC and O<sub>2</sub> leads to the formation of SiO<sub>2</sub>, C, CO<sub>2</sub> and CO [2-5]. These formed molecules of CO<sub>2</sub> and CO can react with SiO<sub>2</sub> [6]. In order to investigate the potential reduction of carbon defects by reducing CO and CO<sub>2</sub>, an analysis of oxidized SiC wafers was conducted. SiC wafers were proceeded furnace thermal oxidation, while controlling the pressure to facilitate rapid removal of CO and CO<sub>2</sub>. To ensure accurate comparisons, the analysis was performed using AES, Dynamic SIMS, and TOF-SIMS techniques, with a specific focus on examining the behavior of carbon. The analysis results AES in (Fig. 1), Dynamic SIMS in (Fig. 2) and TOF-SIMS in (Fig. 3), revealed observable changes in the

SiO<sub>2</sub>/SiC interface and carbon content within the SiO<sub>2</sub> layer. Each analyst observed that carbon was reduced from the SiC interface of the wafer that had undergone lower pressure oxidation. It could be possible that by applying lower pressure to increase the gas flow speed within the furnace, rapid removal of CO and CO<sub>2</sub> was achieved, thereby reducing the subsequent reaction with SiO<sub>2</sub>. Consequently, this reduction in reactivity led to a decrease in the carbon content at the interface and within the oxide layer.

Fig. 1. Oxide on SiC wafer AES analysis results - Carbon profile.

Fig. 2. Oxide on SiC wafer Dynamic SIMS analysis results - Carbon profile.

Fig. 3. Oxide on SiC wafer TOF-SIMS analysis results - Carbon profile.

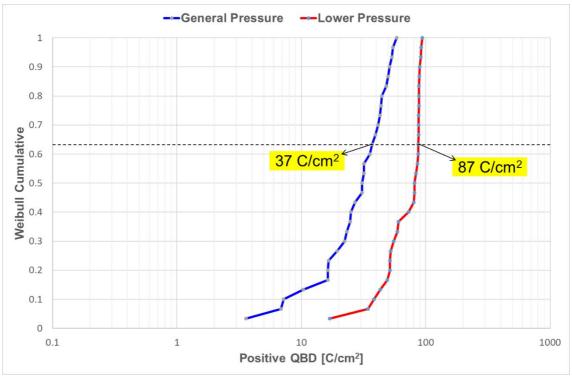

The  $Q_{BD}$  is a standard destructive test method to verify the gate oxide quality in MOS devices. To evaluate effect of pressure control related carbon component change during thermal oxidation,  $Q_{BD}$  characteristic is evaluated. SiC MOS Capacitance  $Q_{BD}$  measured, then compared by Weibull plot. As shown in (Fig. 4), we obtained  $Q_{BD}$  results that improved at lower pressure (87 C/cm<sup>2</sup>) better than those obtained in the general pressure (37 C/cm<sup>2</sup>).

**Fig. 4.** Q<sub>BD</sub> Weibull plot of general pressure and lower pressure. SiC MOS Capacitance charge to breakdown Q<sub>BD</sub>, Istress=20mA/cm<sup>2</sup>, Tstress=25°C.

Therefore, the results from analysis have revealed that pressure difference during oxidation can support forming less Carbon defects in  $SiO_2$  layer and this effect is related with better  $Q_{BD}$  characteristic shown thermal oxidation process.

# **Summary**

In summary, we verified carbon behavior from pressure control in furnace thermal oxidation process. It could be possible that by applying lower pressure to increase the gas flow speed within the furnace, rapid removal of CO and CO<sub>2</sub> was achieved, thereby reducing the subsequent reaction with SiO<sub>2</sub>. The lower pressure thermal oxidation proceeded oxidized SiC wafer SIMS analysis results revealed observable Carbon decrease in the SiO<sub>2</sub>/SiC interface and SiO<sub>2</sub> layer. As this effect, SiC NMOS Capacitance, which is proceeded lower pressure thermal oxidation, shown improved Q<sub>BD</sub> results more than double. Therefore, lower pressure during furnace thermal oxidation can generate less Carbon in SiO<sub>2</sub> and SiO<sub>2</sub>/SiC interface, and this effect improves SiC MOSFET gate oxide quality as shown Q<sub>BD</sub> improvement results.

### References

- [1] Maria Cabello, Victor Soler, Gemma Rius, Josep Montserrat, Jose Rebollo, Philippe Godignon, Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review, Materials Science in Semiconductor Processing 78 (2018) 22-31.

- [2] Yasuto Hijikata, Hiroyuki Yaguchi, Sadafumi Yoshida, A Kinetic Model of Silicon Carbide Oxidation Based on the Interfacial Silicon and Carbon Emission Phenomenon, Applied Physics Express 2 (2009) 021203.

- [3] Toru Akiyama, Ayako Ito, Kohji Nakamura, Tomonori Ito, Hiroyuki Kageshima, Masashi Uematsu, Kenji Shiraishi, First-principles investigations for oxidation reaction processes at 4H-SiC/SiO<sub>2</sub>, Surface Science 641 (2015) 174-179.

- [4] Nicolas Biscay, Lucile Henry, Tadafumi Adschiri, Masahiro Yoshimura, Cyril Aymonier, Behavior of Silicon Carbide Materials under Dry to Hydrothermal Conditions, Nanomaterials 2021, 11, 1351.

- [5] Shiyan Chen, Yi Zeng, Xiang Xiong, Huilin Lun, Ziming Ye, Tiansing Jiang, Lingwei Yang, Jun Zhang, Liping Liu, Guolin Wang, Li Jing, Xianqian Xie, Changhai Yan, Static and dynamic oxidation behaviour of silicon carbide at high temperature, Journal of the European Ceramic Society 41 (2021) 5445-5456.

- [6] Kenta Chokawa, Masaaki Araidai, Kenji Shiraishi, Effects of annealing with CO and CO<sub>2</sub> molecules on oxygen vacancy defect density in amorphous SiO<sub>2</sub> formed by thermal oxidation of SiC, J. Appl. Phys. 124, 135701 (2018).