# Crystal Originated Defect Monitoring and Reduction in Production Grade SmartSiC<sup>™</sup> Engineered Substrates

Submitted: 2023-09-07

Revised: 2024-05-23

Online: 2024-08-22

Accepted: 2024-05-27

Enrica Cela<sup>1,a\*</sup>, Kassem Alassaad<sup>1,b</sup>, Audrey Chapelle<sup>1,c</sup>, Séverin Rouchier<sup>1,d</sup>, Walter Schwarzenbach<sup>1,e</sup>, Alexis Drouin<sup>1,f</sup>, Valentine Chagneux<sup>1,g</sup>, Marcin Zielinski<sup>1,h</sup> and Christophe Maleville<sup>1,i</sup>

<sup>1</sup>Soitec, Chemin des Franques, 38190 Bernin, France

<sup>a</sup>enrica.cela@soitec.com, <sup>b</sup>kassem.alassaad@soitec.com, <sup>c</sup>audrey.chapelle@soitec.com, <sup>d</sup>severin.rouchier@soitec.com, <sup>e</sup>walter.schwarzenbach@soitec.com, <sup>f</sup>alexis.drouin@soitec.com, <sup>g</sup>valentine.chagneux@soitec.com, <sup>h</sup>marcin.zielinski@soitec.com, <sup>i</sup>christophe.maleville@soitec.com

\*corresponding author

**Keywords:** SmartSiC<sup>™</sup>, Smart Cut<sup>™</sup>, engineered substrate, crystal defects, micro-pipe, bulk inclusions, dislocation array, automatic defect classification, defect inspection, photoluminescence

**Abstract.** Power devices electronics based on Silicon Carbide (SiC) are emerging as a breakthrough technology for various applications. The link between the quality of SiC substrates and device performance has been widely discussed [1]. Smart Cut<sup>TM</sup> technology offers the opportunity to integrate a high quality SiC layer on a low resistivity handle wafer. Moreover the crystal quality of a single donor wafer can be replicated multiple times to provide an epitaxy-ready substrate in high volume [2]. Nevertheless, some extended grown-in defects of SiC starting material, like micropipes or bulk inclusions, may generate surface defects called "Crystal Originated Defects" (COD) on transferred layers. This paper explains how SmartSiC<sup>TM</sup> defect density can be reduced by limiting the number of extended defects on donor wafers. Specific inspection recipes were developed to monitor the starting material and the replicated engineered substrate: COD root-causes and effects were analyzed. We demonstrated how a well-suited quality control of donor wafers plays a major role to guarantee defect-free SmartSiC<sup>TM</sup> wafers.

#### Introduction

Power devices growing market requires new technical solutions to both lower manufacturing cost and to increase the device yield. Despite the significant progress in 4H-SiC material supply and quality, raw material manufacturers are struggling to fulfill market demand. Nowadays the main players in SiC power devices are starting the processing of 200 mm SiC substrates, therefore high volume production of prime crystal grade 200 mm 4H-SiC substrates is still a challenge [3-4].

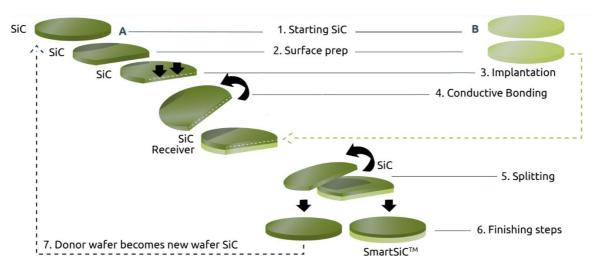

SmartSiC<sup>TM</sup> engineered substrates demonstrated the capability to combine a cost effective process (the Smart Cut<sup>TM</sup> process applied to SiC materials, explained in Fig.1) with high quality crystal grade and ultra low resistivity.

In addition, as detailed in [5], Smart Cut<sup>TM</sup> technology can be extended to 200 mm wafers to overcome the risk of large size SiC substrates shortage.

## **Crystal Originated Defects Generation Mechanism**

Smart  $Cut^{TM}$  technology (Fig. 1) consists in several steps including hydrogen implantation of the 4H-SiC starting wafer, enabling to control the transferred thickness (typically less than 1  $\mu$ m). The implanted wafer is bonded to a handle material before splitting (step 5). Because a key step of this process is to split a thin monocrystalline SiC layer from a donor, the defectivity of the starting material has an impact on the total usable area of SmartSiC<sup>TM</sup> wafers.

Fig. 1. Smart Cut<sup>TM</sup> process description, as adapted to SiC.

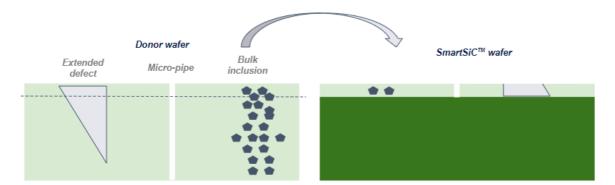

Depending on its quality, the donor substrate (starting SiC, step 1) can show different grown-in defect types, like micro-pipes and inclusions [6-7]. Some donor extended defects affect the integrity of the surface layer transferred using Smart Cut<sup>TM</sup> process, and can generate a Crystal Originated Defect (COD) after SmartSiC<sup>TM</sup> manufacturing, as schematized in Fig 2.

**Fig. 2.** Crystal Originated Defect generation from a 4H-SiC donor.

#### **Donor Wafer Extended Defects Characterization**

In this study the incoming defectivity of the donor was measured with SICA88 tool (Lasertec) consisting of a Nomarski difference interferential contrast (DIC) microscope for surface defects imaging and ultra-violet photoluminescence (UV-PL) setup for crystal defects characterization. We used 313 nm wavelength for PL excitation and a near-infrared filter to collect the images with a CCD sensor.

An Automatic Defect Classification (ADC) algorithm was optimized to capture and classify the extended grown-in defects of 4H-SiC, based on both surface and PL image properties.

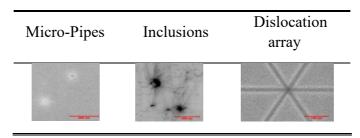

Three classes of substrate defects were found to be the most critical for a successful layer transfer process: *micro-pipes*, *inclusions* and *extended dislocation arrays*. Table 1 illustrates the defects as imaged using SICA88 UV-PL channel.

**Table 1.** UV-PL images of extended substrate defects.

Micro-pipes are well-known SiC defects consisting in a hollow core associated with a superscrew dislocation [7]. State-of-the art SiC manufacturers can limit micro-pipe generation to reach a density below 0.1 defects/cm<sup>2</sup>.

The mechanism of formation of "inclusion" defects during SiC crystal growth (especially Carbon inclusions) was described in [8] and [9]: large inclusions (>100  $\mu$ m) are generally well controlled by suppliers, whereas smaller inclusions (< 20  $\mu$ m) are often not specified.

Star-shaped dislocation arrays nature and effect were studied in [10]. The defect consists of a center area with high density of threading dislocations and six arms of dislocation arrays. Nowadays even prime grade 4H-SiC substrates show several star-shaped crystal defects per wafer.

## Correlation of 4H-SiC grown-in defects to SmartSiC<sup>TM</sup> quality

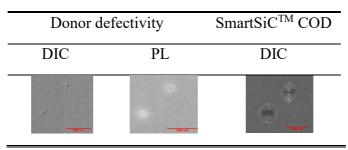

Similarly as for donors, engineered substrates defects were imaged using SICA88 surface DIC channel. A specific ADC was developed on a deep learning basis to classify SmartSiC<sup>TM</sup> defect types. An adapted and fine tuned inspection allows estimating the contribution of starting material defects to substrate total usable area for devices manufacturing. Table 2 shows an example of donor extended defects and related Cristal Originated Defect (COD) replicated to the transferred layer:

**Table 2.** Donor micro-pipes images and corresponding COD on SmartSiC<sup>TM</sup>.

Therefore, donor defectivity control is crucial to guarantee prime grade SmartSiC<sup>TM</sup> substrates.

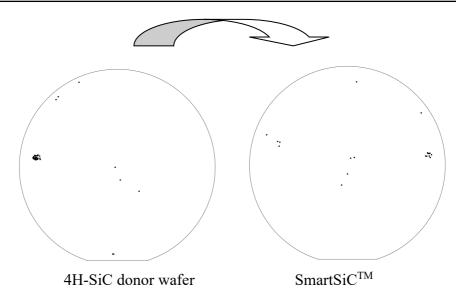

Fig. 3 illustrates the link between SiC starting materials and SmartSiC<sup>TM</sup> grade: donor wafer extended defects are mirrored into the replicated substrate.

**Fig. 3.** SmartSiC<sup>TM</sup> defect map correlation to donor quality (from SICA88 inspection): donor wafer with crystal defect signature (left) and corresponding replicated SmartSiC<sup>TM</sup> (right)

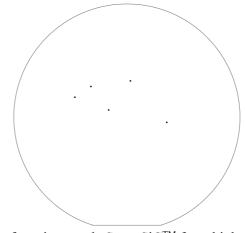

As shown in Fig.4, selecting high quality starting materials allows manufacturing engineered substrates with less than 0.1 defects/cm<sup>2</sup>:

Fig. 4. SICA defect map for prime grade SmartSiC<sup>TM</sup> from high quality donor.

### **Summary**

In this work, we showed how 4H-SiC donor material extended defects (micro-pipes, inclusions and star-shaped dislocation arrays) generate Crystal Originated Defects (COD) after SmartSiC<sup>TM</sup> manufacturing. A well-suited metrology was developed to monitor critical defects and we demonstrated the relation between donor and SmartSiC<sup>TM</sup> quality.

Novel Smart Cut<sup>TM</sup> approach allows selecting best-in class donor wafers and replicating their quality multiple times. Thus SmartSiC<sup>TM</sup> technology is able to provide both 150 mm and 200 mm high quality engineered substrates to growing power device market.

This work is supported by the H2020 - ECSEL JU program of the European Union under the grant of the TRANSFORM project 'Trusted European SiC Value Chain for a greener Economy' (ECSEL JU Grant No. 101007237).

#### References

- [1] T. Kimoto, Japanese Journal of Applied Physics 54, 040103 (2015).

- [2] S. Rouchier et al., Mat. Sc. Forum 1062, pp 131-135 (2022).

- [3] I. Manning et al., Mat. Sc. Forum 1062, pp 54-58 (2022).

- [4] M. Musolino et al., Microelectronic Engineering 274, 111976 (2023).

- [5] W. Schwarzenbach *et al.*, "SmartSiC<sup>TM</sup>: Boosting SiC performance for high-voltage power applications", ICSCRM 2022.

- [6] J. Fan and P.K. Chu, Silicon Carbide Nanostructures, (Springer International Publishing Switzerland, 2014) pp 35-37.

- [7] T.Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology, (John Wiley and Sons, Singapore, 2014) p. 51.

- [8] L. Guo *et al.*, Mat. Sc. Forum 897, pp 39-42 (2017).

- [9] M. Dudley et al., Applied Physics Letters 75, 6 (1999).

- [10] J.W. Lee *et al.*, Mat. Sc. Forum 527-529, pp 403-406 (2006).