# Impact of Single-Step Deep P-Body Implant on 1.2 kV 4H-SiC MOSFET

Submitted: 2024-09-20

Revised: 2025-08-07

Online: 2025-09-05

Accepted: 2025-08-08

Pavan Vudumula<sup>1,a</sup>, Yu-Chieh Chien<sup>1,b</sup>, Abdul Hannan Yeo<sup>1,c\*</sup>, Lakshmi Kanta Bera<sup>1,d</sup>, Umesh Chand<sup>1,e</sup>, Voo Qin Gui Roth<sup>1,f</sup>, Surasit Chung<sup>1,g</sup>, Navab Singh<sup>1,h</sup>, Yee-Chia Yeo<sup>1,i</sup>

<sup>1</sup>Institute of Microelectronics (IME), Agency for Science, Technology, and Research (A\*STAR), Singapore 138634.

\*E-mail: aVudumula\_pavan\_kumar@a-star.edu.sg, bChien\_Yu\_Chieh@a-star.edu.sg, channan\_yeo@a-star.edu.sg, dLakshmi\_kanta\_bera@a-star.edu.sg, eChand\_Umesh@a-star.edu.sg, fRoth\_Voo@a-star.edu.sg, gSurasit\_chung@a-star.edu.sg, hnavab@a-star.edu.sg, iYeo Yee Chia@a-star.edu.sg,

Keywords: Channeling implant, Deep p-body, Single step implant

**Abstract:** In this work, TCAD simulation of SiC MOSFETs design with deep (2  $\mu$ m) p-base using single step aluminum channeling implant along [0001] direction and JFET design using phosphorus implant is presented. The threshold voltage (V<sub>th</sub>) was around 3 V for both the devices. Improvements to the specific on-resistance (R<sub>on,sp</sub>) reduction by ~ 30 %, breakdown voltage (BV) enhancement by ~ 40 %, miller plateau (Q<sub>GD</sub>) reduction by ~ 30% is reported. Furthermore, both the Baliga figure-of-merit (BFOM) (BV<sup>2</sup>/R<sub>on,sp</sub>) and high-frequency figure-of-merit (HFOM) (R<sub>on,sp</sub> × Q<sub>GD</sub>) with 2  $\mu$ m deep p-base /JFET implant are enhanced as compared to shallow 0.7  $\mu$ m p-base/JFET implant. This paper provides valuable insights into the advantages of a single-step channeling implant at room temperature, without the need for a hard mask. This approach offers a high throughput with a low-cost process for fabricating high-performance SiC MOSFETs.

# Introduction

4H-SiC MOSFETs are well-suited for hybrid electric vehicles (HEV) and pure electric vehicles (EV) with a voltage rating of 1.2 kV. This is attributed to their impressive BV, low R<sub>on,sp</sub>, and fast switching speeds [1]. These devices consist of box-shaped implantation profiles formed through multi-step processes, including the p-base, JFET, n<sup>+</sup> and p<sup>+</sup> regions. Aluminum is used for both the p-base and p<sup>+</sup> implantation, while phosphorus is used for the JFET and n<sup>+</sup> implantation [2]. The multi-step implantation for box profiles is commonly conducted utilizing SiO<sub>2</sub> hard masks at high temperatures (> 400 °C). Undoubtedly, this process entails several steps that inherently impede manufacturing throughput. Few studies have investigated the impact of deep p-body and deep JFET on R<sub>on,sp</sub>, BV and short circuit withstand time [3,4]. A recent study has shown that a well-defined box-type profile can be achieved through a single-step implantation with significant depth along the [0001] and  $[11\overline{2}3]$  crystal orientations [5]. However, the box shape profile is more effective in the [0001] direction. The channeling implantation process performed at room temperature, allows the use of photoresists which eliminates the need for hard mask processes. This helps to streamline fabrication by eliminating several steps involved in hard mask patterning which could lead to significant cost reductions. This channeling implant has potential applications in SiC super junction devices too. However, there are little reports on the characteristics of deep p-body standard SiC MOSFETs using single-step implant. This study investigates the impact of a deep p-body using a single-step implant profile along [0001] and the corresponding JFET implant design using phosphorous channeling implant along [0001] in 1.2 kV MOSFETs in terms of its static and dynamic characteristics.

## **Results and Discussion**

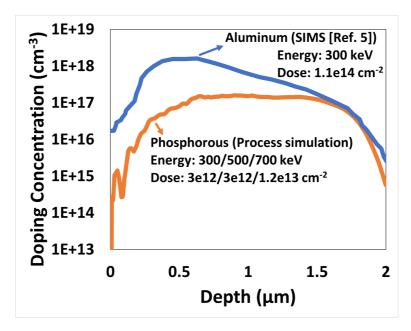

Experimental data on aluminum channeled implantation with an energy of 300 keV and a dose of  $1.2\times10^{13}$  cm<sup>-2</sup> along the [0001] crystal direction show a nearly box-shaped profile up to a depth of 2 µm [4]. This profile has been used for the p-body. To achieve a uniform JFET design, phosphorus implantation with optimized parameters (energy: 300/500/700 keV, dose:  $3\times10^{12}/3\times10^{12}/1.2\times10^{13}$  cm<sup>-2</sup>) is necessary. The implant profile is illustrated in Fig. 1.

**Fig. 1** Simulated doping profile for deep (2.0 μm) channeling implantation along [0001] orientation with optimized JFET profile.

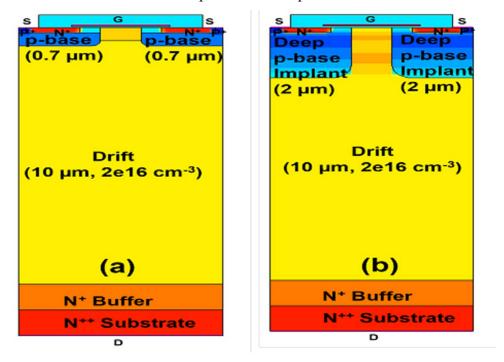

**Fig. 2** Schematic of (a) non-channeled 0.7 μm p-base and (b) channeled single-step implanted 2 μm p-base from TCAD simulation.

The device cross-section of a 1.2 kV MOSFET with a non-channeled implant for a p-body depth of 0.7  $\mu$ m and a p-body depth of 2  $\mu$ m using channeling implant is depicted in Fig. 2 (a) and (b), respectively. These devices are simulated using TCAD with W<sub>JFET</sub> = 1  $\mu$ m, L<sub>ch</sub> = 0.5  $\mu$ m, L<sub>drift</sub> =

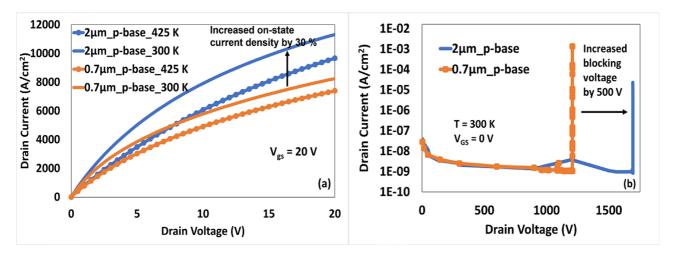

10  $\mu$ m, and a uniform epitaxy doping profile of 2 x 10<sup>16</sup> cm<sup>-3</sup>. The extracted threshold voltage (V<sub>th</sub>) is approximately 3 V for both devices, and specific on-resistance (R<sub>on,sp</sub>) from I<sub>d</sub>-V<sub>d</sub> characteristics (Fig. 3 (a)) is 30% lower with a JFET implant depth of 2  $\mu$ m compared to a shallow JFET implant depth of 0.7  $\mu$ m. This reduction is due to 2  $\mu$ m charge sustaining layer (CSL) with deep JFET implant, resulting in increased electron flow and thus a lower R<sub>on,sp</sub>. Fig. 3 (b) demonstrates a 40% improvement in blocking voltage for the p-body device with a depth of 2  $\mu$ m compared to the device with a depth of 0.7  $\mu$ m. Enhanced two-dimensional electric field distribution with deeper p-body compared to shallow p-base allows the device to sustain higher blocking voltages. Deep p-base better shields the channel and gate oxide from high drain bias due to the depletion in JFET.

**Fig. 3** Simulated (a) output and (b) blocking voltage characteristics for SiC MOSFETs with non-channeling (orange) and channeling (blue) implantation.

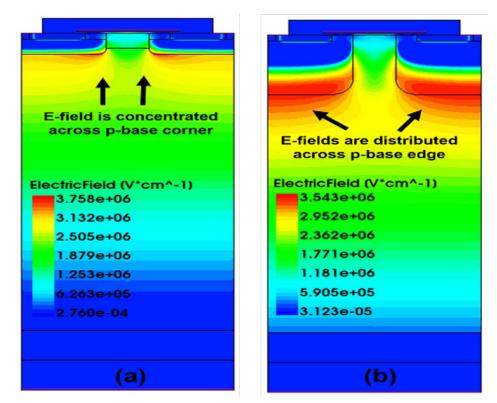

**Fig. 4** Blocking-state electric field distribution near breakdown for (a) non-channeling 0.7 μm and (b) channeling 2.0 μm p-base region in SiC MOSFETs.

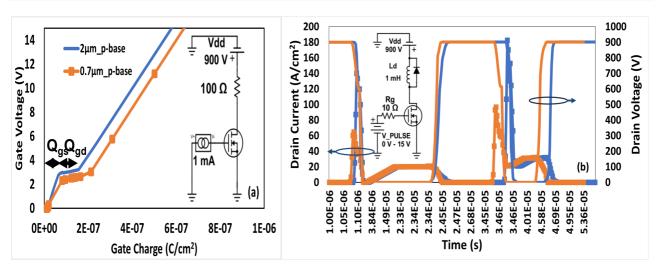

**Fig. 5** Simulated (a) gate charge and (b) switching characteristics with non-channeling 0.7 μm and channeling 2.0 μm p-base region in SiC MOSFETs.

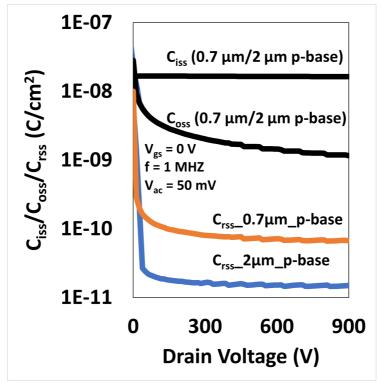

The off-state electric field distributions near the breakdown regime for 0.7 μm and for 2 μm p-base are shown in Fig. 4 (a) and 4 (b). Additionally, gate charge (Fig. 5(a)) and clamped inductive load switching simulations (Fig. 5 (b)) are performed using a mixed-mode SPICE environment to analyze the miller plateau (Q<sub>gd</sub>) and switching losses. The non-linear capacitance simulations with variations in drain bias, including input (C<sub>iss</sub>), output (C<sub>oss</sub>), and reverse transfer (C<sub>gd</sub>/C<sub>rss</sub>) capacitances are shown in Fig. 6. An 80% improvement in C<sub>rss</sub> corresponds to the reduced gate-to-drain coupling with the deep p-base design, which induces an increased depletion width along the JFET region during the switching regime. C<sub>iss</sub> and C<sub>oss</sub> remain the same for both devices as the remaining regions remain unaltered with a 5 μm cell pitch. Table 1 lists the performance metrics (BFOM, HF-FOM) and switching losses for both devices along with benchmarking results.

**Fig. 6** Simulated non-linear input, output, and miller capacitances with drain bias with non-channeling 0.7 μm and channeling 2.0 μm p-base region in SiC MOSFETs.

| 0.7 μm p-base 1.2 kV 4H-SiC MOSFET |                                    |                                                |                               | 2.0 μm p-base 1.7 kV 4H-SiC MOSFET |                                    |                                           |                               | Benchmark [Ref. 3]                                                |

|------------------------------------|------------------------------------|------------------------------------------------|-------------------------------|------------------------------------|------------------------------------|-------------------------------------------|-------------------------------|-------------------------------------------------------------------|

| <i>T</i> (°C)                      | BV (V)                             | $R_{ m on,sp}$ (m $\Omega$ -cm $^2$ )          | BFOM<br>(MV/cm <sup>2</sup> ) | <i>T</i> (°C)                      | BV (V)                             | $R_{ m on,sp} \ ({ m m}\Omega	ext{-cm}^2$ | BFOM<br>(MV/cm <sup>2</sup> ) | Design parameters:                                                |

| 27                                 | 1208                               | 2.4                                            | 608                           | 27                                 | 1693                               | 1.7                                       | 1686                          | $W_{\rm JFET} = 0.9  \mu \text{m}$                                |

| 150                                | 1220                               | 2.7                                            | 551                           | 150                                | 1700                               | 2.0                                       | 1445                          | $L_{ch} = 0.5 \mu m$                                              |

|                                    | $Q_{\rm gd}$ (nC/cm <sup>2</sup> ) | $R_{\rm on,sp}$ (m $\Omega$ -cm <sup>2</sup> ) | $HF-FOM$ $(nC-m\Omega)$       |                                    | $Q_{\rm gd}$ (nC/cm <sup>2</sup> ) | $R_{ m on,sp} \ ({ m m}\Omega{ m -cm}^2$  | HF-FOM (nC-mΩ)                |                                                                   |

| 27                                 | 117                                | 2.4                                            | 281                           | 27                                 | 82                                 | 1.7                                       | 140                           |                                                                   |

| 150                                | 117                                | 2.7                                            | 433                           | 150                                | 82                                 | 2.0                                       | 164                           | Electrical parameters:                                            |

|                                    | E <sub>on</sub> (m                 | J) <i>E</i>                                    | off (mJ)                      | E <sub>on</sub> (m                 |                                    | $E_{\rm off}$ (mJ)                        |                               | $R_{\text{on,sp}} = 4 \text{ m}\Omega\text{-cm}^2$<br>BV = 1560 V |

| 27                                 | 2.1                                |                                                | 8.0                           | 27                                 | 1.7                                |                                           | 8.0                           |                                                                   |

**Table 1** Simulated electrical performance metrics (BFOM and HF-FOM) at 27 °C and 150 °C.

#### Conclusion

In this study, we showed that the single-step channeling implantation is a highly promising method for realizing high BFOM and low HF-FOM in 4H-SiC MOSFETs. In addition, the implementation of channeling implantation ensured a superior process throughput at a much lower cost than the standard multi-step implant process.

## Acknowledgement

This work was supported by the Science and Engineering Research Council of A\*STAR (Agency for Science, Technology and Research) Singapore, under Grant No. A20H9A0242.

## References

- [1] B. J. Baliga, Silicon Carbide Power Devices, World scientific (2006).

- [2] T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology, John Wiley & Sons (2014).

- [3] D. Kim, N. Yun, A. J. Morgan, and W. Sung, "The effect of deep JFET and P-Well Implant of 1.2kV 4H-SiC MOSFETs," IEEE J. Electron Devices Soc., vol. 10, 989-99 (2022).

- [4] D. Kim and W. Sung, "Improved short-circuit ruggedness for 1.2kV 4H-SiC MOSFET using a deep p-well implemented by channeling implantation," IEEE Electron Device Letters, vol. 42, no. 12, 1822-1825 (2021).

- [5] M. K. Linnarsson, L. Vines, and A. Hallén, "Influence from the electronic shell structure on the range distribution during channeling of 40-300 keV ions in 4H-SiC," J. Appl. Phys., 130, 075701 (2021).