# On the Characterization of 4H-SiC PiN Diodes and JFETs for their Use in High-Voltage Bidirectional Power Devices

Submitted: 2024-09-20

Revised: 2025-03-21

Online: 2025-09-08

Accepted: 2025-03-21

Arne Benjamin Renz<sup>1,a\*</sup>, Yifan Jiang<sup>3,b</sup>, P.M. Gammon<sup>1,2,c</sup>, Erfan Bashar<sup>1,d</sup> and Jiankang Bu<sup>3,e</sup>

<sup>1</sup>University of Warwick, School of Engineering, Coventry, UK

<sup>2</sup>PGC Consultancy Ltd, Stratford-upon-Avon, UK

<sup>3</sup>Ideal Power Inc, Austin, TX, USA

<sup>a</sup>Arne.Renz@warwick.ac.uk , <sup>b</sup>Yifan.jiang@idealpower.com , <sup>c</sup>P.M.Gammon@warwick.ac.uk, dE.Bashar.1@warwick.ac.uk , <sup>e</sup>Jiankang.Bu@idealpower.com

**Keywords:** 4H-silicon carbide, BTRAN™, Field-effect transistors (FETs), Bidirectional Power Switches, lifetime enhancement

**Abstract.** A bidirectional field-effect transistor (FETs), known as a BTRAN<sup>TM</sup>, was designed, fabricated and characterized on silicon carbide (SiC) for the first time. After grinding to original N+ substrate, atomic force microscopy revealed grinding marks and an increase of surface roughness to a rms value of 7.812 nm (50 μm x 50μm scan area), but these were suitable for further device processing. A lifetime enhancement oxidation process carried out on both sides of the drift region at 1400°C for 4 hrs in dilute oxygen (4 slm Ar : 1 slm O<sub>2</sub>) enhanced the average carrier lifetime from 1 μs to 5 μs. After device fabrication, functionality was proven both on-die and on a custom-made PCB design that enabled access to all four terminals (topside and bottomside) in the on-state and off-state. Off-state measurements revealed a breakdown voltage exceeding 7 kV. In summary, these encouraging results, with necessary improvements of contact resistivity, will build the foundation for the second generation of SiC BTRAN<sup>TM</sup> devices.

### Introduction

Power electronics are a key enabling technology in the process towards a fully electrified society. Modern power conversion is integral in delivering efficient electric vehicles (EVs) and their fast charging stations, advanced motor drives and the integration of renewable energy into a modern grid. With an EV market share of 50% targeted by the US Government and the fact that about 50 % of all electricity is used to power and drive electric motors, it becomes evident that efficiency of power electronics systems will be at the center of any policy that wants to steer society towards a more sustainable energy economy.

In these applications, well-developed converter topologies are key. Ideally, these would contain semiconductor switches that have both excellent blocking capabilities in both directions and bidirectional current conduction in the on-state [1]. However, none of the conventional semiconductor switches, e.g., insulated-gate bipolar transistors (IGBTs) and metal-oxide-semiconductor field-effect transistors (MOSFETs), can provide these functionalities alone, such that multiple discrete device topologies are typically deployed. As an example, an inverse-series connection of two silicon (Si) MOSFETs achieves switching functionality in two directions, but the total on-resistance (Ron) is doubled compared to a single device. To circumvent this, a second arrangement needs to be connected in parallel. This means that, for the realization of bidirectional switching capability, using common power semiconductors results in a fourfold increase in chip area and cost. The introduction of monolithic bidirectional switches (MBDSs) with a single shared drift region for blocking either voltage polarity, and two gates, means that these converter topologies need to reevaluated.

The research activities on MBDS devices can be traced back to the early 2000s, with early activities focusing on IGBTs that were reverse-blocking [2]. Within a few years, multiple companies started to investigate MBDSs based on gallium nitride (GaN) high-electron mobility transistors (HEMTs). These devices were typically rated at around 600V, with resistances reaching 140 m $\Omega$  [3].

In silicon carbide (SiC), MBDS device development is still at a very early stage. Research activities have so far resulted in the successful fabrication of a monolithic bidirectional IGBT, where demonstrator devices have successfully blocked up to 7 kV [3]. However, processing requires a non-standard, processing methods, including grinding away the original wafer to access the backside of the drift region, double sided lifetime enhancement, and double-sided photolithography including backside alignment. When packaged, novel cooling solutions as both sides of the wafer feature intricate structures, such as gates, base and emitter regions.

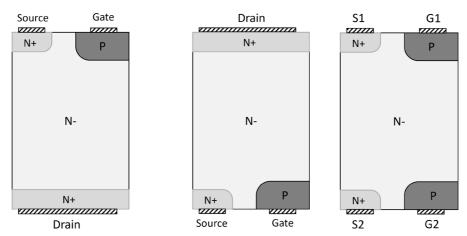

This work aims to demonstrate a SiC BTRAN<sup>TM</sup> device concept that was originally developed for Si processing [4]. This features a field-effect transistor (FET) on each side of the wafer with a shared collector region (B-TRAN<sup>TM</sup>). Vertical Si devices have achieved a blocking voltage of  $\pm$  1200 V and were able to support pulsed currents of up to  $\pm$  100 A. In this investigation, we aim to transfer this concept to 4H-SiC. Firstly, vertical PiN diodes and lateral devices were simulated, fabricated and characterized on both the C-face (000-1) and Si-face (0001), as required to produce a SiC B-TRAN<sup>TM</sup>. The carrier lifetime of the thick drift region was then optimized to enable sufficient carrier diffusion for conductivity modulation.

## **Experimental**

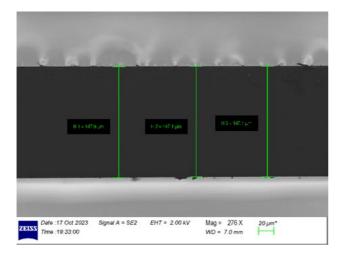

Devices were fabricated on a 100 mm diameter, 350  $\mu$ m thick n+-substrate, onto which was grown a 150  $\mu$ m thick n-type unintentionally doped (<1 x  $10^{15}$  cm<sup>-3</sup>) epitaxial layer. After initial alignment mark formation between topside and bottomside, the samples were flipped to remove the n+-substrate by means of grinding. The scanning electron microscope (SEM) image in Fig. 2 shows the resulting cross-section of the wafer. High-temperature oxidation was then carried out at 1,400°C in a dilute oxygen ambient (4 slm Ar : 1 slm O<sub>2</sub>) on both the Si-face and C-face to improve the carrier lifetime,

**Fig.1.** Cross-sectional representation of the JFET structures (left and middle) and the full BTRAN <sup>TM</sup> device (right).

**Fig. 2.** (Left) The drift region thickness post-grinding, measured by cross-sectional SEM imaging. (Right) Optical microscopy image of the finished one-sided BTRAN device, fabricated on the C-face after substrate removal.

similar to [5]. P+- implants and n+-implants were then carried out on both the Si-face and C-face to enable gate, source (on the BTRAN) and cathode and anode ohmic contact formation (on the PiN diodes). A 1.5 µm thick passivation layer was then deposited on both samples by means of low-pressure chemical vapour deposition (LPCVD), using tetraethyl orthosilicate (TEOS) as Si precursor before a 1.5 µm thick aluminium (Al) pad metal was deposited to aid with device testing and wire bonding. The final device structure can be seen in Fig. 1, with microscopy images in Fig. 2. Atomic force microscopy (AFM) measurements were carried out on a Bruker Icon AFM in peakforce tapping mode to extract surface roughness and quantify any possible large wafer bow post-grinding.

The enhancement throughout the drift thickness is diffusion limited due to the low diffusion coefficients of carbon and oxygen in SiC. Common carrier lifetime measurement techniques such as microwave-detected photoconductance decay ( $\mu$ -PCD) probe the near-surface region of the epilayer, give an indication of carrier lifetime. Time transient data was measured by  $\mu$ -photoconductive decay (PCD), which has a 355 nm ultraviolet (UV) laser source. The effective carrier lifetime was assessed prior to and after lifetime enhancement in a custom Freiberg Instruments spotMDP setup.

#### **Results**

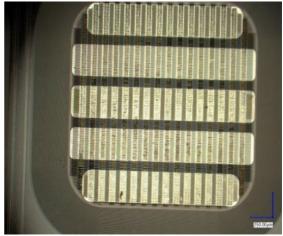

Low surface quality post-grinding is required for the success of the device fabrication. An extensive AFM investigation was conducted once the samples had their substrates removed and prior to further processing. An overview of the extracted root mean square (RMS) values can be found in Table 1. Representative images of the top side and bottom side can be found in Fig. 3 below. A full wafer post-grinding is depicted in Fig. 4 (left), too.

| Topside/backside | Position on 4" wafer | Scan area        |                    |

|------------------|----------------------|------------------|--------------------|

|                  |                      | 5 μm x 5 μm (nm) | 50 μm x 50 μm (nm) |

| Topside          | Centre (0,0)         | 0.267            | 0.494              |

| Topside          | Bottom right         | 0.256            | 0.615              |

|                  | (25mm, -25mm)        |                  |                    |

| Topside          | Top left             | 0.254            | 0.538              |

|                  | (-25mm, 25mm)        |                  |                    |

| Backside         | Centre (0,0)         | 4.377            | 7.812              |

| Backside         | Bottom right         | 5.122            | 5.473              |

|                  | (25mm, -25mm)        |                  |                    |

| Backside         | Top left             | 3.369            | 4.619              |

|                  | (-25mm, 25mm)        |                  |                    |

**Table I.** Extracted surface roughness parameters post-substrate removal. All measurements were done at room temperature.

**Fig. 3.** (Left) Image of a representative 50 um x 50 um scan of the (left) frontside, which did not undergo the processing and achieved a <1 nm rms surface roughness value and (right) backside, which was grinded, showing grinding marks post-processing.

The surface quality of the thick, as-grown, epitaxial layer can be seen when observing the extracted rms values from the top. Here, even surface roughness values that are extracted from a  $50\mu m \times 50\mu m$  scan area are significantly lower than 1 nm, with values averaging 0.55 nm. No obvious further surface modifications/decorations were visible during any topside measurement, with all measurements averaging tightly at around 0.5 nm. After the substrate was then fully removed by grinding, the surface showed grinding marks throughout, with surface roughness values averaging 10 times higher at 5.96 nm. With all contacts in the BTRAN<sup>TM</sup> devices being ohmic, fabrication was then continued.

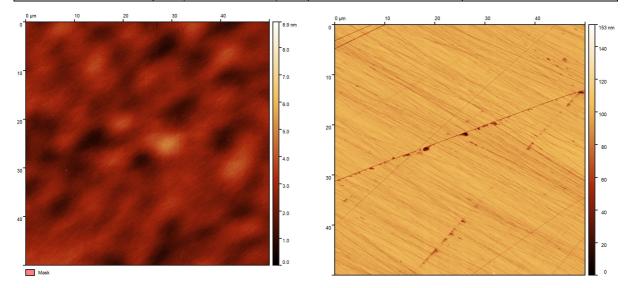

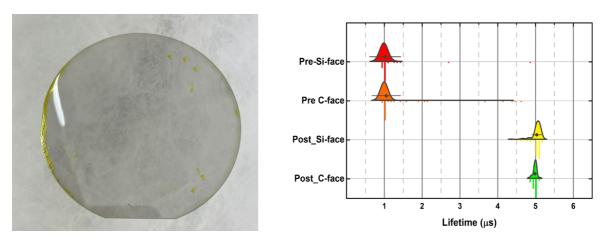

Fig. 4. (Left) Image of a full four inch wafer post-grinding, with bright spots representing triangular defects in the 4H-SiC epilayer and right) u-PCD measurements before and after high-temperature oxidation ( $\lambda = 355$  nm), with 400 measurements being taken at room temperature per dataset.

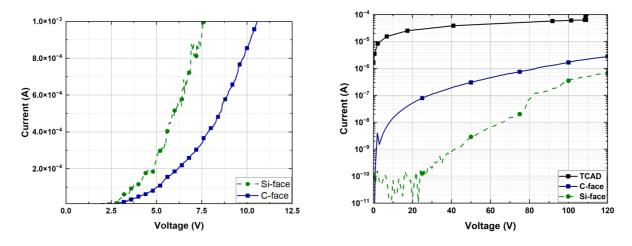

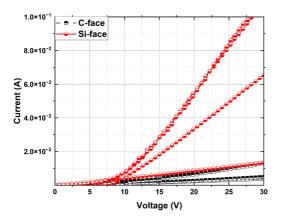

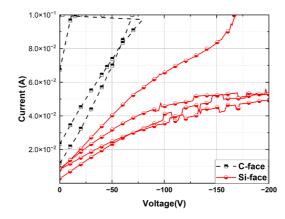

**Fig.5**. Gate-source forward (left) and reverse (right) characteristics of diodes fabricated on C-and Si-face.

Fig.6. On state of vertical PiN diodes fabricated on both the C-and Si-face.

After the grinding process, an analysis of the transient carrier lifetime on the Si- and C-face was carried out before and after the lifetime enhancement oxidation process. The results are shown in Fig. 4 (b), where 400 spot measurements were taken at room temperature across the wafer. More details about the 4 hour lifetime enhancement procedure can be found in [5]. Prior to the lifetime enhancement treatment, the effective carrier lifetime on the thinned wafer averaged about 1 µs, both on the Si- and the C-face. After the thermal oxidation process, the lifetime was increased to approximately 5 µs, which will enhance conductivity modulation in the thick drift region.

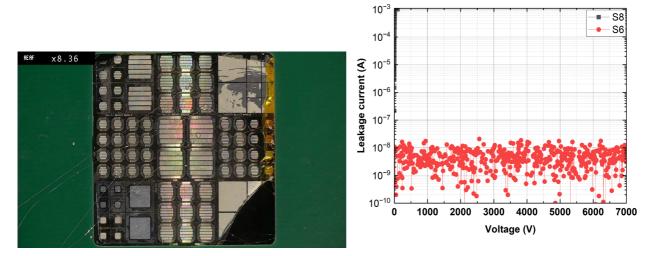

**Fig. 7.** (Left) Final chip on PCB for bi-directional switching of the BTRAN<sup>TM</sup>, allowing for the static characterization of multiple devices on that chip. Individual devices were then wire bonded to contact pads that are located outside of this chip. (Right) blocking voltage of a single tested BTRAN<sup>TM</sup> device, showing no visible signs of leakage up to 7 kV.

The active area design comprised a 1  $\mu m$  trench etch into the gate area, into which a p+-region of 200 nm was implanted.

After fabrication, the lateral P-gate to N-source breakdown in the devices was measured on wafer, depicted in Fig. 5, right, where the breakdown exceeds 100 V, outperforming TCAD simulation results. Representative on-state results for the lateral JFETs (Fig. 5, left) and vertical PiN diodes (Fig. 6) show the functionality of the fabricated structures.

Having proven the general functionality of the fabricated structures on-die, wafers were laser cut and chips were then soldered onto custom-made PCBs. These were designed to allow access to terminals on both the back side and the top side of the same chip. An example of a chip that had been soldered onto one of these PCBs can be seen in Fig. 7 (left) below. Terminals were bonded to terminal pads by means of wire bonding using approx. 50 µm aluminium wire. Once this was done, we were able to measure the blocking voltage (S1-G2) between the topside source and bottom side gate, all the way up to 7 kV. To prevent arcing, fluorinert gel was applied directly before the leakage measurements were carried out. A representative device with poor leakage performance is shown in Fig. 7 (right). Some devices managed to show excellent breakdown performance, as demonstrated in the same figure. For leakage measurements, all other terminals were left floating.

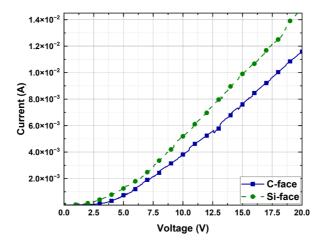

The same configuration also allowed for the on-state measurement of devices, which can be seen in Fig. 8 (left) and the on-state voltage drop in Fig. 8 (right).

**Fig. 8.** (Left) On-state of the observed SiC BTRAN<sup>TM</sup> and (Right) on-state voltage drop on individual devices..

The on-state (G1-S1) was then measured using a B1505 A probe station with a high-current extender (bottom left). The G1-S1 diode performance, with forward current up to 100 mA, could be observed on Fig. 8(left). The other terminals were left floating. A specific contact resistivity of the p-type ohmic contact of  $1.16 \times 10^{-2} \Omega \cdot \text{cm}^2$  and  $1.34 \times 10^{-3} \Omega \cdot \text{cm}^2$  of the n-type ohmic contact were extracted from TLM measurements and can be one source of the relatively high resistance that can be observed in the on-state of the PiN diodes, as well as the BTRAN<sup>TM</sup>. In Fig. 8 (right), the on-state voltage drop between devices can be seen, confirming this trend. Here, a DC voltage of 30 V was applied across the topside of the base, for current injection through the base. The voltage was then swept between the topside source (S1) and gate on the bottom side (G2).

#### Conclusion

In this investigation, we successfully simulated, designed, fabricated and characterized the first fully functional silicon carbide BTRAN device. As part of the challenges in the fabrication process, we demonstrated, that, after substrate removal, the backside of the wafer showed grinding marks and an increase in surface roughness up to 7.812 nm, when investigated on a  $50\mu m \times 50\mu m$  by means of atomic force microscopy.

To help conductivity modulate the device, a carrier lifetime enhancement investigation was conducted, where we oxidized the samples in a high-temperature furnace at  $1400^{\circ}$ C for 4 hrs in dilute oxygen ambient (4 slm Ar : 1 slm O<sub>2</sub>). This raised the lifetime relatively uniformly from 1  $\mu$ s (pretreatment) to approximately  $5\mu$ s (post-enhancement), both on the C- and Si-face of a full 4" wafer.

The fully fabricated structures were then measured on-die, where on-states showed the full functionality of one-sided structures laterally, although the conduction response suffered heavily from high specific contact resistivities, averaging  $1.16 \times 10^{-2} \ \Omega.\text{cm}^2$  and  $1.34 \times 10^{-3} \ \Omega.\text{cm}^2$  on TLM structures for p-type and n-type ohmic contacts, respectively. Selected chips were then soldered on a custom-made PCB design, allowing the static characterization of the full BTRAN<sup>TM</sup> devices by enabling access to both contacts on the topside and backside of the chip. Here, on-states of the full device structures showed general functionality, although suffering from high specific contact resistivities. A promising performance off-state was demonstrated, blocking more than 7 kV. In summary, these encouraging results, with necessary improvements of contact resistivity, will build the foundation for a second generation of BTRAN<sup>TM</sup> devices to full commercialization.

#### References

- [1] Huber, J, and Kolar. J.W., "Monolithic Bidirectional Power Transistors", in *IEEE Power Electronics Magazine*, Volume. 10, 2023.

- [2] S. Chowdhury et al., "Operating principles, design considerations, and experimental characteristics of high-voltage 4H-SiC bidirectional IGBTs", in *IEEE Trans. Electron Devices*, vol.64, pp. 888-896, 2017.

- [3] F. Vollmaier et al., "Performance evaluation of future T-type PFC rectifier and inverter systems with monolithic bidirectional 600V GaN switches", in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, pp. 5297-5304, 2021.

- [4] M. Dong et al., "BTRAN<sup>TM</sup> Optimization and Performance Characterization.", in *2023 IEEE Applied Power Electronics Conference and Exposition (APEC)*, pp. 1835-1839, 2023.

- [5] T. Kimoto et al., "Carrier lifetime and breakdown phenomena in SiC power device material.", in *Journal of Physics D: Applied Physics*, vol. 51, pp. 363001, 2018.