# SiC MOSFETs C-V Capacitance Curves with Negative Biased Drain

Submitted: 2024-09-20

Revised: 2025-02-24

Online: 2025-09-08

Accepted: 2025-02-24

Ilaria Matacena<sup>1,a\*</sup>, Luca Maresca<sup>1,b</sup>, Michele Riccio<sup>1,c</sup>, Andrea Irace<sup>1,d</sup>, Giovanni Breglio<sup>1,e</sup>, Santolo Daliento<sup>1,f</sup>

<sup>1</sup>Dept. of Electrical Engineering and Information Technologies, University of Naples Federico II, via Claudio, 21, 80125, Naples, Italy

<sup>a</sup>ilaria.matacena@unina.it, <sup>b</sup>luca.maresca@unina.it, <sup>c</sup>michele.riccio@unina.it, <sup>d</sup>andrea.irace@unina.it, <sup>e</sup>breglio@unina.it, <sup>f</sup>daliento@unina.it,

Keywords: SiC MOSFET, Capacitance, C-V curve.

Abstract. There are some technological issues in SiC MOSFETs that are still unsolved. One of the main problems is the high density of traps/defects at the SiC/SiO<sub>2</sub> interface. Traps distribution at such interface is complex and it affects the overall performance of the device. The high-density of defects at the SiC/SiO<sub>2</sub> interface is a relevant problem since it can influence the overall performance of the device, causing detrimental impacts on threshold voltage stability, channel mobility and leakage current amplitude. Due to the fundamental importance of the SiC/SiO<sub>2</sub> interface characterization, several techniques have been employed to investigate defects properties related to this region. In this work non-classical C-V measurements are performed. Capacitance is measured between Gate and Source terminals while a fix DC voltage is imposed on the Drain. This latter is considered among positive values in the first case, while it is chosen as a negative voltage in the second case. The arising capacitances in both cases show an unexpected behavior which can be related to interface properties. To this aim numerical analysis is performed in Sentaurus TCAD environment.

# Introduction

Silicon Carbide (SiC) MOSFETs are gradually replacing Silicon (Si) MOSFETs due to the excellent properties of SiC material. High thermal conductivity and high bandgap [1] are indeed properties of such material. These devices technology has undergone a great development in last decades. However, there are still some issues that are not completely solved. Among these it worth to be mentioned that the density of defects arising at the SiC/SiO<sub>2</sub> interface is orders of magnitudes higher with respect to Si/SiO<sub>2</sub>. These defects can affect some crucial properties of the overall device [2] such as the channel mobility [4] and threshold voltage instability [3]. Given the key role played by the quality of the mentioned interface, several techniques have been considered to characterize the defect/traps interface density. Among these, the most used methods are based on the measurement of impedance, and more in detail capacitance varying with voltage. These techniques are widely used in various applications ranging from semiconductor devices and solar cells [5]-[13] to batteries [14]. This method is non-destructive, and it allows a fast characterization procedure. In literatures, most part of the studies for power devices are carried out on MOS structure where it is possible to rely to low-high frequency capacitance method [15]-[19]. The capacitance behavior in MOS structure changes drastically with varying frequency [20] and this variation can give information about the defects/traps in the device under test. In fact, the inversion charge is able to follow the applied stimulus only if the frequency is sufficiently low, due to the low thermal carrier generation in the depletion region. This means that in the inversion region the behavior of the capacitance is mainly described by the inversion charge not able to follow the high frequency of the applied stimulus. The last statement holds true only in the case of MOS structure. In MOSFETs, the situation is different since the channel is refilled with carriers coming from the Source and Drani regions in the inversion region. Thus, capacitance behavior in the inversion region results not varied for low and high frequency and the low-high frequency method cannot be used in this case [21]. From the foregoing, it is clear the necessity to accurately analyze the capacitance arising from a MOSFET device. This

can be performed by means of numerical environments which enable to characterize the SiC/SiO<sub>2</sub> interface properties [22]-[26]. The mentioned capacitance is usually measured at the Gate terminal and connecting Drain and Source terminals [27]-[29]. In previous works [25],[30]-[33], we investigated a non-classical C-V measurements on commercially available planar SiC MOSFETs. In these studies, experimental data are obtained by applying the AC small signal on the Gate, while a fix DC bias is applied on the Drain and the Source terminal is grounded. The so obtained capacitance shows an unexpected peak in the inversion region, which can be related to the interface properties and the channel region. In this work, the capacitance trend is investigated when the applied fix Drain voltage assumes negative values. Experimental results are shown and supported by numerical analysis. The presented model is built in Sentaurus TCAD environment. An unexpected peak in capacitance behavior is found in both experimental and numerical results.

# **Experimental Results**

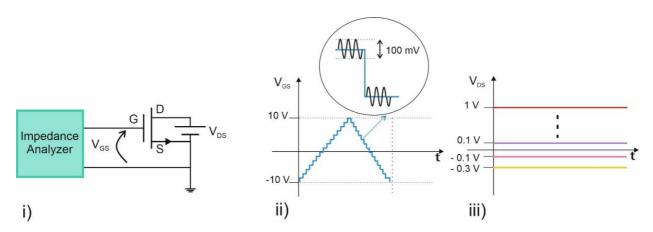

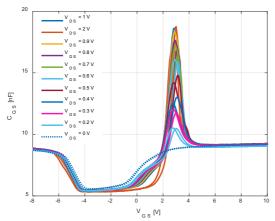

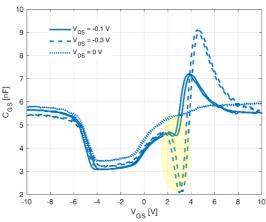

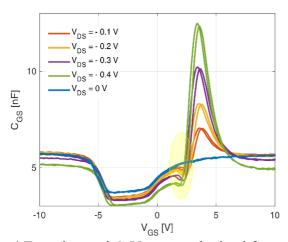

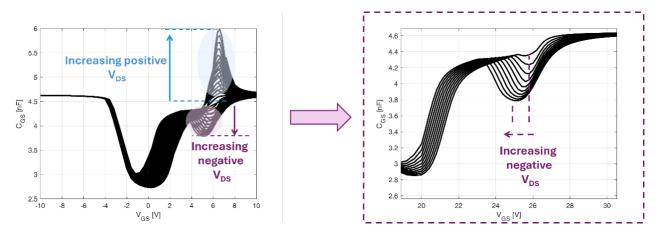

Capacitance is measured on commercially available planar SiC MOSFETs, as shown in Fig. 1. The excitation signal consisting of a DC voltage ranging from -10 V to 10 V with a superimposed AC small signal, Fig. 1ii, is applied on the Gate of the device under test. A fix DC bias, Fig. 1iii is applied on the Drain, while the Source is connected to ground. The Gate capacitance measured when the Drain is biased with fix positive values is presented in Fig. 2. Capacitance has classical behavior, i.e. the case when  $V_{DS} = 0$  V (dotted line), in the accumulation and depletion region. In the inversion region the situation drastically changes when  $V_{DS} \neq 0$  V. A sharp peak arises, and its height is higher as V<sub>DS</sub> increases. The experimental curves obtained when a positive Drain voltage is applied show a non-negligible peak centered at a voltage close to the threshold voltage. The arising peak appears more prominent as the applied Drain voltage increases. In previous works, the peak shape was associated to traps in the channel region [22] under the SiC/SiO<sub>2</sub> interface. The experimental data collected when the applied Drain voltage is negative are presented in Fig. 3 and Fig. 4. Such curves exhibit a different behavior from the previous case. These capacitances show a sudden decrease between the depletion and inversion region, highlighted region in the mentioned figures. The capacitance reaches its minimum for a Gate voltage which is decreasing with higher negative Drain bias. After such behavior, the capacitance increases, showing a peak in the inversion region.

Fig. 1. i) Experimental setup; ii) Gate imposed voltage; iii) Drain applied voltage.

**Fig. 2** Experimental C-V curves obtained from a commercial device with positive V<sub>DS</sub>.

**Fig. 3** Experimental C-V curves obtained from a commercial device with negative V<sub>DS</sub>.

**Fig. 4** Experimental C-V curves obtained from a commercial device with negative V<sub>DS</sub>.

**Fig. 5.** Sketch of the TCAD structure.

### **Numerical Setup**

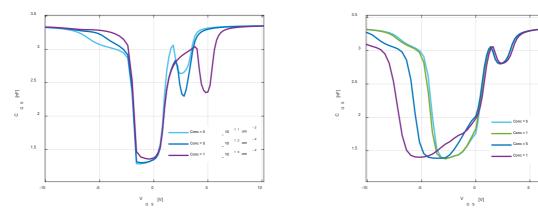

A numerical framework has been developed in Sentaurus TCAD tool by Synopsys. The structure under test is presented in Fig. 5. The performed analysis consists in an AC small signal analysis which allows to investigate the capacitance behavior [23]. Numerical results obtained by considering both negative and positive Drain voltages are reported in Fig. 6. More in detail, the values considered for V<sub>DS</sub> range from 1 V to -1 V in steps of 0.1 V. The Gate voltage has been swept from -10 V to 10 V. The AC superimposed signal has been chosen with a magnitude of 100 mV and a frequency of 100 kHz. The presented curves show similar trends to the experimental collected data. For positive Drain voltage, the capacitance peak is higher as the voltage increases, while the curves obtained with negative Drain voltage exhibit a decrease after which the behavior starts to increase again. Also, referring to the numerical results in the case of negative Drain bias, the capacitance shows a minimum at a lower Gate voltage as negative Drain voltage increases. The dependence of capacitance from interface traps when Drain is negatively biased has also been considered. More in detail a uniform traps distribution along the SiC/SiO<sub>2</sub> interface has been described. In the first case only acceptors traps have been considered. The capacitance trend obtained is presented in Fig. 7, for a Drain voltage  $V_{DS} = -0.5 \text{ V}$ . Acceptors modify the capacitance behavior in the inversion region and, more in detail, the capacitance decreases more as traps concentration increases. The influence of donor traps has also been investigated. Numerical capacitance trends are shown on Fig. 8 for the case  $V_{DS} = -0.5 \text{ V}$ . Those results show as donors modify the right part (i.e. the accumulation and depletion regions) of the capacitance curve.

Fig. 6 Numerical C-V curves obtained with negative and positive V<sub>DS</sub>.

**Fig. 7.** Numerical C-V curves obtained with a trap distribution of acceptors.

**Fig. 8.** Numerical C-V curves obtained with a trap distribution of donors.

### **Conclusions**

In this work, we exploited a non-classical C-V measurement with different types of Drain biasing. More in detail, Gate capacitance is measured when a fix bias is imposed on the Drain. The Drain voltage imposed is considered both positive and negative. The resulting curves exhibit a sharp peak near the threshold voltage in either case. Experimental data are supported by numerical analysis performed in Sentaurus TCAD. Numerical results have shown similar trends to those obtained in experiments. Numerical analysis has also shown how capacitance curve measured with negative biased Drain modifies when a distribution of acceptors/donors traps is described at SiC/SiO<sub>2</sub> interface.

#### References

- [1] B. J. Baliga, Fundamentals of power semiconductor devices, Springer Science & Business Media, (2010).

- [2] C. Raynaud, et al., Comparison of trapping-detrapping properties of mobile charge in alkali contaminated metal-oxide-silicon carbide structures, Applied physics letters 66, no. 18: 2340-2342, (1995).

- [3] D. Peters et al., Investigation of threshold voltage stability of SiC MOSFETs, ISPSD, (2018).

- [4] V. V. Afanasev, et al., Intrinsic SiC/SiO2 interface states, physica status solidi (a) 162, no. 1: 321-337, (1997).

- [5] Lancellotti, L., Lisi, N., Veneri, P. D., Bobeico, E., Matacena, I., & Guerriero, P. (2019, July). Graphene-on-Silicon solar cells with graphite contacts. In 2019 International Conference on Clean Electrical Power (ICCEP) (pp. 199-203). IEEE.

- [6] Gobbo, C., Di Palma, V., Trifiletti, V., Malerba, C., Valentini, M., Matacena, I., ... & Tseberlidis, G. (2023). Effect of the ZnSnO/AZO interface on the charge extraction in Cd-free kesterite solar cells. Energies, 16(10), 4137.

- [7] Sonnet, A. M., Hinkle, C.L., Heh, D., Bersuker, G., & Vogel, E.M. (2010). Impact of semiconductor and interface-state capacitance on metal/high-k/GaAs capacitance–voltage characteristics. *IEEE transactions on electron devices*, *57*(10), 2599-2606.

- [8] Lancellotti, L., Bobeico, E., Della Noce, M., Veneri, P. D., & Matacena, I. (2018, June). Work function determination of transparent contact for a: Si/c-Si heterojunction solar cells. In 2018 IEEE International Conference on Environment and Electrical Engineering and 2018 IEEE Industrial and Commercial Power Systems Europe (EEEIC/I&CPS Europe) (pp. 1-5). IEEE.

- [9] Matacena, I., Guerriero, P., Lancellotti, L., Alfano, B., De Maria, A., La Ferrara, V., ... & Daliento, S. (2023). Impedance spectroscopy analysis of perovskite solar cell stability. Energies, 16(13), 4951.

- [10] Westerhoff, U., Kurbach, K., Lienesch, F., & Kurrat, M. (2016). Analysis of lithium-ion battery models based on electrochemical impedance spectroscopy. Energy Technology, 4(12), 1620-1630.

- [11] Matacena, I., Lancellotti, L., Daliento, S., Alfano, B., De Maria, A., La Ferrara, V., ... & Guerriero, P. (2023). Impedance Spectroscopy of Perovskite Solar Cells With SnO 2 Embedding Graphene Nanoplatelets. IEEE Journal of Photovoltaics.

- [12] Turut, A. (2020). On current-voltage and capacitance-voltage characteristics of metal-semiconductor contacts. Turkish Journal of Physics, 44(4), 302-347.

- [13] Matacena, I., et al. "Capacitance–Voltage Investigation of Encapsulated Graphene/Silicon Solar Cells." *IEEE Transactions on Electron Devices* (2023).

- [14] Gaberšček, M. (2022). Impedance spectroscopy of battery cells: Theory versus experiment. Current Opinion in Electrochemistry, 32, 100917

- [15] Chang, Yao-Wen, et al. "Charge-based capacitance measurement for bias-dependent capacitance." *IEEE Electron Device Letters* 27.5 (2006): 390-392.

- [16] Almora, Osbel, et al. "On Mott-Schottky analysis interpretation of capacitance measurements in organometal perovskite solar cells." *Applied Physics Letters* 109.17 (2016).

- [17] Gobbo, Carla, et al. "Effect of the ZnSnO/AZO interface on the charge extraction in Cd-free kesterite solar cells." *Energies* 16.10 (2023): 4137.

- [18] Matacena, Ilaria, et al. "Forward bias capacitance investigation as a powerful tool to monitor graphene/silicon interfaces." *Solar Energy* 226 (2021): 1-8.

- [19] Heerens, W-C. "Application of capacitance techniques in sensor design." *Journal of physics E: Scientific instruments* 19.11 (1986): 897.

- [20] Schroder, D.K. Semiconductor Material and Device Characterization, 3rd ed.; Wiley: Hoboken, NJ, USA, 2006.

- [21] Hu, Chenming Calvin. "Modern Semiconductor Devices for Integrated Circuits." Part I: Electrons and holes in a semiconductor (2011).

- [22] Matacena, L. Maresca, M. Riccio, A. Irace, G. Breglio, S. Daliento, & A. Castellazzi, (2022). SiC MOSFET CV Characteristics with Positive Biased Drain. In Materials Science Forum (Vol. 1062, pp. 653-657). Trans Tech Publications Ltd

- [23] L. Maresca et al. Influence of the SiC/SiO 2 SiC MOSFET Interface Traps Distribution on C–V Measurements Evaluated by TCAD Simulations. IEEE Journal of Emerging and Selected Topics in Power Electronics 9.2 (2019): 2171-2179.

- [24] Matacena, I., Maresca, L., Riccio, M., Irace, A., Breglio, G., & Daliento, S. (2022, June). Experimental Analysis of CV and IV Curves Hysteresis in SiC MOSFETs. In *Materials Science Forum* (Vol. 1062, pp. 669-675). Trans Tech Publications Ltd.

- [25] Matacena, Ilaria, et al. "SiC MOSFET CV Curves Analysis with Floating Drain Configuration." Materials Science Forum. Vol. 1062. Trans Tech Publications Ltd, 2022.

- [26] Matacena, Ilaria, et al. "Evaluation of Interface Traps Type, Energy Level and Density of SiC MOSFETs by Means of CV Curves TCAD Simulations." Materials Science Forum. Vol. 1004. Trans Tech Publications Ltd, 2020.

- [27] Wei, Jiaxing, et al. "Interfacial damage extraction method for SiC power MOSFETs based on CV characteristics." 2017 29th International Symposium on Power Semiconductor Devices and IC's (ISPSD). IEEE, 2017.

- [28] Tsuji, Katsuhiro, et al. "Measurement of MOSFET CV curve variation using CBCM method." 2009 IEEE International Conference on Microelectronic Test Structures. IEEE, 2009.

- [29] Jouha, Wadia, et al. "Physical study of SiC power MOSFETs towards HTRB stress based on CV characteristics." IEEE Transactions on Device and Materials Reliability 20.3 (2020): 506-511.

- [30] Matacena, Ilaria, et al. "SiC MOSFETs Capacitance study." *e-Prime-Advances in Electrical Engineering, Electronics and Energy* (2023): 100251.

- [31] Matacena, I., Maresca, L., Riccio, M., Irace, A., Breglio, G., Castellazzi, A., & Daliento, S. (2023, July). SiC MOSFETs Biased CV Curves: A Temperature Investigation. In *Materials Science Forum* (Vol. 1091, pp. 31-36). Trans Tech Publications Ltd.

- [32] Matacena, I., Maresca, L., Riccio, M., Irace, A., Breglio, G., & Daliento, S. (2024). Frequency Investigation of SiC MOSFETs CV Curves with Biased Drain. Solid State Phenomena, 360, 145-149.

- [33] Matacena, I., Maresca, L., Riccio, M., Irace, A., Breglio, G., Castellazzi, A., & Daliento, S. (2022, July). SiC/SiO 2 interface traps effect on SiC MOSFETs Gate capacitance with biased Drain. In 2022 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA) (pp. 1-5). IEEE.