# Achieving Low $D_{it}$ (~5×10<sup>10</sup>eV<sup>-1</sup>cm<sup>-2</sup>), Competitive $J_G$ (~ 5×10<sup>-10</sup> A cm<sup>-2</sup>) Performance and Enhanced Post-Stress Flatband Voltage Stability Using Deposited Oxide

Submitted: 2024-09-20

Revised: 2025-08-28

Online: 2025-09-12

Accepted: 2025-08-28

Umesh Chand<sup>1,a\*</sup>, Chien Yu-Chieh<sup>1,b</sup>, Abdul Hannan Yeo<sup>1,c</sup>, Voo Qin Gui Roth<sup>1,d</sup>, Shiv Kumar<sup>1,e</sup>, Akhil Ranjan<sup>1,f</sup>, Binni Varghese<sup>1,g</sup>, Weijie Wang<sup>1,h</sup>, Pavan Vudumula<sup>1,i</sup>, Tamara Fidler<sup>2,j</sup>, Patrick Schmid<sup>2,k</sup>, Mario Saggio<sup>3,l</sup>, Maurizio Castorina<sup>3,m</sup>, Marco Camalleri<sup>3,n</sup>, Jia Xie<sup>4,o</sup>, Gong Xiao<sup>4,p</sup>, Surasit Chung<sup>1,q</sup>, Lakshmi Kanta Bera<sup>1,r</sup>, Navab Singh<sup>1,s</sup>, Yeo Yee Chia<sup>1,t</sup>

<sup>1</sup>Institute of Microelectronics (IME), Agency for Science, Technology and Research (A\*STAR), Singapore 138634

> <sup>2</sup>Centrotherm International AG, Blaubeuren, Germany <sup>3</sup>STMicroelectronics, Singapore & Catania, Italy <sup>4</sup>National University of Singapore, Singapore

**Keywords:** Deposited Oxide, Interface Trap Density, Flat Band Voltage, and Reliability.

**Abstract.** In this work, we propose and experimentally validate a novel approach to achieve superior interface properties of the SiO<sub>2</sub>/SiC MOS capacitors through a low-temperature oxide deposition technique for gate dielectric followed by a nitridation process. Low interface trap density ( $\sim 5 \times 10^{10} \, \text{eV}^{-1} \text{cm}^{-2}$ ), robust flat-band voltage stability under positive bias stress, and decent leakage current density ( $J_G \sim 5 \times 10^{-10} \, \text{A cm}^{-2}$ ) can be unambiguously verified after nitric oxide (NO) gas post-deposition annealing.

#### Introduction

Silicon carbide (SiC) power MOSFETs are a key enabling technology in high-efficiency power electronics applications, particularly in systems requiring high voltage, high temperature, and high switching frequency. Despite their promise, one of the primary challenges SiC MOSFETs faces is their inherently low channel mobility, which limits overall device performance[1,2]. This issue is largely attributed to the high interface trap density (Dit) at the SiO<sub>2</sub>/SiC interface, primarily caused by carbon-related defects formed during the high-temperature oxidation process to create the gate dielectric layer [2,3]. These defects introduce unwanted energy states within the bandgap, which act as traps, reducing the mobility of carriers and thereby degrading the on-state performance of the device.

Various strategies have been explored to mitigate these challenges, including modifications to the oxidation process and post-oxidation annealing treatments. Traditional oxidation methods at high temperatures often result in significant carbon contamination at the SiC interface, increasing the density of interface traps. Low-temperature deposition techniques have recently emerged as a promising alternative. These methods offer better control over the interface properties, reducing carbon-related defects and thus improving channel mobility [4,5]. However, despite the advantages,

the precise impact on long-term device reliability and performance remains an open area of research. A deeper understanding of the SiO<sub>2</sub>/SiC interface engineering under these conditions is crucial to unlocking the full potential of SiC MOSFETs.

In this work, we explore the effectiveness of a low-temperature deposited oxide as a gate dielectric in mitigating interface-related challenges in SiC MOSFET technology. Our results show that the deposited oxide approach yields a minimal  $D_{\rm it}$  of  $\sim 5\times10^{10}~{\rm eV^{-1}cm^{-2}}$ , excellent device-to-device uniformity, decent leakage current density ( $J_{\rm G}$ ), and superior flat-band voltage stability ( $V_{\rm FB}$ ) under positive bias stress.

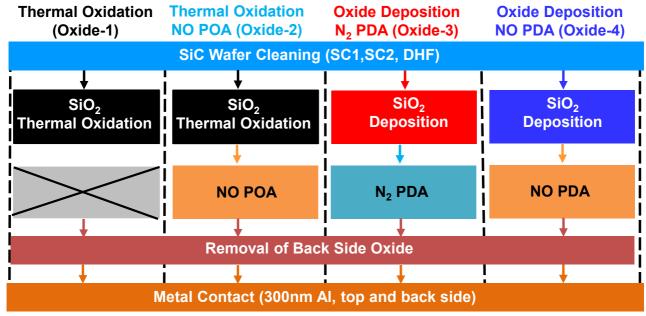

Fig. 1. Fabrication process flow for the SiO<sub>2</sub>/SiC MOS capacitors.

#### **Result and Discussion**

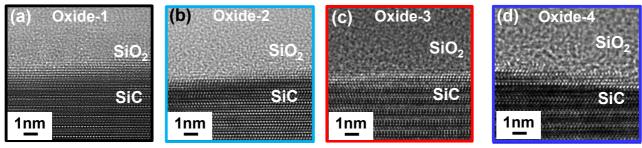

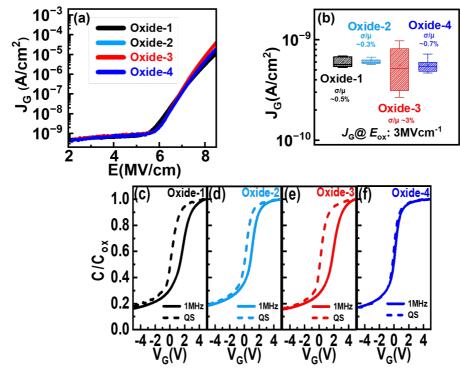

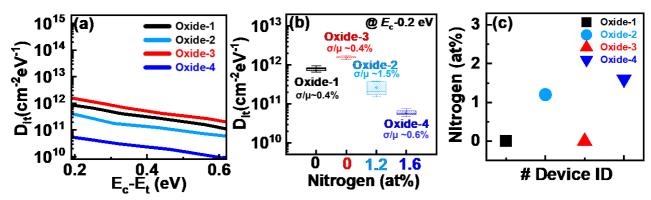

SiO<sub>2</sub>/SiC MOS capacitors were fabricated on a highly doped n-type 4° off-cut (0001) 4H-SiC substrate, with a 10  $\mu$ m thick nitrogen-doped homo-epilayer. Key aspects of the process flow are illustrated in Fig. (1). High-resolution transmission electron microscopy (HRTEM) images were obtained for all the samples to investigate the presence of an additional layer at the SiO<sub>2</sub>/SiC interface following post-oxidation/deposition annealing (POA/PDA). A sharp interface can be seen between SiO<sub>2</sub> and SiC [Fig. 2(a-b)]. To access device yield and uniformity, we randomly selected 15 devices of the same die and measured  $J_G$  [Fig. 3(a)]. The tight statistical distribution of  $J_G$  for randomly selected devices is shown in Fig. 3(b). Capacitance-voltage (*C-V*) measurement was conducted to investigate the impact of different methods on the SiO<sub>2</sub>/SiC interface [Fig. 3(c-f)]. The oxide-4 devices significantly reduce  $D_{it}$  to ~  $5\times10^{10}$  eV<sup>-1</sup>cm<sup>-2</sup> [Fig. 4(a)], which may be attributed to the effective mitigation of carbon-related defects in deposited oxide, and the incorporation of nitrogen may further passivate dangling bonds at the SiO<sub>2</sub>/SiC interface after NO POA. The tight distribution with small coefficient of variation ( $\sigma/\mu$ ) is observed for  $D_{it}$  [Fig. 4(b)]. X-ray photoelectron spectroscopy (XPS) study supported the existence of a slightly nitrogen-rich SiC surface after NO POA/PDA [Fig. 4(c)].

Fig. 2. (a-d) Cross-sectional TEM of the SiO<sub>2</sub>/SiC interface for all the samples.

**Fig. 3.** (a)  $J_G$  - $V_G$  for the SiC/SiO<sub>2</sub> MOS capacitors and (b) statistical distribution of  $J_G$  for randomly selected devices and (c-f) quasi static and 1 MHz C–V curves of the SiO<sub>2</sub>/SiC MOS capacitors.

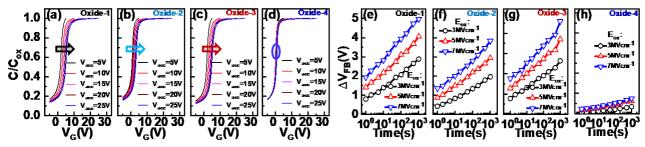

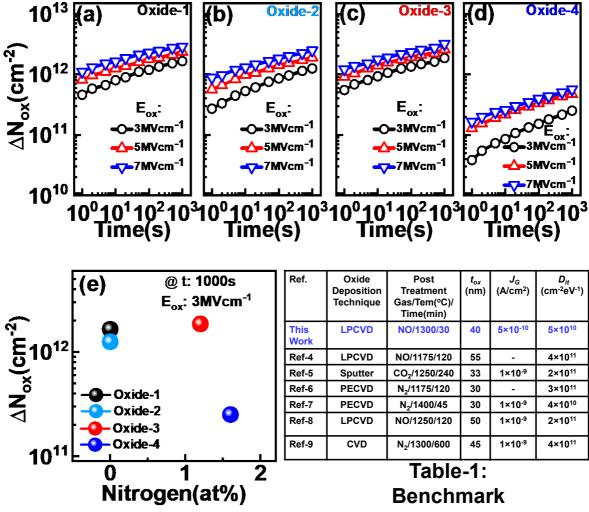

Next, the C-V measurements were repeated from -5 V to various accumulation voltages from 5 V to 25 V [Fig. 5(a-d)] to investigate the effect of high accumulation voltage on flat-band ( $V_{\rm FB}$ ) stability. The improved  $V_{\rm FB}$  stability for the oxide-4 devices could be due to the reduction of interface defects and near interface traps at the SiO<sub>2</sub>/SiC interface. Furthermore, we examined the  $V_{\rm FB}$  stability by conducting a positive bias stress test. The oxide field ( $E_{\rm ox}$ ) is applied according to industry guidelines to ensure accurate and reliable testing procedures [10]. A constant voltage stress corresponding to  $E_{\rm ox}$  values of 3, 5, and 7 MV/cm was applied for a duration of up to  $10^3$  s [Fig. 5(e-h)]. The bulk trap density ( $\Delta N_{\rm ox}$ ) extracted as a function of bias stress time with various  $E_{\rm ox}$  values of 3, 5, and 7 MV/cm shown in Fig. 6(a-d). The oxide-4 scheme device manifests superior  $V_{\rm FB}$  stability against bias stress with the lowest extracted  $\Delta N_{\rm ox}$ .

**Fig. 4.** (a) energy distribution of  $D_{it}$  estimated by the high-low method [2], (b) the distribution of  $D_{it}$  extracted at around  $E_c$ -0.2 eV, and (c) nitrogen concentration plotted for for all samples.

Fig. 5. (a-d) C-V curves with different accumulation voltages of the SiO<sub>2</sub>/SiC MOS capacitors and (e-h)  $\Delta V_{\rm FB}$  as a function of bias stress time with various  $E_{\rm ox}$  of 3, 5, and 7 MV/cm.

This can be attributed to the minimization of carbon-related defects through the deposited oxide approach, in which the trap states are further reduced by NO-PDA. Finally, we benchmark the  $D_{it}$  and  $J_G$  of our devices with previously reported deposited oxide SiC devices (Table I). It is reasonable to conclude that the oxide-4 device in this study has achieved the lowest  $J_G$  ( $\sim 5 \times 10^{-10}$  A cm<sup>-2</sup>) and a satisfactory  $D_{it}$  value ( $\sim 5 \times 10^{10}$  eV<sup>-1</sup>cm<sup>-2</sup>).

**Fig. 6.** (a-d)  $\Delta N_{\rm ox}$  as a function of bias stress time with various  $E_{\rm ox}$  field of 3, 5, and 7 MV/cm. (e) change in  $\Delta N_{\rm ox}$  plotted as a function of nitrogen concentration and Table-1 Benchmark of this work with reported work.

## Conclusion

In summary, our deposited gate oxide on SiC with NO-POA had produced low  $D_{it}$  and led to a significant enhancement in MOS capacitor device performance and reliability such as superior  $V_{FB}$  stability under positive bias stress.

## Acknowledgement

This work was supported by the Science and Engineering Research Council of A\*STAR (Agency for Science, Technology, and Research) Singapore, under Grant No. A20H9a0242.

## References

- [1] T. Kimoto and H. Watanabe, Appl. Phys. Express 13, 120101 (2020).

- [2] T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices, and Applications (Wiley, New York, 2014).

- [3] U. Chand et al., International Conference on Silicon Carbide and Related Materials (ICSCRM), (2023).

- [4] P. Fiorenza, et al., Material Science in Semiconductor Processing, 169, 107866 (2023).

- [5] T.H. Kil, et al., AIP Advance, 13, 115304 (2023).

- [6] M. Yakut, et al., ICSCRM, (2023).

- [7] K. Tachiki, et al., Applied Physics Express, 14,031001 (2021).

- [8] M. Lim, et al., ICSCRM, 535-540, (2019).

- [9] S. Asaba, et al., ICSCRM, 924, 457-460 (2017).

- [10] D. A. Gajewski et al., ICSCRM, 179-186 (2023).