# Device Performance and Reliability of SiC CMOS up to 400°C

Submitted: 2024-09-21

Revised: 2025-08-02

Online: 2025-09-12

Accepted: 2025-08-04

Emran Ashik<sup>1,a\*</sup>, Sundar B Isukapati<sup>2,b</sup>, Hua Zhang<sup>3,c</sup>, Tianshi Liu<sup>3,d</sup>, Utsav Gupta<sup>3,e</sup>, Adam J Morgan<sup>2,f</sup>, Veena Misra<sup>1,g</sup>, Woongje Sung<sup>2,h</sup>, Ayman Fayed<sup>3,i</sup>, Anant K Agarwal<sup>3,j</sup>, Bongmook Lee<sup>1,4,k</sup>

<sup>1</sup>Department of ECE, North Carolina State University, Raleigh, NC, USA <sup>2</sup>College of Nanoscale Sci. and Eng., SUNY University at Albany, NY, USA <sup>3</sup>Department of ECE, Ohio State University, Columbus, OH, USA <sup>4</sup>College of Eng., SUNY Polytechnic Institute, Utica, NY, USA

<sup>a</sup>ekashik@ncsu.edu, <sup>b</sup>SIsukapati@sunypoly.edu, <sup>c</sup>zhang.8230@buckeyemail.osu.edu, <sup>d</sup>liu.2876@buckeyemail.osu.edu, <sup>e</sup>gupta.1121@buckeyemail.osu.edu, <sup>f</sup>adam.morgan@nomispower.com, <sup>g</sup>vmisra@ncsu.edu, <sup>h</sup>wsung@albany.edu, <sup>i</sup>fayed.1@osu.edu, <sup>j</sup>agarwal.334@osu.edu, <sup>k</sup>leeb1@sunypoly.edu

**Keywords:** MOSFET, CMOS, Field Effect Mobility, Threshold Voltage, Chemical Vapor Deposition, Transfer Characteristics, Interface Traps, Reliability, BTI

Abstract. This study evaluates the performance and reliability of SiC n- and p-MOSFETs across a temperature range from room temperature up to 400°C, focusing on field effect (FE) mobility and threshold voltage variations under high thermal and bias stress conditions. By analyzing the variations in field effect mobility and threshold voltage under different stress conditions, our study illustrates distinct behaviors between devices with thermally grown oxides and those with chemical vapor deposited (CVD) oxide layers, underscoring significant differences in long term performance. Results indicate that while n-MOSFETs maintain threshold voltage shifts below 3% and exhibit robust characteristics up to 400°C, p-MOSFETs exhibit permanent threshold voltage shifts of up to 10% and mobility reductions of 15% particularly above 300°C DC stress. The 2 nm ultrathin thermal (UT) SiO<sub>2</sub> followed by 40nm CVD SiO<sub>2</sub>, outperform thermal oxides, sustaining less degradation in mobility and less shift in threshold voltage under bias temperature instability (BTI) conditions at voltages up to ±25V and temperatures as high as 400°C. This research advances SiC CMOS technology by confirming that SiC n-MOSFETs are ready for high-temperature circuit applications, while highlighting the need for further improvement in p-MOSFETs to enhance their reliability under extreme conditions.

#### Introduction

Silicon carbide (SiC) has accumulated significant attention in the semiconductor industry due to its outstanding physical and electronic properties [1]. As a wide bandgap material, SiC is inherently capable of operating at higher electric fields, power levels, and thermal environments compared to traditional silicon-based devices. This robustness makes SiC an ideal candidate for power electronics, particularly in applications requiring high efficiency and reliability under extreme conditions such as in electric vehicles, aerospace, and industrial power systems [2], [3]. SiC distinguishes itself from other wide-bandgap semiconductors by allowing the straightforward growth of gate oxides in a similar manner to silicon. This key advantage positions SiC as a superior choice for applications requiring wide bandgap materials due to its ease of fabrication and enhanced device performance. Despite its significant advantages, SiC technology, particularly in metal-oxide-semiconductor field-effect transistors (MOSFETs), encounters notable challenges that can impact device performance and reliability. One such challenge is the poor interface quality between the SiC substrate and the gate oxide. The interface quality is crucial because it affects the mobility of charge carriers and the stability of the device's electrical characteristics under different operating conditions. Imperfections at this interface, such as traps and defects formed mainly due to carbon cluster formations and oxygen

vacancies, lead to increased electron scattering, reduced carrier mobility, and fluctuations in threshold voltage, which in turn compromise the efficiency and lifespan of the MOSFET [4], [5], [6].

Due to these imperfections, high-temperature operations can accelerate the failure of SiC MOSFETs, worsening issues like increased leakage currents and dielectric breakdown [7]. One of the critical issues in SiC MOSFETs is the reliability of the gate oxide layer when subjected to temperatures exceeding 150°C, a standard threshold in power electronics [8], particularly regarding the degradation mechanisms that impact their long-term stability and performance. The reliability concerns arise from the significant presence of traps at the SiO<sub>2</sub>/SiC interface. Strategies such as enhanced passivation layers and thermally stable contact materials are critical for maintaining device performance and longevity under these conditions. Among the reliability concerns, bias temperature instability (BTI), particularly negative BTI, poses a significant challenge for SiC MOSFETs, manifesting as large shifts in threshold voltage (V<sub>TH</sub>) [9], [10], [11]. These shifts are exacerbated at high temperatures, leading to degraded device performance and lifetime [7]. The underlying cause often ties back to the quality of the gate oxide. Thermally grown silicon dioxide (SiO<sub>2</sub>) on SiC tends to exhibit a higher density of interface traps (D<sub>it</sub>), which are accentuated under thermal stress and electric bias, further compounding reliability issues [12], [13].

This paper represents the behavior of n- and p-type SiC MOSFETs across a wide temperature range, from room temperature up to 400°C, with a particular focus on mobility and threshold voltage variations. By conducting a comparative study of devices with thermally grown oxides versus those with CVD oxides, it highlights distinct performance differences under various stress conditions. Our results underscore the superior stability and performance of deposited oxide layers compared to traditional thermal oxides, particularly in high-temperature applications. It also provides new findings on how n- and p-MOSFETs respond differently to temperature-related stress, with n-MOSFETs showing less change in performance under these conditions, offering insights for improving SiC CMOS for extreme environment.

#### **Fabrication Process**

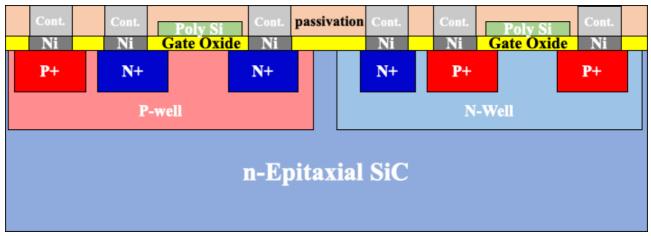

The fabrication of n- and p-channel MOSFETs was conducted at Analog Devices Inc., utilizing 6-inch epitaxially grown SiC wafers. The implanted channels were doped with nitrogen and aluminum at concentrations of  $4 \times 10^{16}$  cm<sup>-3</sup> and  $2 \times 10^{16}$  cm<sup>-3</sup> for n- and p-channels, respectively. A visual overview of the design is illustrated in Fig. 1. This study investigates three different gate oxide conditions: a standard thermally grown oxide and two CVD oxides, which were grown to thicknesses of 20 nm and 40 nm using ADI's established CVD method. Additionally, a 2 nm ultrathin thermal oxidation step was applied prior to the CVD process to enhance nucleation. More comprehensive details of the fabrication process are available in [9], [14].

**Fig. 1.** The cross-section of the n- and p-channel MOSFETs is selectively illustrated that relates to the key findings of this study. For a comprehensive view and detailed analysis of the full cross-section, refer to the documentation presented in [9].

## **Characterization Method**

Oxide capacitances were extracted by driving the device into accumulation to determine the effective oxide thickness (EOT). For all transfer characteristics,  $\pm$  0.1 V was applied to drain while source and substrate was at 0 V. All devices have 30  $\mu$ m channel length and 30  $\mu$ m channel width to keep W/L=1 and avoid any geometry effect. The peak FE mobility was extracted using,

$$\mu_{FE(peak)} = \frac{\max\left(\frac{\delta I_D}{\delta V_{GS}}\right)}{V_{DS}C'_{OX}} \tag{1}$$

Where, drain current =  $I_D$ , gate to source voltage =  $V_{GS}$ , drain to source voltage= $V_{DS}$ , oxide capacitance in accumulation per unit area =  $C'_{OX}$  (in F/cm<sup>2</sup>). To perform BTI characteristics, stress-sense-stress technique was used [11]. The threshold voltage was characterized using the intercept of maximum slope via linear extrapolation of  $I_D$  vs  $V_{GS}$  characteristics [15]. In order to minimize the time between two "stress" stage the "current level" is chosen from the drain current at threshold voltage and voltage shift was observed to achieve that "current level" is considered as  $V_{TH}$  shift for BTI measurement. This setup enabled the application of very low voltage stress for a very short time to "sense" the threshold voltage shift after each "stress" step.

#### **Results and Discussions**

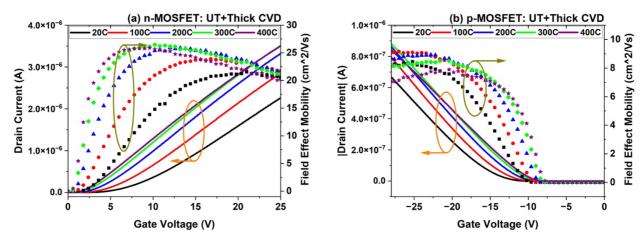

**Device Characteristics vs. Temperature.** Fig. 2 illustrates the transfer characteristics of n- and p-channel MOSFETs with gate oxide formed using ultrathin thermal SiO<sub>2</sub> and thick CVD grown SiO<sub>2</sub> across a range of temperatures. As temperatures rise from room temperature (20°C) to 400°C, there is a decrease in the threshold voltage, attributed to the enhanced thermal voltage (\$\textit{\ellipsi}\$) which boosts the inversion charge density in the channel of both n- and p-MOSFETs [16]. FE mobility in SiC predominantly increases with temperature due to mobility predominantly limited by Coulombic scattering [9], [17]. Lattice damage during implantation, incomplete recovery after activation annealing, surface roughness and large density of traps at/near interface provide significant amount of scattering centers for charge carriers. Initially, field effect (FE) mobility increases with temperature. As the device characteristics are analyzed beyond this point, the influence of Coulombic scattering diminishes with increasing temperature, while phonon scattering becomes more prevalent, acting as main constraints on mobility at elevated temperatures. As a result, the mobility shows a downward trend for both n- and p-channel MOSFETs as temperatures rise, with the decline starting around 300°C for n-MOSFETs and 130°C for p-MOSFETs. The complex interplays of different scattering mechanisms shapes the device performances at different temperatures.

**Fig. 2.** Transfer characteristics of (a) n-channel and (b) p-channel MOSFETs with temperature ranging from 20°C to 400°C. Both MOSFETs have ultrathin thermal (UT) SiO<sub>2</sub>/40 nm thick CVD grown SiO<sub>2</sub>.

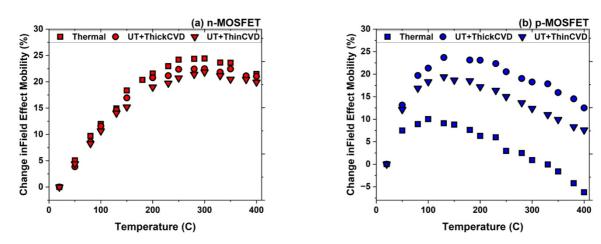

To gain a deeper understanding of how device mobility is influenced by temperature, the field effect (FE) mobility across different gate oxide conditions is extracted in Fig. 3. These conditions include a 50 nm thermal oxide, 2 nm UT SiO<sub>2</sub> + 40 nm CVD SiO<sub>2</sub>, and 2 nm UT SiO<sub>2</sub> + 20 nm CVD SiO<sub>2</sub>. The measurement temperature was varied from 20°C to 400°C. The FE mobility was derived using Eq. 1 and subsequently normalized to the corresponding room temperature mobility value to ensure consistency in comparison.

The variance in temperature behavior between n- and p-MOSFETs can be largely attributed to the fundamental scattering mechanisms affecting carrier mobility [16]. As temperature rises, charge carriers gain kinetic energy, enhancing their ability to overcome the potential barriers of ionized impurities. This results in a reduced probability of carrier scattering by these impurities, thereby increasing the Coulombic scattering-limited mobility. However, alongside this increase, temperature also amplifies lattice vibrations within the semiconductor material, enhancing phonon scattering. Phonon scattering involves the interaction of charge carriers with the vibrating atoms of the lattice, which increases with temperature due to greater vibrational energy. As a consequence, phonon scattering becomes a significant limitation on mobility at higher temperatures, ultimately leading to the observed decrease in mobility as temperatures approach and exceed the transition point. From Matthiesen's rule,

$$\mu_{total} = \frac{1}{\frac{1}{\mu_C} + \frac{1}{\mu_L} + \dots} \tag{2}$$

where,  $\mu_C$  and  $\mu_L$  are coulombic scattering limited and phonon scattering limited mobility respectively. In SiC MOSFETs with SiO<sub>2</sub> as gate dielectric, the FE mobility is limited by coulombic scattering with  $\mu_C$  being much less than  $\mu_L$ . This is due to traps at SiC/SiO<sub>2</sub> interface [4]. With the increase in temperature,  $\mu_C$  increases which gives rise to the effective mobility in Matthiesen's rule (Eq. 2). However,  $\mu_L$  decreases with increase in temperature due to increased vibrational energy from higher temperature which eventually overturns the total mobility dependent solely on  $\mu_L$ .

**Fig. 3.** Percentage change in FE mobility vs temperature for (a) n-channel and (b) p-channel MOSFETs.

For n-MOSFETs, there is a continuous increase in peak mobility up to a temperature of 250-300°C, at which point the mobility begins to decrease. This peak and subsequent decline mark a transition from mobility being primarily limited by Coulombic scattering to being limited by phonon scattering and the "transition point" indicates the temperature at which phonon interactions become sufficiently prominent to overshadow the effects of Coulombic scattering. For p-MOSFETs, however, this transition occurs at a significantly lower temperature of 100-130°C. This is due to the charge carriers (holes) in the p-MOSFETs have significantly heavier effective masses compared to the charge carriers (electrons) in n-MOSFETs [1]. The carriers with heavier effective mass have more energy at higher temperature to overcome the barrier for coulombic scattering centers which diminishes the effect of coulombic scattering quicker than lighter counterparts. Hence, the p-MOSFETs have lower

"transition" temperature compared to n-MOSFET. Furthermore, the mobility vs. temperature results for p-MOSFETs are very different for different gate oxide conditions compared to n-MOSFETs. The traps near conduction band are very much optimized over the last few decades with different annealing and POA while there is limited research on traps near valence band and the difficulty in extraction of traps near valence band. The difference in mobility change vs. temperature (Fig. 3 (b)) can be attributed to the differences in traps distribution near the valence band.

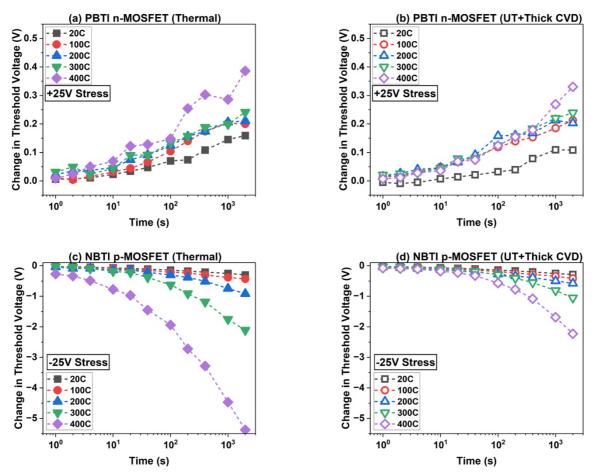

BTI vs. Temperature. BTI analysis is not only critical to diagnose the reliability and longevity of MOSFETs under combination of electrical and thermal stress but also provides crucial information about gate oxide quality and interface traps. A stress bias is applied at the gate while source, drain and substrate are grounded. The threshold voltage shifts due to injection of charges into the dielectric traps located at or near the oxide/semiconductor interface with different stress time. Positive and negative bias temperature instability measurements were conducted on both n- and p-channel MOSFETs. In order to contrast the results, the thermal oxide condition was characterized alongside the UT+CVD oxide condition. Fig. 4 shows the PBTI and NBTI shift of threshold voltages with ±25V (4MV/cm) stress and the temperature was varied from room temperature to 400°C.

**Fig. 4.** BTI characteristics of n- and p-MOSFETs at various temperature with ±25 V DC stress. For each measurement, the "current level" was chosen before applying any stress at corresponding temperature.

In Fig. 4 (a) and (b), The PBTI shifts for both thermal and deposited oxides, respectively, indicate that both types of oxide are effectively optimized. The traps near the conduction band are passivated sufficiently to prevent substantial shift in the threshold voltage. As the temperature increases, the shift in  $V_{TH}$  also increases. Even though same gate bias was applied to stress the dielectrics, the reduction in threshold voltage at higher temperature causes an increase in the effective electric field. As a result, the  $V_{TH}$  shifts are slightly larger at higher temperature. The effective electric field can be extracted using the following equation-

$$E_{eff} = \frac{V_{GS} - V_{TH}}{EOT} \tag{3}$$

where,  $E_{\rm eff}$  is the electric field that acts on the oxide and EOT is the effective oxide thickness. The electric field applied at the gate has two-fold role in MOS structure; one part acting upon necessary band bending to form the channel which essentially is equal to  $\frac{V_{TH}}{EOT}$  whereas, the rest acts on the gate oxide. Few data points are off from the trend which indicates the charged mobile ion movement in gate oxide which can be ignored from the analysis. Nevertheless, the shift in  $V_{TH}$  for both types of oxides is less than 5% even with measurement temperature as high as  $400^{\circ}$ C.

In Fig. 4 (c) and (d), we observe significant threshold voltage shifts in p-MOSFETs under -25V bias stress across different temperatures, more so than in n-MOSFETs. Due to the higher initial threshold voltage in p-MOSFETs, configured by using the same n+ poly-Si gate material and the presence of un-passivated interface traps near the valence band, the effective gate oxide electric field is much smaller compared to n-MOSFETs (-2.2 MV/cm for thermal oxide and -2.7 MV/cm for deposited oxide). The pronounced shift in p-MOSFETs is linked to the un-passivated carbon clusters and oxygen vacancies at the interface [12]. Additionally, a secondary slope becomes evident more quickly at higher temperatures, indicating an accelerated activation of defect states, which impacts the NBTI behavior significantly.

The prolonged bias application could activate deep-level traps, resulting in a distinct secondary slope in BTI studies [9]. These BTI characteristics include an increase in interface trap density ( $D_{ii}$ ), a reduction in field effect (FE) mobility, and a rise in threshold voltage, which notably do not revert even after the stress is removed. Higher temperatures increase band bending due to increased thermal voltage ( $\emptyset_i$ ) and facilitate the thermal generation of carriers. The band bending pushes more traps closer to the valence band at the gate oxide interface, which in turn activates additional deep-level traps under prolonged stress. Consequently, this process precipitates the emergence of the secondary slope earlier in the BTI timeline, thereby affirming the complex interplay among temperature, bias stress, and trap activation in p-MOSFETs. Since it has already established that thermal oxide has more traps near valence band compared to our novel deposited oxide, the secondary slope of thermal oxide starts at lower temperature than that of deposited oxide.

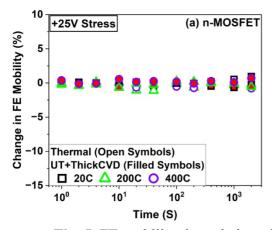

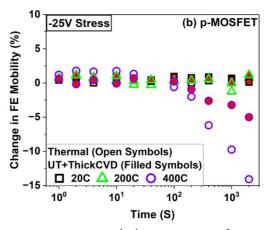

To complete our analysis, FE mobility was extracted following each BTI stress evaluation, with Fig. 5 demonstrating the percentage change in FE mobility in relation to its initial state. While n-MOSFETs showed a negligible change in mobility (<1.5%) at and up to 400°C across both oxide types, p-MOSFETs registered more substantial declines: 5% for deposited oxides and 15% for thermal oxides at the same temperature. This marked degradation in thermal oxides correlates with their earlier activation of secondary slopes and a higher presence of interface traps near the valence band. This further establishes the enhanced stability and efficiency of our newly developed deposited oxides over conventional thermal oxides.

**Fig. 5.** FE mobility degradation after BTI measurement at varied temperature for (a) n-MOSFET and (b) p-MOSFET with thermal and deposited oxides.

## Conclusion

In this study, n- and p-MOSFETs fabricated on 6-inch 4H-SiC wafers demonstrated distinct behaviors across different gate oxide conditions, from room temperature up to 400°C. Devices with ultrathin thermal combined with CVD SiO<sub>2</sub> exhibited superior field effect mobility and stability compared to those with traditional thermal oxides, particularly under high-temperature conditions. Bias temperature instability (BTI) tests revealed minimal threshold voltage shifts for n-MOSFETs under extreme thermal stress, highlighting their durability, whereas p-MOSFETs faced significant permanent threshold voltage shifts and mobility reductions above 300°C, pointing to un-passivated deep level traps within the bandgap near the valence band. These findings suggest the necessity for enhanced passivation strategies, particularly near the valence band, to improve the performance and reliability of SiC MOSFETs, and demonstrate that deposited oxide stacks offer a more reliable alternative to traditional thermal oxides for high temperature applications.

# Acknowledgement

The work was funded by Advanced Research Projects Agency-Energy (ARPA-E) U.S. Department of energy, under Award Number DE-AR0001028

## References

- [1] W. J. Choyke and G. Pensl, "Physical Properties of SiC," *MRS Bull.*, vol. 22, no. 3, pp. 25–29, Mar. 1997, doi: 10.1557/S0883769400032723.

- [2] R. R. Siergiej *et al.*, "Advances in SiC materials and devices: an industrial point of view," *Mater. Sci. Eng. B*, vol. 61–62, pp. 9–17, Jul. 1999, doi: 10.1016/S0921-5107(98)00438-3.

- [3] M. Alexandru *et al.*, "SiC Integrated Circuit Control Electronics for High-Temperature Operation," *IEEE Trans. Ind. Electron.*, vol. 62, no. 5, pp. 3182–3191, May 2015, doi: 10.1109/TIE.2014.2379212.

- [4] G. Pensl *et al.*, "Traps at the SiC/SiO2-Interface," *MRS Online Proc. Libr. OPL*, vol. 640, p. H3.2, Jan. 2000, doi: 10.1557/PROC-640-H3.2.

- [5] V. V. Afanas'ev, "Electronic properties of SiO2SiC interfaces," *Microelectron. Eng.*, vol. 48, no. 1, pp. 241–248, Sep. 1999, doi: 10.1016/S0167-9317(99)00379-2.

- [6] E. Pippel, J. Woltersdorf, H. Ö. Ólafsson, and E. Ö. Sveinbjörnsson, "Interfaces between 4H-SiC and SiO2: Microstructure, nanochemistry, and near-interface traps," *J. Appl. Phys.*, vol. 97, no. 3, p. 034302, Dec. 2004, doi: 10.1063/1.1836004.

- [7] D. J. Lichtenwalner *et al.*, "Accelerated Testing of SiC Power Devices," in *2020 IEEE International Integrated Reliability Workshop (IIRW)*, Oct. 2020, pp. 1–6. doi: 10.1109/IIRW49815.2020.9312873.

- [8] A. Christou, Reliability of High Temperature Electronics. RIAC, 1996.

- [9] E. K. Ashik *et al.*, "Bias Temperature Instability on SiC n- and p-MOSFETs for High Temperature CMOS Applications," in *2022 IEEE International Reliability Physics Symposium (IRPS)*, Mar. 2022, p. 3B.4-1-3B.4-8. doi: 10.1109/IRPS48227.2022.9764565.

- [10] A. J. Lelis, R. Green, D. B. Habersat, and M. El, "Basic Mechanisms of Threshold-Voltage Instability and Implications for Reliability Testing of SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 316–323, Feb. 2015, doi: 10.1109/TED.2014.2356172.

- [11] R. Green, A. Lelis, and D. Habersat, "Threshold-voltage bias-temperature instability in commercially-available SiC MOSFETs," *Jpn. J. Appl. Phys.*, vol. 55, no. 4S, p. 04EA03, Mar. 2016, doi: 10.7567/JJAP.55.04EA03.

- [12] R. W. Kee, K. M. Geib, C. W. Wilmsen, and D. K. Ferry, "Interface characteristics of thermal Si02 on SiC," *J. Vac. Sci. Technol.*, vol. 15, no. 4, pp. 1520–1523, Jul. 1978, doi: 10.1116/1.569779.

- [13] T. E. Rudenko, I. N. Osiyuk, I. P. Tyagulski, H. Ö. Ólafsson, and E. Ö. Sveinbjörnsson, "Interface trap properties of thermally oxidized n-type 4H–SiC and 6H–SiC," *Solid-State Electron.*, vol. 49, no. 4, pp. 545–553, Apr. 2005, doi: 10.1016/j.sse.2004.12.006.

- [14] S. B. Isukapati *et al.*, "Monolithic Integration of Lateral HV Power MOSFET with LV CMOS for SiC Power IC Technology," in *2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, May 2021, pp. 267–270. doi: 10.23919/ISPSD50666.2021.9452235.

- [15] L. Dobrescu, M. Petrov, D. Dobrescu, and C. Ravariu, "Threshold voltage extraction methods for MOS transistors," in 2000 International Semiconductor Conference. 23rd Edition. CAS 2000 Proceedings (Cat. No.00TH8486), Oct. 2000, pp. 371–374 vol.1. doi: 10.1109/SMICND.2000.890257.

- [16] Y. Tsividis, Operation and Modeling of the Mos Transistor (The Oxford Series in Electrical and Computer Engineering). USA: Oxford University Press, Inc., 2004.

- [17] V. Uhnevionak *et al.*, "Comprehensive Study of the Electron Scattering Mechanisms in 4H-SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 62, no. 8, pp. 2562–2570, Aug. 2015, doi: 10.1109/TED.2015.2447216.