ISŚN: 1662-9795, Vol. 470, pp 201-206 doi:10.4028/www.scientific.net/KEM.470.201

© 2011 The Author(s). Published by Trans Tech Publications Ltd, Switzerland.

# Capture/Emission Processes of Carriers in Heterointerface Traps Observed in the Transient Charge-Pumping Characteristics of SiGe/Si-Hetero-Channel pMOSFETs

Toshiaki Tsuchiya<sup>1a</sup>, Keiichi Yoshida<sup>1b</sup>, Masao Sakuraba<sup>2c</sup> and Junichi Murota<sup>2d</sup>

<sup>1</sup>Interdisciplinary Faculty of Science and Engineering, Shimane University, 1060 Nishikawatsu, Matsue 690-8504, Japan <sup>2</sup>Research Institute of Electrical Communication, Tohoku University,

2-1-1 Katahira, Aoba-ku, Sendai 980-8577, Japan

<sup>a</sup>tsuchiya@ecs.shimane-u.ac.jp, <sup>c</sup>sakuraba.masao@myad.jp,

dmurota@riec.tohoku.ac.jp

Keywords: heterointerface trap, carrier capture process, charge pumping, MOSFET

**Abstract.** Transient phenomena related to carrier capture/emission processes in interface traps were observed in the the charge pumping (CP) characteristics of SiGe/Si hetero-channel pMOSFETs, i.e., the CP characteristics were found to depend on the on/off time of the gate pulse. From these observations, time constants for the processes both in SiGe/Si heterointerface traps and in gate-oxide interface traps were derived. The time constant is considered to depend on the energy level of the interface traps that are present over a wide range within the energy gap. Therefore, these phenomena provide an interesting way of evaluating the discrete energy levels of interface traps in nanometer-scale devices containing only a few traps.

# Introduction

Strained-Si and SiGe/Si hetero-CMOS structures are highly promising materials for the construction of advanced high performance Si CMOS devices [1, 2]. To exploit the advantages of SiGe/Si heterostructure effectively and to establish adequate device reliability, an understanding of the electrical properties of the hetero-interface, i.e., heterointerface traps, is an important factor.

On the other hand, as the dimensions of MOSFETs are scaled into the nanometer regime, fluctuations in device characteristics due to variations in gate length, discrete dopant fluctuations, line-edge roughness, and so on have become serious problems [3-5]. Moreover, the presence of current noise in MOSFETs has recently become a problem even in digital circuits [6]. The 1/f noise is the dominant type of noise in silicon MOSFETs, and is considered to be determined by the electronic properties at and near the gate-oxide interface. Discrete drain current fluctuations, known as random telegraph noise (RTN), are observed in MOSFETs under constant bias conditions and are considered to be caused by charge-transport fluctuations due to the capture/emission of carriers at single traps. It has been pointed out that RTN will become one of the greatest reliability issues in

scaled-down digital devices [6-11].

Therefore, the identification of traps that exist in the vicinity of the heterointerface and the gate-oxide interface will be essential for the development of future small MOS devices.

In this paper, we describe transient phenomena that have been observed in the dependence of the charge pumping characteristics upon the on/off time of the gate pulse in SiGe/Si hetero-channel pMOSFETs. These are related to the carrier capture/emission processes in SiGe/Si heterointerface traps and/or the gate-oxide interface traps, and a time constant for the process will be derived from the transient characteristics.

## **Experiments**

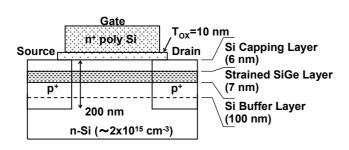

A schematic of the cross section of the SiGe/Si hetero-p-channel MOSFETs (pMOSFETs) used in this study is shown in Fig. 1. These devices were fabricated using a high-quality low-temperature epitaxially grown heterostructure incorporating a Si buffer layer, a strained SiGe layer and a Si capping layer. The heterostructure was grown in an ultraclean low-pressure chemical vapour deposition (CVD) system [12]. The deposition temperature was 750 °C for the Si buffer layer (100 nm thick), 500 °C for the strained SiGe layer (7 nm thick), and 500 °C for the Si capping layer (10 nm thick). The Ge fraction in the SiGe layer was 0.4. This was estimated using X-ray diffractometry by determining the lattice constant of a thicker relaxed SiGe layer deposited under the same deposition conditions. After forming a 700-nm-thick field oxide layer at 400 °C by CVD, a 10 nm gate oxide layer was thermally grown by wet oxidation at 700 °C. Thus, the final thickness of the Si capping layer was 6 nm. An in-situ phosphorous-doped n<sup>+</sup> polysilicon layer was deposited and patterned to form the gate, and the source and drain were formed by B<sup>+</sup> ion implantation (1.2x10<sup>15</sup>cm<sup>-2</sup> at 25 keV). The gate length and width of the MOSFETs were 1.5 and 4 μm, respectively. After the interconnection processes, a final forming gas annealing was performed at 400 °C. All of the annealing processes were performed at temperatures below 700 °C to prevent degradation of both the flatness of the heterostructure surface and the Ge profile in the channel region.

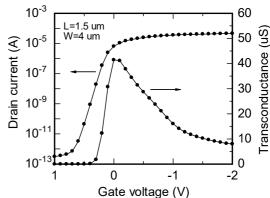

Typical electrical characteristics of the SiGe/Si hetero-pMOSFET used in this study are shown in Fig. 2.

Fig. 1 SiGe/Si-hetero-channel pMOSFET used in this study.

Fig. 2 Typical drain current and transconductance as a function of gate voltage in the SiGe/Si-hetero-channel pMOSFETs.

Charge pumping (CP) measurements [13] were performed using a gate pulse of fixed amplitude (-3 V) and a variable base level,  $V_{\rm BASE}$ , with a pulse frequency of 66~250 kHz, in the temperature range from RT to 91 K. The gate pulse configuration during the CP measurements is shown in Fig. 3.

# T<sub>p</sub>: pulse period t<sub>w</sub>: pulse width t<sub>r</sub>: rise time t<sub>r</sub>: fall time V<sub>BASE</sub>: base level V<sub>p</sub>: pulse height

Fig. 3 Gate pulse configuration during charge pumping measurements.

#### **Results and Discussions**

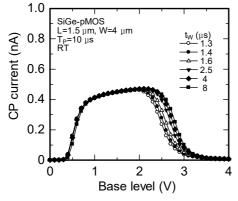

It is well known that the maximum CP current depends upon the rise time ( $t_r$ ) of the gate pulse,

even when adequate inversion and accumulation conditions are attained during the measurement, as shown in Fig. 4. This is due to decrease in the emission current from electrons in non-steady-state interface traps in the upper part of the energy band gap moving to the conduction band under the influence of the rapidly rising gate voltage [13].

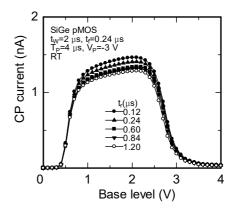

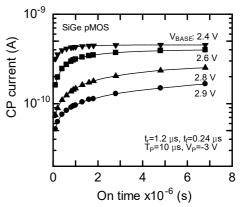

We observed another transient phenomenon in the rising portion (but not at maximum current) of the CP characteristics at room temperature (RT) [14]. The dependence of the pulse-width ( $t_W$ ), i.e.,

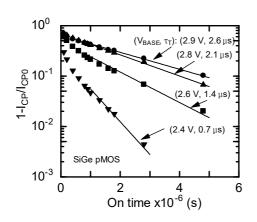

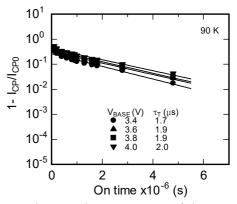

the on-time of the gate pulse, upon the CP characteristics is shown in Fig. 5. The CP currents ( $I_{\rm CP}$ ) at a given  $V_{\rm BASE}$  in the rising portion as a function of on-time are shown in Fig. 6. The current increases with increasing on-time, and shows a saturation behavior that can be described by  $I_{\rm CP} = I_{\rm CP0} [1 - \exp(t/\tau_{\rm T})]$  using a time constant  $\tau_{\rm T}$ , where  $I_{\rm CP0}$  is a saturated CP current. 1-  $I_{\rm CP}/I_{\rm CP0}$  for each value of  $V_{\rm BASE}$  as a function of on-time is shown in Fig. 7. The time constant ( $\tau_{\rm T}$ ) for each  $V_{\rm BASE}$  can be derived from Fig. 7, as indicated in the figure.

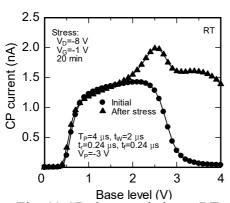

Fig. 4 Dependence of CP characteristics on the rise time of the gate pulse.

Fig. 5 Dependence of the CP characteristics in the rising portion on the pulse width, i.e., on-time of the gate pulse.

Fig. 6 CP current as a function of on-time for different base levels in the rising portion.

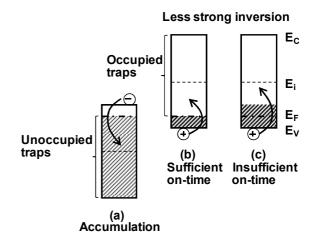

The value of  $\tau_T$  is considered to be related to the capture process of holes from the less strong inversion layer to both the gate-oxide interface traps and the heterointerface traps, as follows: Changes in the energy band diagram during this process are shown in Fig. 8. Holes trapped in the interface traps recombine with electrons coming from the accumulation layer formed while at the base level (i.e., during accumulation) as shown in Fig. 8(a), and some of the holes in the inversion layer are captured by interface traps during the on-time (i.e., during inversion) as shown in Figs. 8(b) and 8(c). However, in this case, inversion is less strong because of the rising portion in the CP characteristics, and only a small fraction of the interface traps can capture holes if the on-time is insufficient, as shown in Fig. 8(b).

We also observed similar transient behavior in the opposite rising portion of the CP characteristics, which depends upon the off-time of the gate pulse. This is considered to be related to the emission of holes from interface traps to the less strong accumulation layer. The time constants related to the emission process ( $\tau_{\text{T}}\sim 1.5-2~\mu\text{s}$ ) were derived from the dependences.

Fig. 7 Time constant of the on-time dependent CP current with base level as a parameter.

Fig. 8 Energy band diagrams explaining the on-time dependent CP characteristics, indicating capture process of holes from the less strong inversion layer to the heterointerface traps.

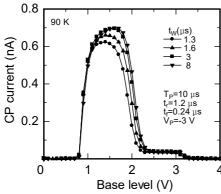

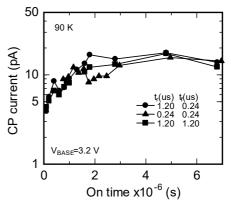

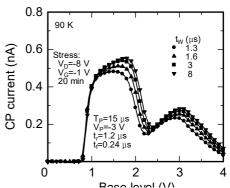

Moreover, if we perform low temperature CP measurements [15], the value of  $\tau_T$  for heterointerface traps only should be obtained. The dependence of the pulse-width ( $t_W$ ) upon the CP characteristics at 90 K is shown in Fig. 9. The plateau region seen at around  $V_{BASE}$ =2.5~3 V in Fig. 9 is the CP current due to the heterointerface traps [15]. Therefore, we can derive the time constant ( $\tau_T$ ) from the change in the CP current in the rising portion of the plateau region. The CP currents at a base level of 3.2 V in the rising portion as a function of on-time at 90 K are shown in Fig. 10. From this figure, we obtained  $\tau_T$ ~1 µs. However, since the number of heterointerface traps is small, the CP current in the rising portion at a base level of around 3.2 V in Fig. 9 is very low. Therefore, the accuracy of the obtained value of  $\tau_T$  may not be very high.

Then, we used hot carriers to generate heterointerface traps [16, 17] and tried to improve the accuracy. The CP characteristics at RT before and after hot carrier stress are shown in Fig. 11. Stress drain and gate voltages were -8 V and -1 V, respectively, and stress time was 20 min. It can be seen

Fig. 9 Dependence of the CP characteristics on the pulse width at 90K.

Fig. 11 CP characteristics at RT before and after hot carrier stress.

from the figure that significant numbers of interface traps were generated. The dependence of the pulse-width upon the CP characteristics at 90 K after stress is illustrated in Fig. 12, which shows a marked increase in heterointerface traps. 1-  $I_{\rm CP}/I_{\rm CP0}$  at some values of  $V_{\rm BASE}$  in the rising portion are shown as a function of on-time at 90 K in Fig. 13. The values of  $\tau_{\rm T}$ ~1.7-2.0 µs are derived from the figure, which is related to the capture process of holes in the heterointerface traps.

Fig. 10 On-time dependent CP current related to heterointerface traps at 90 K.

Fig. 12 On-time dependent CP characteristics at 90 K after hot carrier stress.

Fig. 13 Time constant of the on-time dependent CP current derived from heterointerface traps generated by hot carriers.

# **Summary**

Transient phenomena related to the carrier capture/emission processes in interface traps were observed in the charge pumping characteristics of SiGe/Si hetero-channel pMOSFETs, i.e., the charge pumping characteristics were found to depend on the on/off time of the gate pulse. From these observations, time constants for the processes both in the SiGe/Si hetero-interface traps and in the gate-oxide interface traps were derived. The time constant is considered to depend on the energy level of the interface traps that are present over a wide range within the energy band gap. Therefore, this method provides an interesting way by which to evaluate the discrete energy levels of interface

traps in future small devices containing only a few traps.

## Acknowledgment

This work was partially supported by a Grant-in-Aid for Scientific Research from the Japan Society for the Promotion of Science, and by a Grant-in-Aid for Scientific Research on Priority Areas from the Ministry of Education, Science, Sports and Culture.

# References

- [1] J. Welser, J.L. Hoyt and J.F. Gibbons: IEDM Technical Digest, 1992, p. 1000.

- [2] T. Mizuno, S. Takagi, N. Sugiyama, J. Koga, T. Tezuka, K. Usuda, T. Hatakeyama, A. Kuroda and A. Toriumi: IEDM Technical Digest, 1999, p. 934.

- [3] T. Mizuno, J. Okamura and A. Toriumi: IEEE Trans. Electron Devices 41 (1994), p. 2216.

- [4] K. Takeuchi, T. Fukai, T. Tsunomura, A. T. Putra, A. Nishida, S. Kamohara and T. Hiramoto: IEDM Technical Digest, 2007, p. 467.

- [5] A. Asenov, A. Cathibnol, B. Cheng, K. P. McKenna, A. R. Brown, A. L. Shluger, D. Chanemougame, K. Rochereau and G. Ghibaudo: IEEE Electron Device Letters, vol. 29 (2008), p. 913.

- [6] N. Tega, H. Miki, T. Osabe, A. Kotabe, K. Otsuga, H. Kurata, S. Kamohara, K. Tokami, Y. Ikeda and R. Yamada: IEDM Technical Digest, 2006, p. 491.

- [7] N. Tega, H. Miki, F. Pagette, D. J. Frank, A. Ray, M. J. Rooks, W. Haensch and K. Torii: Technical Digest of Symposium on VLSI Technology, 2009, p. 50.

- [8] K. Takeuchi, T. Nagumo, S. Yokogawa, K. Imai and Y. Hayashi: Technical Digest of Symposium on VLSI Technology, 2009, p. 54.

- [9] T. Nagumo, K. Takeuchi, S. Yokogawa, K. Imai and Y. Hayashi: IEDM Technical Digest, 2009, p. 759.

- [10] S. Lee, H. J. Cho, Y. Son, D. S. Lee and H. Shin: IEDM Technical Digest, 2009, p. 763.

- [11] N. Tega, H. Miki, Z. Ren, C. P. D'Emic, Y. Zhu, D. J. Frank, J. Cai, M. A. Guillorn, D. G. Park, W. Haensch and K. Torii: IEDM Technical Digest, 2009, p. 771.

- [12] J. Murota, M. Sakuraba and B. Tillack: Jpn. J. Appl. Phys., vol. 45 (2006), p. 6767.

- [13] G. Groeseneken, H.E. Maes, N. Beltran and R.F. De Keersmaecker: IEEE Trans. Electron Devices, vol. 31 (1984), p. 42.

- [14] T. Tsuchiya, K. Yoshida, M. Sakuraba and J. Murota: 4<sup>th</sup> International SiGe Technology and Device Meeting, 2008, p. 64.

- [15] T. Tsuchiya, Y. Imada and J. Murota: IEEE Trans. Electron Devices, vol. 50 (2003), p. 58.

- [16] T. Tsuchiya, M. Sakuraba and J. Murota: IEEE IRPS Proceedings, 2004, p. 449.

- [17] T. Tsuchiya, S. Mishima, M. Sakuraba and J. Murota: Jpn. J. Appl. Phys., vol. 46 (2007), p. 5015.