# Influence of Cell Design and Gate-to-Source Voltage on Avalanche Robustness of SiC MOSFET Integrated JBS Diode

Submitted: 2022-09-12

Revised: 2023-01-13

Online: 2023-05-19

Accepted: 2023-01-13

Chongyu Jiang<sup>1,a</sup>, Hongyi Xu<sup>2,b\*</sup>, Songlin Yang<sup>3,c</sup>,Hengyu Wang<sup>1,d</sup>, Na Ren<sup>2,e</sup> and Kuang Sheng<sup>2,f</sup>

<sup>1</sup>College of Electrical Engineering, Zhejiang University, Hangzhou, China

<sup>2</sup>Hangzhou Global Scientific and Technological Innovation Center, Zhejiang University, Hangzhou,

<sup>3</sup>Dynex Semiconductor Ltd

<sup>a</sup>cy\_jiang@zju.edu.cn, <sup>b</sup>xuhongyi@zju.edu.cn, <sup>c</sup>songlin.yang@dynexsemi.com, <sup>d</sup>wanghengyu@zju.edu.cn, <sup>e</sup>ren na@zju.edu.cn, <sup>f</sup>shengk@zju.edu.cn

**Keywords:** SiC MOSFET integrated JBS Diode, avalanche robustness(UIS capability), failure mechanism.

Abstract. In this work, 1200 V SiC JMOS devices with different  $W_{sch}$  (2 µm, 2.5 µm and 3 µm) are fabricated. The single UIS tests under different  $V_{gs\_off}$  (-5 V and 0 V) are carried out to investigate the avalanche capability. The avalanche robustness among various  $W_{sch}$  under same  $V_{gs\_off}$  is also compared and analyzed by simulation. The different failure mechanisms between different  $V_{gs\_off}$  are studied by observation of de-cap result and analysis through simulation. The method of improving avalanche ruggedness of JMOS is proposed.

#### Introduction

The SiC MOSFET, operating at high-temperature and high-speed condition, has been proved to enhance power density significantly [1]. The performance in the third quadrant receives much attention for the body diode of SiC MOSFET can be used as a freewheeling diode in the forward circuit, bridge rectifier and PFC [2]. However, the body diode of SiC MOSFET, PN diode, will increase switching loss for its high turn-on voltage and long reverse time [3]. Besides, large stacking faults induced by basal plane dislocations will occur when PN diode conducts, which will increase on-resistance and diode voltage drop[4]. To eliminate this effect caused by the PN body diode, the SiC MOSFET embedded a low turn-on voltage Junction-Barrier-Schottky diode (JMOS) has been proposed [5-7]. The Junction-Barrier-Schottky diode can work during the operation in place of PN diode for its lower built-in potential and reduce the risk of potential failures caused by electrons and holes recombination.

The ruggedness of body diode remains a concern for JMOS in applications. Some works have been proposed to examine the reliability of JMOS, including short-circuit reliability, UIS reliability and surge current capability [8,9]. However, the mechanism study on avalanche robustness of JMOS is not enough and specific especially for different  $V_{gs\_off}$ .

In this work, 1200 V SiC JMOS devices with different  $W_{sch}$  (2 µm, 2.5 µm and 3 µm) are fabricated. The single UIS tests under different  $V_{gs\_off}$  (-5 V and 0 V) are carried out to investigate the avalanche capability. The avalanche robustness among various  $W_{sch}$  under same  $V_{gs\_off}$  is also compared and analyzed by simulation. The different failure mechanisms between different  $V_{gs\_off}$  are studied by observation of de-cap result and analysis through simulation. The method of improving avalanche ruggedness of JMOS is proposed.

## **Single Unclamped Inductive Switching Test Result**

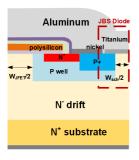

In this study, the Schottky barrier is integrated into the source region, which is referred as JMOS. The half-cell structure of 1.2kV JMOS in this work is shown in Fig. 1.

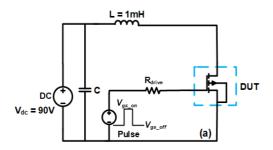

The UIS test bench and circuit schematic are shown in Fig. 2(a) and (b). The load inductance is 1mH. Power charges the inductor to a peak current when the device under test (DUT) turns on. The drain to source voltage climbs up to avalanche voltage and the current goes down until the stored energy is dissipated by the device when DUT turns off. Avalanche energy can be calculated by Eq. (1):

$$E_{ava} = \int_0^{t_{ava}} V_{ds} \cdot I_{ds} dt \tag{1}$$

where  $t_{ava}$  is the avalanche time,  $V_{ds}$  and  $I_{ds}$  are the drain to source voltage and drain current of the DUT.

**Fig. 1:** Schematic of SiC MOSFET integrated Junction-Barrier-Schottky diode (JMOS) with  $W_{JFET} = 3 \mu m$ .

**Fig. 2:** (a) Schematic of Single Pulse Unclamped Inductive Switching test circuit. (b) UIS test bench. Test conditions:  $V_{dc} = 90$ V, L = 1mH,  $V_{gs\_on} = 15$ V,  $V_{gs\_off} = -5$ V/0V, room temperature  $(T_0) = 300$ K.

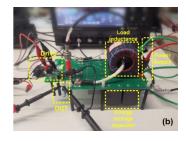

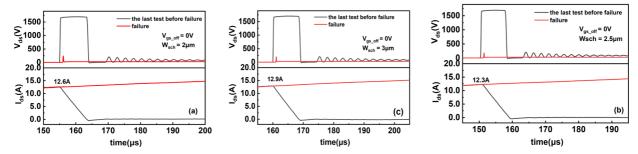

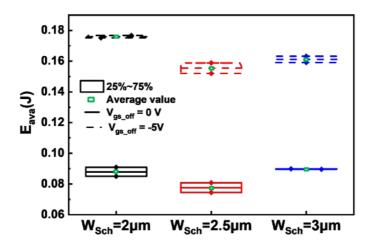

The single UIS test waveforms for JMOS with different  $W_{sch}$  (2 $\mu$ m, 2.5 $\mu$ m and 3 $\mu$ m) under  $V_{gs\_off} = -5$ V and  $V_{gs\_off} = 0$ V are shown in Fig. 3(a), (b), (c) and Fig. 4(a), (b), (c). The last non-destructive waveform and failure waveforms for three types of devices are shown. Two devices are evaluated for each test condition. The maximum avalanche energy ( $E_{ava\_max}$ ) is summarized in Fig. 5. It is found that JMOS with 2.5 $\mu$ m Schottky width has the lowest avalanche robustness under  $V_{gs\_off} = 0$ V and -5V. For JMOS with fixed  $W_{sch}$ ,  $E_{ava\_max}$  under  $V_{gs\_off} = -5$ V is nearly twice of that under  $V_{gs\_off} = 0$ V.

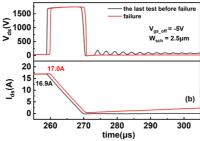

**Fig. 3:** The last UIS test before failure and failure test waveform ( $V_{ds}$ ,  $I_{ds}$ ) under  $V_{gs\_off} = -5$  V of JMOS with (a)  $W_{sch} = 2$  μm (b)  $W_{sch} = 2.5$  μm or (c)  $W_{sch} = 3$  μm. The maximum avalanche currents for JMOS with 2 μm, 2.5 μm and 3 μm Schottky diode width are 18.2 A, 16.9 A and 17.3 A. The avalanche voltage is around 1700 V.

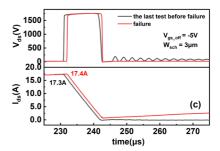

Fig. 4: The last UIS test before failure and failure test waveform ( $V_{ds}$ ,  $I_{ds}$ ) under  $V_{gs\_off} = 0$ V of JMOS with (a)  $W_{sch} = 2\mu$ m (b)  $W_{sch} = 2.5\mu$ m (c)  $W_{sch} = 3\mu$ m. The maximum avalanche currents for JMOS with  $2\mu$ m,  $2.5\mu$ m and  $3\mu$ m Schottky diode width are 12.6A, 16.9A and 17.3A. The device fails immediately under  $V_{gs\_off} = 0$ V after the onset of avalanche and dissipates no energy during avalanche when the current is large enough, which is different from  $V_{gs\_off} = -5$ V.

Fig. 5: The maximum avalanche energy for JMOS with various Schottky diode width under different  $V_{gs\_off}$ . It is found that JMOS with 2.5µm Schottky diode width has the lowest avalanche robustness under  $V_{gs\_off} = -5$ V and  $V_{gs\_off} = 0$ V. For JMOS with fixed  $W_{sch}$ , the maximum avalanche energy under  $V_{gs\_off} = -5$ V is nearly twice of that under  $V_{gs\_off} = 0$ V.

# Failure Mechanism Analysis

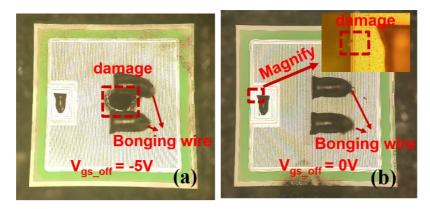

**De-caped results** To figure out the failure mechanism, the destructive devices are de-caped and the failure spot are displayed in Fig. 6. The large burn mark located in the active region under  $V_{gs\_off} = -5V$  test due to huge energy dissipation and junction temperature rise. On the other hand, the leakage current point is found near gate-finger under  $V_{gs\_off} = 0V$  test.

Fig. 6: Vertical view of failed JMOS ( $W_{sch} = 3\mu m$ ). The large burn damage between Bonging wire occurs under  $V_{gs\_off} = -5V$  test. The failure spot can be found near gate-finger under  $V_{gs\_off} = 0$  V test.

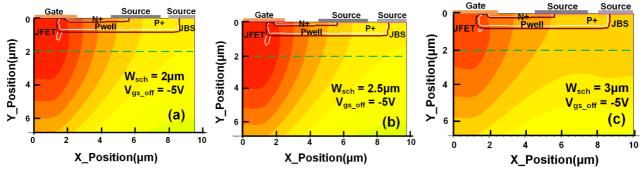

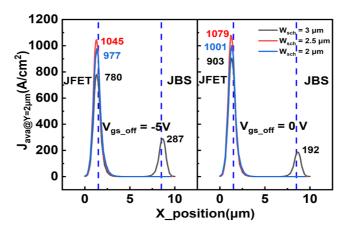

UIS capability analysis under the same  $V_{gs\_off}$  The UIS simulations are conducted for JMOS with different  $W_{sch}$ . For  $V_{gs\_off} = -5$ V, the lattice temperature distributions at the same time during avalanche for JMOS with different  $W_{sch}$  are shown in Fig. 7 and avalanche current density distribution at Y=2µm shown in Fig. 8. The JMOS with  $W_{sch} = 2.5$ µm has lowest avalanche robustness. Narrow  $W_{sch}$  leads to lower cell avalanche current density ( $J_{ava}$ ) under same chip area and wider  $W_{sch}$  means Schottky junction undertakes more avalanche current. The JMOS with  $W_{sch} = 2.5$ µm under  $V_{gs\_off} = 0$ V has the lowest UIS capability which has similar mechanism under  $V_{gs\_off} = -5$ V.

Fig. 7: UIS simulation results: the lattice temperature distributions at maximum average temperature during avalanche for JMOS with (a)  $W_{sch} = 2 \mu m$  (b)  $W_{sch} = 2.5 \mu m$  or (c)  $W_{sch} = 3 \mu m$ . The temperature of hot point in JFET area is highest for  $W_{sch} = 2.5 \mu m$ , which means its lowest avalanche robustness.

Fig. 8: Avalanche current density at Y=2 $\mu$ m (green dotted line in Fig. 7) at the same time during avalanche. The highest  $J_{ava}$  leads to the highest temperature in JFET area for  $W_{sch} = 2.5\mu$ m. When  $W_{sch}$  decreases, cell pitch decreases and cell number increases under same chip area. Therefore, the  $J_{ava}$  is lower for one cell and avalanche robustness is better. When  $W_{sch}$  increases, the  $J_{ava}$  is highest for one cell. However, JBS diode will undertake a portion of  $J_{ava}$  and thus, the current accumulation at Pwell corner near JFET area will be alleviated. Local heating power in JFET area is reduced and the avalanche robustness is enhanced.

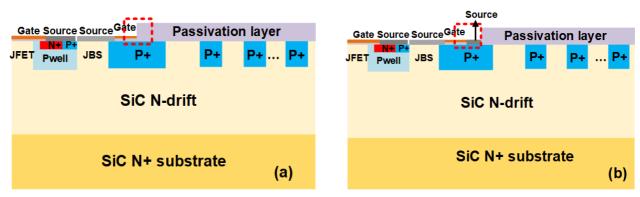

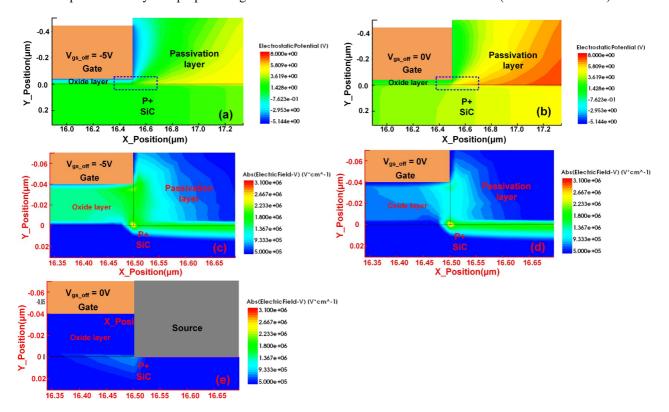

Failure mechanism analysis under different  $V_{gs\_off}$  To find out the difference between  $V_{gs\_off} = -5V$  and 0V, UIS simulations of transition region shown in Fig. 9(a) are carried out. The interaction of oxide, passivation layer near gate-finger is in red dotted line circle in Fig.9. Take  $W_{sch} = 3\mu m$  for example, electrostatic potential distributions at the same  $J_{ava}$  for interaction area under  $V_{gs\_off} = -5V$  and 0V are shown in Fig. 10(a) and (b). The electrostatic potential under  $V_{gs\_off} = 0V$  is denser. Electric field in blue dotted line area under  $V_{gs\_off} = -5V$  and 0V shown in Fig. 10(c) and (d). Higher electric field occurs at tri-corner under  $V_{gs\_off} = 0V$ . The new transition region (shown in Fig. 9(b)) with source between oxide and passivation layer is proposed. The simulation result (Fig. 10(e)) shows the electric field at tri-corner decreases to safe level. Thus, the influence of cell design and  $V_{gs\_off}$  on avalanche robustness of SiC JMOS are investigated and new device design with source finger added in transition region is proposed in this work to enhance the avalanche robustness.

Fig. 9: (a) The existing transition region in JMOS. (b) The proposed transition region in JMOS. The interaction area of oxide, passivation layer near gate-finger and SiC area is in red dotted line circle. Source electrode is added between gate oxide and passivation layer in proposed region to decrease electric field in interaction area (red dotted line area).

Fig. 10: Electrostatic Potential distribution in existing interaction area at the same avalanche current under (a)  $V_{gs\_off} = -5$ V and (b)  $V_{gs\_off} = 0$ V. A surface depletion area is formed on the surface between SiC and SiO<sub>2</sub> due to interface charge. Electrostatic potential lines are denser under  $V_{gs\_off} = 0$ V in blue dotted line area compared with  $V_{gs\_off} = -5$ V, which means higher Electric field in this area. Electric field in blue dotted line area in (a) and (b) are shown in (c)  $V_{gs\_off} = -5$ V and (d)  $V_{gs\_off} = 0$ V. Higher electric field occurs at tri-corner of oxide, passivation layer and SiC area under  $V_{gs\_off} = 0$ V, which causes oxide premature breakdown at gate finger (as observed in Fig. 6(b)) during avalanche test. (e) Electric field in proposed interaction area under  $V_{gs\_off} = 0$ V. The electric field in tri-corner area is improved below 1MV/cm.

## **Summary**

1200 V SiC JMOS devices with different  $W_{sch}$  (2 µm, 2.5 µm and 3 µm) are fabricated. The single UIS tests under different  $V_{gs\_off}$  (-5 V and 0 V) are carried out to investigate the avalanche capability. It is found that JMOS with 2.5µm Schottky width has the lowest avalanche robustness under  $V_{gs\_off} = 0$ V and -5V. For JMOS with fixed  $W_{sch}$ ,  $E_{ava\_max}$  under  $V_{gs\_off} = -5$ V is nearly twice of that under  $V_{gs\_off} = 0$ V.

The avalanche robustness among various  $W_{sch}$  under same  $V_{gs\_off}$  is also compared and analyzed by simulation. Narrow  $W_{sch}$  leads to lower cell avalanche current density  $(J_{ava})$  under same chip area and wider  $W_{sch}$  means Schottky junction undertakes more avalanche current.

The different failure mechanisms between different  $V_{gs\_off}$  are studied by observation of de-cap result and analysis through simulation. Higher electric field occurs at tri-corner in the transition region under  $V_{gs\_off} = 0$ V. A new device design with source finger added in transition region is proposed in this work to enhance the avalanche robustness.

## Acknowledgments

This research was funded by grants from the key area research and development program of Guangdong Province (Grant No.2021B0101300005) and Key Technologies R&D Program of Guangdong Province (2019B010143001).

#### References

- [1] A. Elasser and T. P. Chow, "Silicon carbide benefits and advantages for power electronics circuits and systems," in Proceedings of the IEEE, vol. 90, no. 6, pp. 969-986, June 2002.

- [2] Z. Zhu, H. Xu, L. Liu, N. Ren and K. Sheng, "Investigation on Surge Current Capability of 4H-SiC Trench-Gate MOSFETs in Third Quadrant Under Various VGS Biases," in IEEE Journal of Emerging and Selected Topics in Power Electronics, doi: 10.1109/JESTPE.2020.3028094., Introduction to the Electronic Age, E-Publishing Inc., New York, 1999, pp. 281-304.

- [3] Ryu, Sei Hyung, et al. "Effect of Recombination-Induced Stacking Faults on Majority Carrier Conduction and Reverse Leakage Current on 10 KV SiC DMOSFETs." Materials Science Forum, vol. 600–603, Trans Tech Publications, Ltd., Sept. 2008, pp. 1127–1130.

- [4] S. Palanisamy, T. Basler, J. Lutz, C. Kunzel, L. Wehrhahn-Kilian, R. Elpelt, "Investigation of the bipolar degradation of SiC MOSFET body diodes and the influence of current density", 2021.

- [5] Hino S, Hatta H, Sadamatsu K, Nagahisa Y, Yamamoto S, Iwamatsu T, et al. Demonstration of SiC-MOSFET Embedding Schottky Barrier Diode for Inactivation of Parasitic Body Diode. MSF 2017;897:477–82. https://doi.org/10.4028/www.scientific.net/msf.897.477.

- [6] W. Sung and B. J. Baliga, "On Developing One-Chip Integration of 1.2 kV SiC MOSFET and JBS Diode (JBSFET)," in IEEE Transactions on Industrial Electronics, vol. 64, no. 10, pp. 8206-8212, Oct. 2017, doi: 10.1109/TIE.2017.2696515.

- [7] S. Sundaresan, J. park, V. Mulpuri, S. Jadav and R. Singh, "3300 V SiC MOSFETs with integrated Schottky rectifiers," 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2020, pp. 206-209, doi: 10.1109/ISPSD46842.2020.9170176.

- [8] F. Hsu, C. Yen, C. Hung, K. Chu, L. Lee and C. Lee, "Short-Circuit Ruggedness Analysis of SiC JMOS and DMOS," 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2019, pp. 255-258, doi: 10.1109/ISPSD.2019.8757630.

- [9] C.-T. Yenet al., "Avalanche ruggedness and reverse-bias reliability of SiC MOSFET with integrated junction barrier controlled Schottkyrectifier," inProc. IEEE 30th Int. Symp. Power Semiconductor DevicesICs (ISPSD), May 2018, pp. 56–59. doi:10.1109/ISPSD.2018.8393601