# Enhanced Device Performance with Vertical SiC Gate-All-Around Nanowire Power MOSFETs

Submitted: 2022-09-04

Revised: 2022-12-05

Online: 2023-05-19

Accepted: 2022-12-06

Dong Yang<sup>1,a\*</sup>, Stephan Wirths<sup>2,b</sup>, Lars Knoll<sup>2,c</sup>, Yi Han<sup>1,d</sup>, Dan Mihai Buca<sup>1,e</sup> and Qing-Tai Zhao<sup>1,f</sup>

<sup>1</sup>PGI-9, Forschungszentrum Jülich GmbH, 52428 Jülich, Germany <sup>2</sup>Hitachi Energy Research, 5600 Lenzburg, Switzerland

ado.yang@fz-juelich.de, stephan.wirths@hitachienergy.com, lars.knoll@hitachienergy.com, y.han@fz-juelich.de, d.m.buca@fz-juelich.de, q.zhao@fz-juelich.de

Keywords: Nanowire, gate-all-around, SiC MOSFET, channel mobility.

**Abstract.** SiC gate-all-around (GAA) nanowire (NW) MOSFET is one of the most promising device architecture for the next generation of SiC power MOSFETs. This work reveals the great application potential of vertical SiC GAA NW power MOSFETs via TCAD simulation. The investigated devices show higher channel electron mobility ( $\mu_{ch}$ ) and larger channel carrier density ( $n_{ch}$ ) compared to the conventional SiC power MOSFET. Scaling down of NW diameter ( $D_{NW}$ ) is beneficial in terms of both, lowering channel resistance ( $R_{ch}$ ) via improving  $n_{ch}$  and, increasing breakdown voltage ( $V_b$ ) by modifying electric field distribution. Low specific-on resistance ( $R_{on,sp}$ ) of about 0.68 m $\Omega$ ·cm<sup>2</sup> for 1 kV SiC MOSFET is shown possible. However, scaling down the  $D_{NW}$  below 100 nm causes undesirable increase in  $R_{on,sp}$  due to the unscalable device area which is limited by the vertical gate wrapping stacks. The study on device scaling where the NW diameter ( $D_{NW}$ ) varies from 500 nm to 25 nm provides valuable design considerations for the device performance. Finally, a top-down process has been developed for the device fabrication. Vertical SiC NWs with aspect ratio of 10 are formed by an optimized micro-trench free dry etching process.

#### Introduction

SiC power electronics entered the market as the most promising candidate for high power and high voltage applications due to its superior intrinsic properties over Si devices regarding larger breakdown field, higher electron saturation velocity and higher thermal conductance [1]. However, SiC metal-oxide-semiconductor field-effect transistors (MOSFETs) suffer from high channel resistance due to low channel free electron density ( $n_{ch}$ ) and low channel electron mobility ( $\mu_{ch}$ ) as a result of high interface trap density ( $D_{it}$ ) [2-4]. A lot of research efforts have been put into the improvement of  $\mu_{ch}$ [5-7] by optimization of the dielectrics, including post-oxidation annealing at high temperature in nitric oxide (NO), nitrous oxide (N<sub>2</sub>O), boron nitride (BN) and phosphoryl chloride (POCl<sub>3</sub>) ambient. Still  $\mu_{ch}$  is far beyond SiC bulk electron mobility ( $\mu_b$ ).

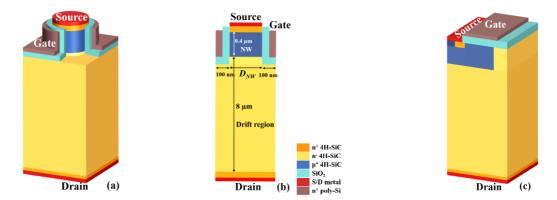

Gate-all-around (GAA) nanowire (NW) [8, 9] is one of the most promising device architectures for the next generation of MOSFETs. Recently, multi-gate SiC FinFETs have been published [10-12], showing advantages of scaled device architecture. A 3D and cross-sectional schematics of a vertical SiC GAA NW MOSFET design used in the present TCAD simulations is illustrated in Fig. 1 (a) and (b), respectively. Fig. 1 (c) is the 3D schematic of a conventional SiC MOSFET. The GAA NW devices exhibit higher  $\mu_{ch}$  and higher inversion channel electron density compared to that of the conventional devices. The higher mobility is due to the lower electric field in SiC NWs. Thus, a lower channel resistance ( $R_{ch}$ ) is obtained for vertical SiC GAA NW MOSFETs.

The study on device scaling where the NW diameter ( $D_{\rm NW}$ ) varies from 300 nm to 25 nm provides few design considerations for performance improvement. By scaling of  $D_{\rm NW}$ , both gate oxide and gate electrode thicknesses remain constant, here both are 50 nm. The cell pitch and the devices area are thus described as ( $D_{\rm NW} + 200$ ) nm and ( $D_{\rm NW} + 200$ )<sup>2</sup> nm<sup>2</sup>, respectively. For the simulation a maximum  $D_{\rm it}$  of 9.5 × 10<sup>13</sup> cm<sup>-2</sup>eV<sup>-1</sup> is considered to match the real situation at the SiC/SiO<sub>2</sub> interface. Schockley-Read-Hall (SRH) recombination with doping and temperature dependency, anisotropic

mobility model, anisotropic avalanche model, Auger recombination model and bandgap narrowing model (Slotboom) are taken into account for electrical simulations of the devices.

Fig. 1. (a) Three-dimensional and (b) cross-sectional schematics of a vertical SiC GAA NW MOSFET. The NW channel and the drift region are p-type  $(1 \times 10^{17} \text{ cm}^{-3})$  and n-type  $(1 \times 10^{16} \text{ cm}^{-3})$  doped, respectively. (c) A conventional SiC MOSFET is also shown as a reference. All the structural parameters are set as the same as in (b) for the two devices during the simulation.

### **Results and Discussion**

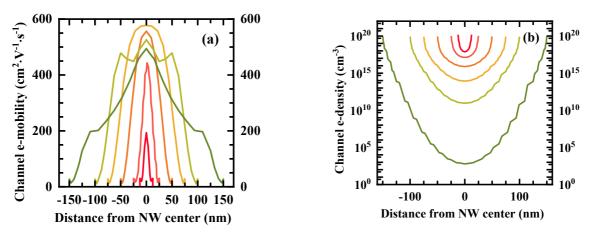

Fig. 2. (a) Channel electron mobility and (b) electron density distributions in NWs as function of  $D_{NW}$  from 300 nm to 25 nm. A gate bias of  $(V_{th} + 10)$  V is applied to turn on the devices.

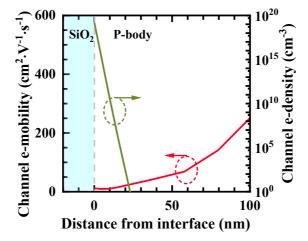

Fig. 3. Channel electron mobility and electron density of a conventional SiC MOSFET.

The simulated channel electron mobility and electron density as a function of NW dimeter,  $D_{\text{NW}}$  are shown in Fig. 2 (a) and (b). As  $D_{\text{NW}}$  reduces to 150 nm,  $\mu_{\text{ch}}$  reaches a maximum value of 570 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at the NW center. The corresponding  $n_{\text{ch}}$  in the NW center is  $1 \times 10^{14}$  cm<sup>-3</sup>. Both values are much higher than that of the conventional device in the same distance from SiC/SiO<sub>2</sub> interface,  $100 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  and  $7.7 \times 10^{-31} \text{ cm}^{-3}$ , respectively, as shown in Fig. 3. A volume inversion is observed for a D<sub>NW</sub><100nm. However, the scaling down of  $D_{\text{NW}}$  to <100nm leads to a decrease of electron mobility in NW center, associated with electric field increase.

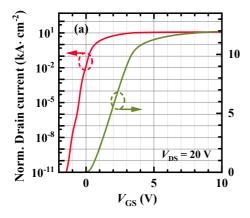

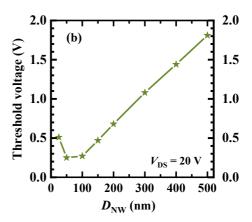

Fig. 4. (a) Transfer characteristics for a vertical SiC GAA MOSFET with  $D_{\text{NW}}$  of 150 nm in both linear and logarithmic scale. (b) The extracted  $V_{\text{th}}$  versus  $D_{\text{NW}}$  of the devices.

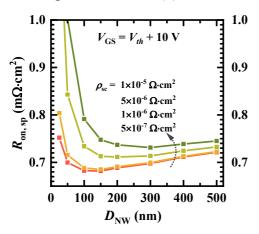

Fig. 5.  $R_{\text{on,sp}}$  versus  $D_{\text{NW}}$  of the devices with  $\rho_{\text{sc}}$  from  $5 \times 10^{-7} \ \Omega \cdot \text{cm}^2$  to  $1 \times 10^{-5} \ \Omega \cdot \text{cm}^2$ .

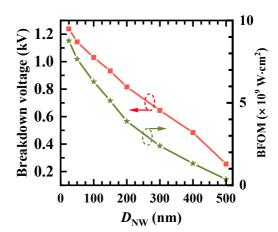

Fig. 6. Dependences of breakdown voltage and BFOM on  $D_{NW}$  at gate voltage  $V_{GS} = 0$  V.

The transfer characteristics of a vertical SiC GAA NW MOSFET with a  $D_{\rm NW}$  of 150 nm are shown in Fig. 4 (a) in both linear and logarithmic scale. The current is normalized to the device area using  $(200 + D_{\rm NW})^2$  nm<sup>2</sup> and considering a constant pitch size of 200 nm between NWs. The pitch size scalability is limited by the gate oxide thickness (here 50 nm SiO<sub>2</sub>) and the metal gate thickness. The improved electrostatics of GAA NW device are evidenced by the very low off-current and a subthreshold swing (SS) of 160 mV/decade. The threshold voltage ( $V_{\rm th}$ ), shown in Fig. 4 (b), decreases from 1.8 V to 0.25 V when the  $D_{\rm NW}$  scales from 500 nm to 50 nm. Further scaling down to 25 nm causes a slight  $V_{\rm th}$  increase to 0.51 V. The dependence of specific on-resistance ( $R_{\rm on,sp}$ ) on  $D_{\rm NW}$  is presented in Fig. 5 after considering of source contact resistivity ( $\rho_{\rm sc}$ ) from  $5\times10^{-7}$   $\Omega\cdot{\rm cm}^2$  to  $1\times10^{-5}$   $\Omega\cdot{\rm cm}^2$ . We have to point out that the scaling of NW cause a high contact resistance at the source. This can be solved by enlarging the diameter of the top NW to increase the contact area while keep the channel with a smaller diameter. The minimum  $R_{\rm on,sp}$  of approximate 0.68 m $\Omega\cdot{\rm cm}^2$  is obtained in the  $D_{\rm NW}$  range between 100 nm and 300nm, depending on the value of  $\rho_{\rm sc}$ . The higher  $\rho_{\rm sc}$ , the larger minimum  $R_{\rm on,sp}$  and the corresponding optimal  $D_{\rm NW}$ . Scaling  $D_{\rm NW}$  below 100 nm results in dramatic

increase in  $R_{\text{on,sp}}$  due to both extremely small source contact area and effective channel area compared to the pitch size. Indubitably,  $R_{\text{on,sp}}$  for very small NWs can be further reduced by shrinking the peripheral area of SiC NWs, e.g. thinning gate oxide or gate electrode, but with the cost of higher gate leakage current.

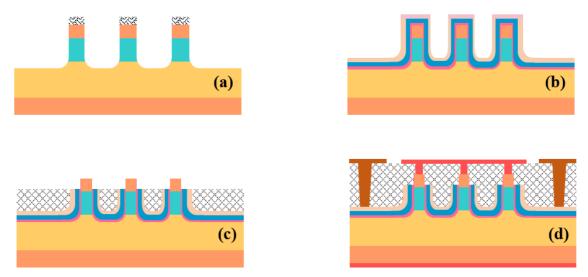

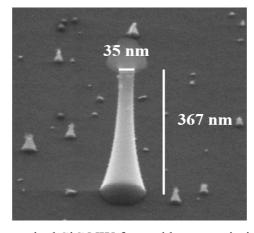

Furthermore, scaling down the  $D_{\rm NW}$  improves the off-state performance of the device. The breakdown voltage ( $V_b$ ) and Baliga's figure-of merits (BFOM) [13] are increased by downscaling of  $D_{\rm NW}$  (Fig. 6). A  $D_{\rm NW}$  of 25 nm improves the  $V_b$  above 1.2 kV. For devices with larger  $D_{\rm NW}$ ,  $V_b$  can be improved by extending drift region or decreasing drift region doping concentration at the expense of increasing  $R_{\rm on,sp}$ . Considering all the performance parameters, the device achieves optimum performance for NW diameter ranging from 100 to 200 nm which has advantage in processing feasibility. Based on the simulation data, vertical SiC GAA NW MOSFETs are presently under fabrication using a top-down process as shown in Fig. 7. Specific technology steps like SiC NWs patterning and micro-trench free etching processes have been successfully developed and tested. Fig. 8 shows, as an example, a SiC NW with a diameter of 35 nm and a height to width aspect ratio of ~10.

Fig. 7. A top-down process for fabrication of vertical SiC GAA NW MOSFETs. (a) NW etching by dry etching, (b) gate dielectrics and gate metal deposition, (c) planarization and top gate stacks removal, and (d) source, drain and gate contact formations.

Fig. 8. SEM image of a vertical SiC NW formed by an optimized dry etching process.

## **Summary**

The high inversion channel electron mobility and channel electron density indicate that GAA NW is a superior device architecture for SiC power MOSFET. A  $D_{\rm NW}$  designing window of 100 nm to 200 nm is suggested to achieve high  $\mu_{\rm ch}$  and low  $R_{\rm on,sp}$ . The maximum  $\mu_{\rm ch}$  in NW center, 570 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, is obtained for  $D_{\rm NW}$  =150 nm. Further down scale of  $D_{\rm NW}$  results in undesired  $\mu_{\rm ch}$  decrease. In addition, when the  $D_{\rm NW}$  is below 100 nm, the source contact resistance becomes the most significant factor in increasing  $R_{\rm on,sp}$  due to the extremely small contact area and the small effective channel area. For device with a  $D_{\rm NW}$  of 100 nm,  $V_{\rm b}$ ,  $R_{\rm on,sp}$  and BFOM are 1 kV, 0.68 m $\Omega$ ·cm<sup>2</sup> and 7.65 × 10<sup>19</sup> W·cm<sup>2</sup>, respectively. Finally, a top-down process with an optimized micro-trench free dry etching process has been developed for the device fabrication. A high conduct can be achieved by fabricating NW array. As an illustration, 1 A current can be conducted by an array of 47600 100nm NWs.

#### References

- [1] L. S. Ramsdell, Studies on silicon carbide, Journal of Earth and Planetary Materials, vol. 32, pp. 64-82, 1947.

- [2] J. N. Shenoy, G. L. Chindalore, M. R. Melloch, J. A. Cooper, J. W. Palmour, and K. G. Irvine, Characterization and optimization of the SiO2/SiC metal-oxide semiconductor interface, Journal of electronic materials, vol. 24, pp. 303-309, 1995.

- [3] A. Siddiqui, E. Hazem, and S. Shakti, The current status and the future prospects of surface passivation in 4H-SiC transistors, IEEE Transactions on Device and Materials Reliability, vol. 16, no. 3, pp. 419-428, 2016.

- [4] G.Y. Chung, C.C. Tin, J.H. Won, J.R. Williams, K. McDonald, R.A. Weller, S.T. Pantelides, L.C. Feldman, Interface state densities near the conduction band edge in n-type 4H-and 6H-SiC, 2000 IEEE Aerospace Conference, vol. 5, 2000.

- [5] G. Gudjonsson, H.O. Olafsson, F. Allerstam, P. A. Nilsson, E.O. Sveinbjornsson, H. Zirath, T. Rodle; R. Jos, High field-effect mobility in n-channel Si face 4H-SiC MOSFETs with gate oxide grown on aluminum ion-implanted material, IEEE Electron Device Lett., vol. 26, no. 5, pp. 96-98, Feb. 2005.

- [6] A. Modic, G. Liu, A. C. Ahyi, Y. Zhou, P. Xu, M. C. Hamilton, J. R. Williams, L. C. Feldman, S. Dhar, High Channel Mobility 4H-SiC MOSFETs by Antimony Counter-Doping, IEEE Electron Device Lett., vol. 35, no. 9, pp. 894-896, Sept. 2014.

- [7] D. Okamoto, M. Sometani, S. Harada, R. Kosugi, Y. Yonezawa, H. Yano, Improved Channel Mobility in 4H-SiC MOSFETs by Boron Passivation, IEEE Electron Device Lett., vol. 35, no. 12, pp. 1176-1178, Oct. 2014.

- [8] H. Lee, L. E. Yu, S. W. Ryu, et al, Sub-5nm all-around gate FinFET for ultimate scaling, 2006 Symposium on VLSI Technology, June 2006.

- [9] J. P. Colinge, C. W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A. M. Kelleher, B. McCarthy, and R. Murphy, Nanowire transistors without junctions, Nature nanotechnology, vol. 5, no. 3, pp. 225-229, Feb. 2010.

- [10] F. Udrea, K. Naydenov, H. Kang, T. Kato, E. Kagoshima, T. Nishiwaki, H. Fujiwara, and T. Kimoto, The FinFET effect in Silicon Carbide MOSFETs, IEEE 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Jun. 2021.

- [11] K. Naydenov, N. Donato, and F. Udrea, Operation and performance of the 4H-SiC junctionless FinFET, Eng. Res. Express, vol. 3, 035008, 2021.

- [12] Rahul P. Ramamurthy, N. Islam, M. Sampath, Dallas T. Morisette, and James A. Cooper, The tri-gate MOSFET: a new vertical power transistor in 4H-SiC, IEEE Electron Device Lett., vol. 42, issue 1, pp.90-93, 2020.

- [13] B. J. Baliga, SiC power devices: From conception to social impact, 2016 46th European Solid-State Device Research Conference (ESSDERC), issue 2378-6558, Sept. 2016.