# 10kV+ Rated SiC n-IGBTs: Novel Collector-Side Design Approach Breaking the Trade-Off between dV/dt and Device Efficiency

Submitted: 2022-09-04

Revised: 2023-02-15

Online: 2023-05-25

Accepted: 2023-02-15

Ioannis Almpanis<sup>1,a\*</sup>, Paul Evans<sup>1,b</sup>, Marina Antoniou<sup>2,c</sup>, Peter Gammon<sup>2,d</sup>, Lee Empringham<sup>1, e</sup>, Florin Undrea<sup>3,f</sup>, Philip Mawby<sup>2,g</sup>, and Neophytos Lophitis<sup>1,h</sup>

<sup>1</sup>University of Nottingham, Nottingham NG7 2RD, United Kingdom <sup>2</sup>University of Warwick, Coventry CV4 7AL, United Kingdom <sup>3</sup>University of Cambridge, Cambridge CB2 1TN, United Kingdom

<sup>a</sup>ezxia8@exmail.nottingham.ac.uk, <sup>b</sup>ezzpe@exmail.nottingham.ac.uk, <sup>c</sup>marina.antoniou@warwick.ac.uk, <sup>d</sup>p.m.gammon@warwick.ac.uk, <sup>e</sup>eezle@exmail.nottingham.ac.uk, <sup>f</sup>tu10000@cam.ac.uk, <sup>g</sup>p.a.mawby@warwick.ac.uk and <sup>b</sup>ezznl@exmail.nottingham.ac.uk

**Keywords:** SiC IGBT, dV/dt, trade-off curves, design optimization, electromagnetic interface.

Abstract. 10kV+ rated 4H- Silicon Carbide (SiC) Insulated Gate Bipolar Transistors (IGBTs) have the potential to become the devices of choice in future Medium Voltage (MV) and High Voltage (HV) power converters. However, one significant performance concern of SiC IGBTs is the extremely fast collector voltage rise (dV/dt) observed during inductive turn-off. Studies on the physical mechanisms of high dV/dt in 4H-SiC IGBTs revealed the importance of collector-side design in controlling the phenomenon. In this paper we propose a novel collector-side design approach, which consists of four n-type layers with optimized doping densities and allows the control of dV/dt independently from the device performance. Further, we demonstrate a reduction of dV/dt by 87% without degrading the high switching frequency capability of the device, or the on-state performance, through the addition of two n-type epitaxial layers in the collector side, between the buffer and the drift regions.

### Introduction

Silicon (Si) bipolar devices, IGBTs and thyristors, are currently the preferred devices in Medium and High voltage applications due to their reduced conduction losses. However, SiC MOSFETs rated up to 10kV have been extensively studied and with advancements in silicon carbide fabrication processing, SiC MOSFETs rated up to 3.3kV have become available commercially by multiple manufacturers with some manufacturers also offering functional devices and engineering samples at higher voltages, reaching up to10kV. Due to the improved high-frequency capabilities of SiC MOSFETs compared to Si bipolar devices, they started displacing them in certain applications. Nonetheless, the on-state resistance of unipolar devices increases quadratically with the device breakdown voltage and therefore SiC bipolar devices can be more favourable for Medium and High voltage applications, at above the 10 kV mark. SiC Punch Through (PT) IGBTs, combine the controllability of MOS devices while achieving a significantly reduced on-state voltage drop, making them attractive.

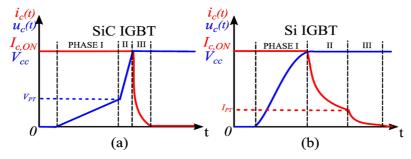

Although the operational principle of a SiC PT-IGBT is like that of its Si counterpart, the voltage and current transients are not. As shown in Fig. 1, during the inductive turn-off process, SiC IGBTs have two voltage rising phases (one slow and one fast) and one current decaying phase, whereas Si IGBTs have one voltage rise phase and two current decay phases (one fast and one slow). The fast voltage rising phase of SiC IGBTs produces an extremely high dV/dT, which is a major concern, affecting the possibility of adoption in the next generation power conversion applications. It poses significant challenges in utilizing gate drivers, cause EMI-related issues to adjacent circuits, increase wire insulation degradation in power machines and pose a challenge in packaging them. As a result,

many studies have been focused on understanding the origins of the high dV/dt in SiC IGBT and revealing methods of suppressing it.

Fig. 1.  $I_c - V_c$  curves during inductive turn-off for (a) silicon carbide and (b) silicon IGBT.

Experimental results presented in [1]-[4] showed that by varying the buffer layer doping and thickness, the plasma injection can be controlled effectively, which can trade off the static performance for improvements in switching losses. However, the impact of these variations on dV/dt was not analysed. Several simulation studies focused on understanding the origins of the high dV/dt and finding ways to suppress it. It was found that external components have limited influence on the dV/dt, and they increase significantly the energy loss [5]. By adjusting the buffer design, a trade-off between switching energy and dV/dt was documented, but the impact on the on-state voltage drop was not studied. The drift layer characteristics were found to affect the turn-off behaviour until the buffer punch-through voltage was reached, i.e. influencing the slow voltage rise phase but not the fast. It was also found that by adjusting the drift layer doping, it is possible to lift the PT voltage above the DC bus voltage, but this results in a non-PT design which leads to significantly increased switching losses [5], [6]. More recently, the authors in [7] suggested a two-step buffer design to allow independent control of the breakdown and switching characteristics of the PT IGBT. However, the simulations were performed under low inductive load of 25A/cm<sup>2</sup>, the dV/dt reduction was rather limited, from 200kV/µs to 120kV/µs, and the impact on the on-state voltage drop was not included in the study. Finally, there have been suggestions of some more complex solutions such as the usage of a multizone collector design [8] or the usage of trenches on the collector side [9]. However, these structures are difficult to be manufactured and they don't provide information on whether they can affect the dV/dt.

This paper analyses the inductive turn-off process of SiC IGBTs and reveal the origins of high dV/dt. After that, a comparison framework of different conventional buffer designs is presented to illustrate the trade-off between the on-state voltage drop, turn-off switching losses and maximum dV/dt under different current densities. Finally, a new collector-side design is proposed, featuring four n-type layers of optimised doping densities, which breaks the trade-offs, allowing for the control of dV/dT independently from other performance parameters.

#### **Device Structure and Methodology**

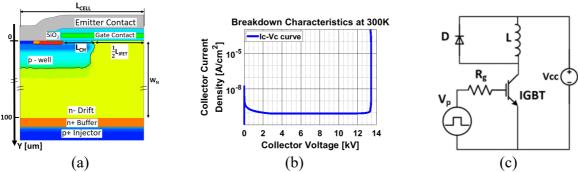

The fabrication process of a typical SiC PT n-IGBT was simulated using Synopsys Sentaurus Process. As shown in Fig. 2(a), the doping concentration (thickness) of the p+ injector, n buffer and n- drift layers are 1x10<sup>19</sup> cm<sup>-3</sup> (4 μm), 5x10<sup>17</sup> cm<sup>-3</sup> (3 μm) and 3x10<sup>14</sup> cm<sup>-3</sup> (100 μm) respectively. The p-well is featuring a retrograde profile which, as has already been described in previous works [10]–[13] improves the trade-off between breakdown, on-state and short-circuit characteristics. It achieves a breakdown voltage of about 13.5kV (Fig. 2(b)) at room temperature, thus allowing to rate the device at 10kV. For the dynamic simulations, a chopper circuit topology was used, coupling the finite element IGBT with a SPICE network shown in Fig. 2(c). The simulation uses previously calibrated models for critical semiconductor physics, including incomplete and impact ionization, Shockley-Read-Hall and Auger recombination, doping and temperature dependence of anisotropy, fixed charge and interface traps at the oxide-semiconductor interface etc [10], [11].

Fig. 2. (a) IGBT half-cell, (b) Breakdown waveform and (c) Chopper circuit topology.

## Silicon Carbide Inductive Turn-Off Process

As has been already experimentally demonstrated in various papers [2]-[4], [15]-[18], the turnoff process of SiC PT IGBTs exhibit two different voltage rising phases followed by one current decaying phase as shown in Fig. 1(a). The first, slow, voltage rising period initiates when the gate voltage falls below the threshold voltage and the electron current ceases. As a result, the total current is sustained by hole current and the space charge region (or depletion region) starts expanding toward the collector side by removing holes at the space charge boundary. The collector voltage is related to the space charge width by Eq. 1, where the positive charge in the space charge region due to the hole current flow has been taken into account. This positive charge is given by Eq. 2, assuming that the holes are moving at their saturation drift velocity due to the high electric field in the space charge region. As a result, the space charge width and collector voltage are increasing at a slow pace determined by the injected hole concentration and the total current density. Additionally, the slope of the electric field is constant according to Poisson's equation 3.

$$V_c(t) = \frac{q(N_d + p_{SC})W_{SC}^2(t)}{2\varepsilon_S}$$

$$p_{SC} = \frac{J_{C,ON}}{qv_{sat,p}}$$

(1)

$$p_{SC} = \frac{J_{C,ON}}{qv_{sat,p}} \tag{2}$$

$$\frac{dE}{dx} = \frac{\rho}{\varepsilon_s} = \frac{q(N_d + p_{SC})}{2\varepsilon_s} \tag{3}$$

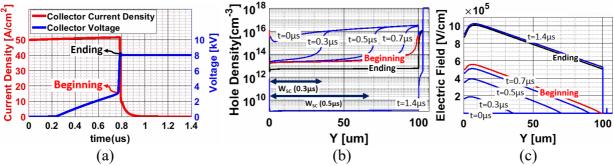

The slow voltage rising phase ends when the space charge region reaches the buffer. The voltage at which this takes place (Punch-Through voltage, V<sub>PT</sub>) is given by Eq. 1, where replacing the Wsc(t) with W<sub>N</sub>. After that time, the electric field slope increases according to Eq. 3 due to the higher doping density of the buffer layer and the Electric field takes a trapezoidal shape. The origin of the high dV/dt can be explained by examining the hole density at the beginning and ending of the high voltage rising phase, shown in Fig. 3(b) with red and black colours respectively. It can be seen that the space charge region width inside the buffer layer and the amount of holes to be removed during this period are small, leading to a fast voltage transient after the Punch Through.

Fig. 3. (a) Typical I<sub>c</sub>(t) and V<sub>c</sub>(t) curves during inductive turn-off, (b) Hole distribution and (c) Electric field across the IGBT at various instants during the turn-off process.

### Influence of the drift layer parameters

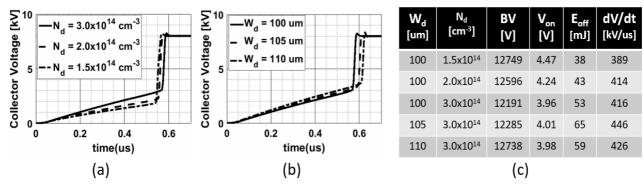

The drift layer parameters can adjust the punch-through voltage (V<sub>PT</sub>) according to Eq. 1. Figures 4(a) and (b) show that the V<sub>PT</sub> can be modified by either the drift region width or doping concentration. However, the high dV/dt during the fast voltage rising period remains relatively unaffected. This happens because the minority carriers injected into the buffer and drift layer are mainly dependent on the buffer layer characteristics, and as a result, the amount of holes to be removed from the buffer layer during the fast voltage rising phase is small for all drift layer variations. Nonetheless, it should be noted that drift layer doping concentration and width have opposite influences on the breakdown voltage, meaning that by increasing the doping density the breakdown voltage reduces, and by increasing the thickness the breakdown voltage increases. The table in Fig. 4(c) summarises the impact of the drift layer parameters on the static and dynamic performance of the IGBT.

Fig. 4. Collector voltage rising curves during turn-off for IGBTs with different (a) drift layer thicknesses and (b) drift layer doping concentrations, (c) Table summarising the static and dynamic characteristics of IGBTs with different variations of drift layer doping concentrations and thicknesses.

### The role of the Buffer layer and the impact of its parameter's variation.

The buffer layer in PT-SiC IGBT plays a crucial role in the device's operation and affects the device's performance because it controls the plasma concentration in the drift layer. Higher buffer doping density and width lead to lower plasma concentration and as a result lower switching losses and higher on-state voltage drop. The minimum charge in the buffer layer to prevent reach-through to the injector layer can be obtained using Eq. 4[19]. Assuming a critical electric field (E<sub>c</sub>) of  $2x10^6$  V/cm for typical drift layer doping concentrations, the minimum charge requirement is about  $1x10^{13}$ cm<sup>-2</sup>. A buffer layer with a thickness (W<sub>B</sub>) of 3 µm requires a doping density (N<sub>B</sub>) of  $3.33x10^{16}$ cm<sup>-3</sup>. By using a buffer layer charge higher than the minimum requirement, the plasma injection and therefore the on-state switching losses can be controlled.

$$N_B \cdot W_B = \frac{\varepsilon_S E_C}{q} \tag{4}$$

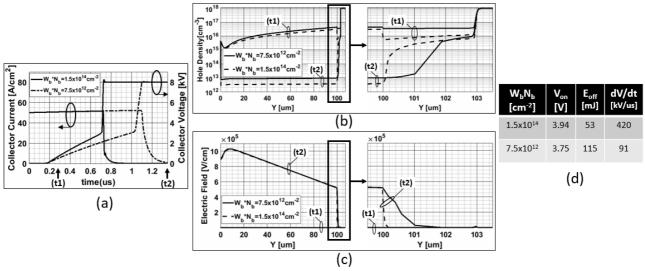

Fig. 5(a) compares the switching behaviour of two IGBTs with total buffer charges 1.5x10<sup>14</sup> cm<sup>-2</sup> and 7.5x10<sup>12</sup> cm<sup>-2</sup>, achieved by using 5x10<sup>17</sup> cm<sup>-3</sup> and 2.5x10<sup>16</sup> cm<sup>-3</sup> doping density in the 3 μm thick buffer layer. Figures 5(b) and 5(c) show the hole density and the electric field at the beginning (t1) and ending (t2) of the turn-off. As can be seen, the lower buffer charge leads to higher plasma injection in the buffer layer during the on-state and increases the depletion region width within the buffer layer. Both these effects lead to a higher amount of holes being removed from the buffer layer and thus lower dV/dt. However, higher plasma concentration in the drift layer leads to increased turn-off duration and higher switching losses. From the results in Fig. 5 for variation of the buffer charge can be concluded that the buffer design affects the three operational characteristics of interest (the on-state voltage drop, the switching losses and the maximum dV/dt), but in a way that they cannot be independently adjusted. Additionally, a more straightforward comparison framework is required to compare different IGBT designs. This comparison framework will be presented in the next section.

#### Comparison framework

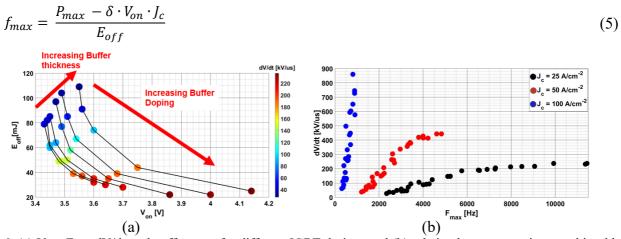

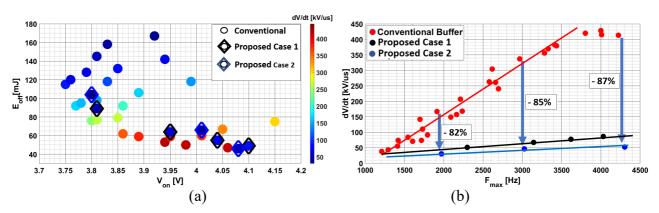

In order to compare the performance of different IGBT designs directly taking into account the on-state, switching losses and maximum dV/dt, these quantities must be clearly presented. For silicon IGBTs, the traditional  $E_{\rm off}-V_{\rm on}$  trade-off curves are sufficient because these two quantities are the most important. However, in SiC IGBT the maximum dV/dt is also a quantity that needs to be optimised. As a result, including the maximum dV/dt value during the turn-off, by using a colourmap, into the  $E_{\rm off}-V_{\rm on}$  trade-off curves for silicon IGBTs, all three parameters can be clearly represented. Figure 6 (a) compares thirty IGBTs with different buffer designs, by varying the buffer layer doping concentration and thickness. It can be concluded that the lower dV/dt always comes with the cost of higher switching losses and all three depicted quantities are strongly coupled. As a result, the higher frequency operation comes with the cost of a higher maximum dV/dt.

Fig. 5. (a)  $I_c(t)$  and  $V_c(t)$  curves during the turn-off of IGBTs with different buffer layer charges ( $W_bN_b$ ). Comparison of the (b) hole densities and (c) electric field inside IGBTs with different buffer charges at the beginning and ending of the turn-off process, and (d) table summarising their switching characteristics.

Another way of comparison of different IGBT designs is to calculate the maximum switching frequency that can be achieved for a given thermal limitation. Assuming that the maximum power that can be dissipated on losses ( $P_{max}$ ) is limited by the packaging at  $300 \text{W/cm}^2$  and with a duty cycle ( $\delta$ ) of 50%, the maximum switching frequency ( $f_{max}$ ) can be calculated by using Eq. 5. In this way, the three-variable optimisation problem became a two-variable one, and the almost linear dependence of the maximum switching frequency and dV/dt can be observed easier, as shown in Fig. 6(b) for different IGBT designs and current densities.

Fig. 6. (a)  $V_{on}$  – $E_{off}$  –dV/dt trade-off curves for different IGBT designs and (b) relation between maximum achievable switching frequency and maximum dV/dt of conventional PT-IGBT designs under different current densities.

#### **Proposed structure**

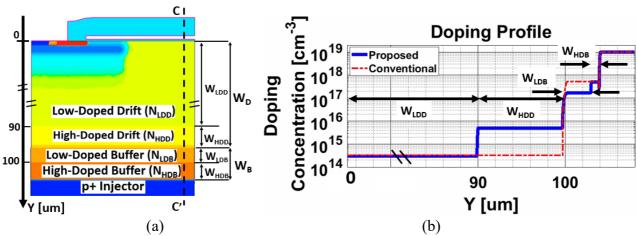

After a detailed analysis of the behaviour of several IGBT designs under various operation conditions, we ended up with a novel device structure which achieves decoupling of the dV/dt from the trade-off between Von-Eoff. As a result, the increasing of the switching speed of the IGBT is not limited by the high dV/dt and EMI-related issues. The proposed structure is compared with the conventional one in Fig. 7. The role of the four n-type layers of the drift and buffer regions can be summarised as follows:

- The higher doped buffer region (HDB) prevents the depletion region from reaching through to the injector region during the forward (static) blocking. It provides the minimum buffer charge as described by Eq. 4.

- The lower doped buffer region (LDB) controls the plasma injection into the drift layer. Higher doping density or width leads to lower plasma injection into the drift region, and therefore the trade-off between on-state and switching losses can be adjusted.

- The higher doped drift region (HDD) is responsible for preventing the depletion region from punching through to the buffer layer during the voltage rising phase of the turn-off process. As a result, it controls the dV/dt by increasing the amount of minority carriers to be removed during the fast voltage transient phase.

- Finally, the lower doped drift region (LDD) controls the breakdown characteristics and the PT voltage of the IGBT.

Fig. 7. (a) Novel collector side IGBT design featuring a step doping profile for the buffer and the drift layers, (b) doping profile comparison between the conventional and the proposed structure across the c-c' cut.

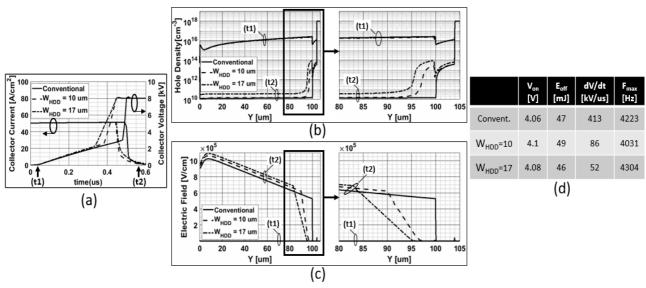

This simple device structure offers the advantage of almost independent control of the trade-off between on-state losses, switching losses and maximum dV/dt. Figure 8 shows how the high dV/dt phase during the inductive turn-off process can be modified with the appropriate selection of doping density and width of the higher-doped drift region (HDD). In this case, the electric field changes slope in the interface between the LDD and HDD regions, instead of the interface between the drift and buffer layer of the conventional structure. As a result, the depletion width during the fast voltage rising phase is much higher achieving an 87% reduction of the maximum dV/dt without affecting significantly the on-state voltage drop and the turn-off switching losses of the IGBT.

Fig. 8. (a) Comparison of  $I_c(t)$  and  $V_c(t)$  curves during the turn-off between the conventional IGBT and IGBTs with different High Doped Drift regions (HDD) to reduce the dV/dt during the fast voltage rising phase. Comparison of the (b) hole densities and (c) electric field inside these IGBTs at the beginning and ending of the turn-off process, and (d) table summarising their switching characteristics.

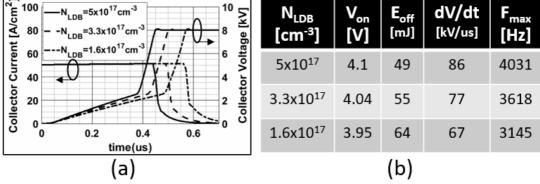

Figure 9 shows how the lower-doped buffer region (LDB) affects the trade-off between Von-Eoff. As can be seen, the optimum Von-Eoff for a desired application can be chosen without affecting significantly the dV/dt.

Fig. 9. (a) Comparison of  $I_c(t)$  and  $V_c(t)$  curves during the turn-off between IGBTs with different Low Doped Buffer regions (LDB) to control the  $V_{on}$ - $E_{off}$  trade-off, and (b) table summarising their switching characteristics.

## Comparison between the conventional and the proposed structure

The reduction of the maximum dV/dt achieved with the proposed device structure can be seen in figures 10(a) and 10(b). The coloured dots inside the diamond symbols in Fig. 10(a) represent variations of the proposed IGBT structures. It is obvious that the maximum dV/dt of all proposed IGBT structures is greatly improved when it is compared to the conventional designs. Furthermore, the reduction of the dV/dt for a given switching frequency achieved with the new design can be seen in Fig. 10(b), where the red points are for the conventional IGBT designs and the black and blue for the two different cases of the proposed design. Equation 5 was used to calculate the maximum switching frequency of each simulated device under inductive load of 25 A/cm<sup>2</sup>.

Fig. 10. Comparison between the conventional and the proposed structure using (a) the  $V_{on} - E_{off} - dV/dT$  trade-off curves and (b)  $F_{max} - dV/dt$  trade-off curves.

# **Summary**

To conclude, this paper presented a novel device structure which can mitigate the high dV/dt produced during the turn-off process of SiC PT-IGBTs. By making use of a four-step n-type doping profile on the collector side, Fig. 7(b), the IGBT efficiency and dV/dt can be controlled independently. Furthermore, this device structure simplifies the IGBT optimization procedure because it provides a straightforward relationship between the device parameters and operational characteristics. As a result, an optimal device can be designed for specific application requirements.

#### References

- [1] Q. Zhang *et al.*, "Design and Characterization of High-Voltage 4H-SiC p-IGBTs," *IEEE Trans. Electron Devices*, vol. 55, no. 8, pp. 1912–1919, Aug. 2008, doi: 10.1109/TED.2008.926627.

- [2] S.-H. Ryu *et al.*, "High performance, ultra high voltage 4H-SiC IGBTs," in *2012 IEEE Energy Conversion Congress and Exposition (ECCE)*, Sep. 2012, pp. 3603–3608, doi: 10.1109/ECCE.2012.6342311.

- [3] S. H. Ryu *et al.*, "20 kV 4H-SiC N-IGBTs," *Mater. Sci. Forum*, vol. 778–780, pp. 1030–1033, Feb. 2014, doi: 10.4028/www.scientific.net/MSF.778-780.1030.

- [4] E. V. Brunt *et al.*, "22 kV, 1 cm 2, 4H-SiC n-IGBTs with improved conductivity modulation," in 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD), Jun. 2014, pp. 358–361, doi: 10.1109/ISPSD.2014.6856050.

- [5] H. Liu *et al.*, "Physical modeling and design optimization of 4H-SiC insulated gate bipolar transistors for dv/dt reduction," *Semicond. Sci. Technol.*, vol. 36, no. 2, p. 025009, Feb. 2021, doi: 10.1088/1361-6641/abcb18.

- [6] W. Deng *et al.*, "Influence of N-drift Layer Parameters on Static and Dynamic Performances of Ultra-high Voltage SiC IGBT," in *2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia)*, Nov. 2020, pp. 2191–2194, doi: 10.1109/IPEMC-ECCEAsia48364.2020.9367646.

- [7] H. Liu *et al.*, "High dv/dt in High Voltage SiC IGBT and Method of Suppression," in *2021 IEEE 1st International Power Electronics and Application Symposium (PEAS)*, Nov. 2021, pp. 1–8, doi: 10.1109/PEAS53589.2021.9628556.

- [8] G. Tang *et al.*, "Frequency-Improved 4H-SiC IGBT With Multizone Collector Design," *IEEE Trans. Electron Devices*, vol. 67, no. 1, pp. 198–203, Jan. 2020, doi: 10.1109/TED.2019. 2951021.

- [9] Y. Wang *et al.*, "Low Turn-Off Loss 4H-SiC Insulated Gate Bipolar Transistor With a Trench Heterojunction Collector," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 1010–1015, 2020, doi: 10.1109/JEDS.2020.3022571.

- [10] A. K. Tiwari *et al.*, "Retrograde p-Well for 10-kV Class SiC IGBTs," *IEEE Trans. Electron Devices*, vol. 66, no. 7, pp. 3066–3072, Jul. 2019, doi: 10.1109/TED.2019.2918008.

- [11] A. K. Tiwari *et al.*, "On the robustness of ultra-high voltage 4H-SiC IGBTs with an optimized retrograde p-well," 2019, doi: 10.1109/DEMPED.2019.8864804.

- [12] I. Almpanis *et al.*, "Influence of Emitter Side Design on the Unintentional Turn-on of 10kV+ SiC n-IGBTs," in *IEEE Energy Conversion Congress and Exposition*, 2022, p. 6.

- [13] I. Almpanis et al., "Short-Circuit Performance Investigation of 10kV+ Rated SiC n-IGBT," in *IEEE Workshop on Wide Bandgap Power Devices and Applications in Europe (WiPDA-Europe 2022)*, 2022, p. 6.

- [14] N. Lophitis *et al.*, "TCAD Device Modelling and Simulation of Wide Bandgap Power Semiconductors," in *Disruptive Wide Bandgap Semiconductors, Related Technologies, and Their Applications*, 2018.

- [15] M. K. Das *et al.*, "A 13 kV 4H-SiC n-Channel IGBT with Low Rdiff, on and Fast Switching," *Mater. Sci. Forum*, vol. 600–603, pp. 1183–1186, Sep. 2008, doi: 10.4028/www.scientific.net/MSF.600-603.1183.

- [16] E. Van Brunt *et al.*, "27 kV, 20 A 4H-SiC n-IGBTs," in *Materials Science Forum*, 2015, vol. 821–823, doi: 10.4028/www.scientific.net/MSF.821-823.847.

- [17] Y. Yonezawa *et al.*, "Device Performance and Switching Characteristics of 16 kV Ultrahigh-Voltage SiC Flip-Type n-Channel IE-IGBTs," *Mater. Sci. Forum*, vol. 821–823, pp. 842–846, Jun. 2015, doi: 10.4028/www.scientific.net/MSF.821-823.842.

- [18] K. Koseki *et al.*, "Dynamic Behavior of a Medium-Voltage N-Channel SiC-IGBT With Ultrafast Switching Performance of 300 kV/μs," *IEEE Trans. Ind. Appl.*, vol. 54, no. 4, pp. 3558–3565, Jul. 2018, doi: 10.1109/TIA.2018.2824247.

- [19] B. Jayant Baliga, Fundamentals of Power Semiconductor Devices. .