# Demonstration of SiC Trench Gate MOSFETs with Narrow Cell Pitch Using Source Self-Aligned Process

Submitted: 2022-09-02

Revised: 2022-12-06

Online: 2023-05-31

Accepted: 2022-12-06

Shinichi Kimoto<sup>1,a\*</sup>, Ryosuke Iijima<sup>2,b</sup> and Shinsuke Harada<sup>1,c</sup>

<sup>1</sup>National Institute of Advanced Industrial Science and Technology, 16-1 Onogawa, Tsukuba, Ibaraki 305-8569, Japan

<sup>2</sup>Toshiba Corporation, 1 Komukai Toshiba-cho, Saiwai-ku, Kawasaki, Kanagawa 212-8582, Japan <sup>a</sup>shinichi1.kimoto@toshiba.co.jp, <sup>b</sup>ryosuke.iijima@toshiba.co.jp, <sup>c</sup>s-harada@aist.go.jp

Keywords: 4H-SiC, Trench, MOSFET, Cell pitch, Self-aligned, Deep-channel, On-resistance

**Abstract.** The SiC trench gate MOSFET with narrow cell pitch is demonstrated using a process in which the n<sup>+</sup> source is self-aligned to the trench gate. A minimum cell pitch of 1.6 μm, which is difficult to achieve using the conventional device structure, is easily fabricated by applying a deep n<sup>+</sup> source and a buried interlayer dielectric structure. The cell pitch reduction indicates a beneficial trend that contributes to a decrease in the specific on-resistance and an increase in the breakdown voltage. The process and structure are promising for further improving SiC power device characteristics.

#### Introduction

SiC trench gate MOSFETs are generally more suitable than planar gate MOSFETs for cell pitch  $(W_{cell})$  reduction. A narrow  $W_{cell}$  is desirable to reduce the specific on-resistance  $(R_{on}A)$ , especially below the 1200 V-class, where the ratio of the channel resistance is high. However, a  $W_{cell}$  reduction causes difficulties in the alignment and patterning processes. The self-aligned process is utilized to overcome these issues. Recent studies have reported the conventional type of single-trench gate MOSFETs (ST-MOSFETs) using the self-aligned process, such as the  $p^+$  shielding region under the gate trench and the segmented contact regions [1-4]. With further reduction in  $W_{cell}$  in the ST-MOSFETs, difficulties in establishing ohmic contact appears due to the contact aperture limit are observed next. In this study, we developed an  $n^+$  source self-aligned process adjacent to the gate trench, which realizes the stable fabrication with narrow  $W_{cell} = 2.0 \, \mu m$  or less, and demonstrated deep-channel MOSFETs (DC-MOSFETs) fabricated using this self-aligned process. This device has a deep  $n^+$  region and a buried interlayer dielectric (ILD), which allow for a significantly narrow  $W_{cell}$ .

# **Design Concept and Fabrication**

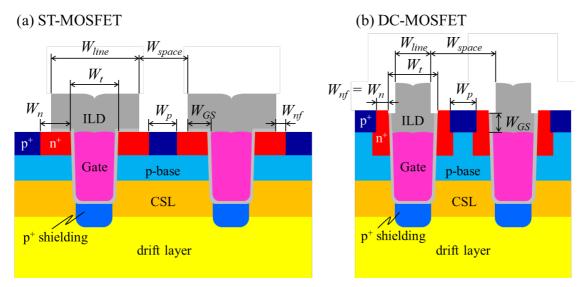

Figure 1 shows the schematic cell structures of (a) ST-MOSFET and (b) DC-MOSFET. The structural differences between ST-MOSFET and DC-MOSFET are  $n^+$  source depth and ILD aperture width. For the ST-MOSFET,  $W_{cell}$  is represented by

$$W_{cell} = W_t + 2W_n + W_p = W_t + 2W_{nf} + W_p + 2W_{GS},$$

(1)

where  $W_t$  is the trench width;  $W_n$  is the n<sup>+</sup> width;  $W_p$  is the p<sup>+</sup> width;  $W_{GS}$  is the gate-source (GS) distance; and  $W_{nf} = W_n - W_{GS}$  is the n<sup>+</sup> footprint width.  $W_{GS}$  requires a certain thickness to obtain a low GS failure rate and low GS capacitance. Additionally, if the ILD width and its aperture width are defined as  $W_{line}$  and  $W_{space}$ , respectively,  $W_{cell}$  reduction sacrifices  $W_{space}$  owing to the constraint  $W_{line} = W_t + 2W_{GS}$ . Consequently, the ILD aperture and metal coverage failure associated with  $W_{space}$  reduction, and ohmic contact failure where  $W_{nf} < 0$ , are likely to occur because of  $W_{space} = 2W_{nf} + W_p$ . On the other hand,  $W_{cell}$  in the DC-MOSFET is given by

$$W_{cell} = W_{t} + 2W_{n} + W_{p} = W_{t} + 2W_{nf} + W_{p}.$$

(2)

It follows that  $W_{nf} = W_n$ . Because the n<sup>+</sup> source is formed deeper than that in the ST-MOSFET, the gate electrode is formed deeper, and the ILD is buried in the trench. Thus, a certain thickness of  $W_{GS}$  is retained in the vertical direction, and  $W_{GS}$  is excluded from the cell parameters, which allow the DC-MOSFET to reduce the  $W_{cell}$  significantly. Furthermore, the strict alignment control at the ILD aperture is unnecessary because  $W_{line}$  only needs to satisfy  $0 \le W_{line} < W_t$ . The ILD aperture, metal coverage, and ohmic contact failure do not occur easily because  $W_{space}$  is maintained wider than that in ST-MOSFET. As stated above, the DC-MOSFET is advantageous in reducing the  $W_{cell}$  with stable processes.

Fig. 1. Schematic cell structures of (a) ST-MOSFET and (b) DC-MOSFET.

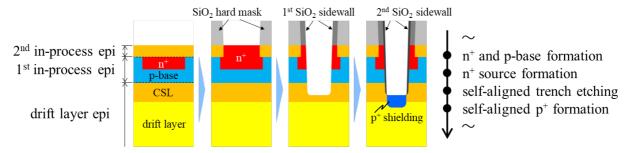

Figure 2 illustrates the main fabrication procedure for the DC-MOSFETs. A drift layer, which concentration and thickness were  $1.5\times10^{16}$  cm<sup>-3</sup> and 4.7 µm, was prepared on a substrate for the 650 V-class, and a current spreading layer (CSL) was then stacked on the drift layer. The bottom half of the n<sup>+</sup> and p-base regions were formed via ion implantation in the first in-process epitaxial growth layer, whereas the upper half of the n<sup>+</sup> source region was formed via ion implantation in the second in-process epitaxial growth layer. Subsequently, without removing the SiO<sub>2</sub> hard mask, the first SiO<sub>2</sub> sidewall was formed, and a SiC trench narrower than the width of the P implantation was formed by dry etching. A p<sup>+</sup> shielding region was then formed by Al implantation with the second SiO<sub>2</sub> sidewall. Therefore, both the p<sup>+</sup> shielding region and n<sup>+</sup> source region were formed using the self-aligned process to the trench gate.

Fig. 2. Main fabrication procedure including the n<sup>+</sup> source self-aligned process for the DC-MOSFET.

#### **Experimental Results**

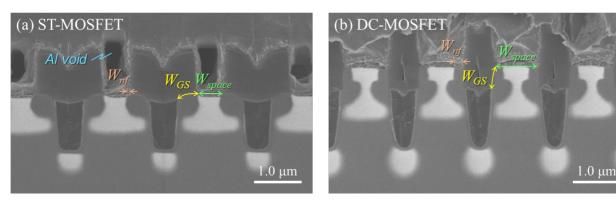

**Demonstration.** Figure 3 shows the cross-sectional SEM image of (a) ST-MOSFET with  $W_{cell} = 2.0 \, \mu \text{m}$  and (b) DC-MOSFET with  $W_{cell} = 1.6 \, \mu \text{m}$ . The DC-MOSFET was fabricated using the n<sup>+</sup> source self-aligned process, whereas the ST-MOSFET did not use the process. For the ST-MOSFET, an Al void and a short  $W_{nf}$  due to the narrow  $W_{space}$  were observed. Moreover, because  $W_{nf}$  is slightly different on the left and right sides of the trench gate owing to the misalignment of both the upper half of the n<sup>+</sup> source region and the ILD aperture to the trench gate, there is a concern that  $W_{nf} < 0 \, \mu \text{m}$  on at least one side when  $W_{cell} < 2.0 \, \mu \text{m}$ . However, for the DC-MOSFET, the Al coverage is satisfactory because of the relatively wide  $W_{space}$ , and  $W_{nf}$  is also wide enough.  $W_{nf}$  is formed equally on both sides of the trench gate because it is not affected by the misalignment of the ILD aperture when  $W_{line} < W_{l}$ . Thus, owing to the ability to form the  $W_{GS}$  in the vertical direction, trench gate MOSFETs with  $W_{cell} < 2.0 \, \mu \text{m}$  are easily realized.

Fig. 3. Cross-sectional SEM images of (a) ST-MOSFET with  $W_{cell} = 2.0 \, \mu m$  and (b) DC-MOSFET with  $W_{cell} = 1.6 \, \mu m$ .

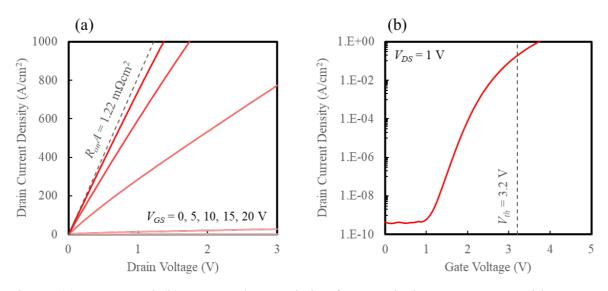

Figure 4 shows (a) the  $J_D$ - $V_{DS}$  and (b)  $J_D$ - $V_{GS}$  characteristics for a DC-MOSFET with  $W_{cell}$  = 1.6 µm. The  $J_D$ - $V_{DS}$  curves display five levels at  $V_{GS}$  = 0, 5, 10, 15, and 20 V. At  $V_{GS}$  = 20 V,  $R_{on}A$  = 1.22 m $\Omega$ cm<sup>2</sup> was obtained at  $J_D$  = 18.9 A/cm<sup>2</sup> ( $I_D$  = 1 A). The  $J_D$ - $V_{GS}$  curve for the same device represents  $V_{th}$  = 3.2 V at  $V_{DS}$  = 1 V and  $J_D$  = 0.3 A/cm<sup>2</sup> ( $I_D$  = 18 mA). The DC-MOSFET using the n<sup>+</sup> source self-aligned process demonstrated desirable static characteristics.

Fig. 4. (a)  $J_D$ - $V_{DS}$  and (b)  $J_D$ - $V_{GS}$  characteristics for a typical DC-MOSFET with  $W_{cell} = 1.6 \,\mu\text{m}$ .

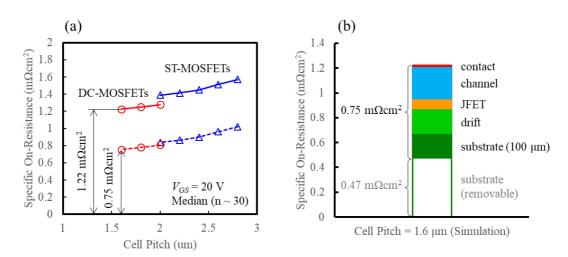

Cell Pitch Dependence of Static Characteristics. Figure 5 (a) depicts the Wcell dependence of RonA (the median value of approximately 30 devices) at  $V_{GS} = 20$  V when the JFET width is varied for both the ST-MOSFETs and DC-MOSFETs. The median values of  $V_{th}$  for the ST-MOSFETs and the DC-MOSFETs with  $W_{cell} = 2.0 \,\mu m$  are 3.9 V and 3.1 V, respectively. The reduced cell pitch shows a trend toward reduced  $R_{on}A$ , especially for the DC-MOSFETs, where the smallest  $R_{on}A$  was obtained. This suggests that the effect of the decrease in  $R_{ch}$  owing to the increased channel density is larger than that of the increase in the JFET resistance ( $R_{JFET}$ ) owing to the wide JFET width, even at  $W_{cell}$  = 1.6  $\mu$ m. The solid lines representing the measurement results include the substrate resistance ( $R_{sub}$ ) with thickness of 360 μm and 333 μm for ST-MOSFETs and DC-MOSFETs, respectively. The dotted lines represent the case where the substrate thickness is reduced to 100  $\mu$ m ( $R_{sub} = 0.20 \text{ m}\Omega\text{cm}^2$ ). Particularly, for the DC-MOSFETs with  $W_{cell} = 1.6 \, \mu \text{m}$ , the  $R_{on}A$  is reduced to 0.75 m $\Omega$ cm<sup>2</sup>. Figure 5 (b) presents the simulated results of the  $R_{on}A$  components for the DC-MOSFET with  $W_{cell} = 1.6 \mu m$ . Excluding the removable substrate resistance of 0.47 m $\Omega$ cm<sup>2</sup>,  $R_{ch}$  is regarded as the largest component despite the high channel density. It suggests that further  $R_{on}A$  reduction is possible by reducing  $W_{cell}$ less than 1.6  $\mu$ m, shortening the channel length ( $L_{ch}$ ) and improving the mobility ( $\mu_{FE}$ ). For example, in DC-MOSFETs with  $W_{cell} = 1.4 \mu m$ , if  $L_{ch}$  is halved and  $\mu_{FE}$  is doubled,  $R_{on}A$  is expected to be  $0.55 \text{ m}\Omega\text{cm}^2$ . In this study,  $L_{ch}$  and  $\mu_{FE}$  are about  $0.46 \text{ }\mu\text{m}$  and  $23 \text{ cm}^2/\text{Vs}$ , respectively.

Fig. 5. (a) Cell pitch dependence of  $R_{on}A$  at  $V_{GS} = 20$  V for both the ST-MOSFETs (blue triangle) and DC-MOSFETs (red circle). The solid and dotted lines indicate the actual measurement results and expectation for a substrate thickness of 100  $\mu$ m, respectively. (b) Simulated results of  $R_{on}A$  components for the DC-MOSFET with  $W_{cell} = 1.6 \mu$ m.

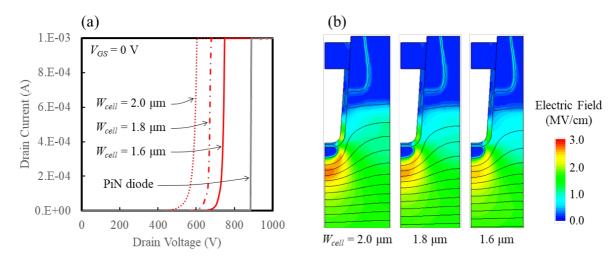

Figure 6 (a) shows the breakdown characteristics at  $V_{GS} = 0$  V for the DC-MOSFETs with  $W_{cell} = 2.0$ , 1.8, and 1.6 µm. The breakdown voltage ( $V_B$ ) tends to increase with the  $W_{cell}$  reduction (JFET width reduction), and the device with  $W_{cell} = 1.6$  µm has  $V_B = 750$  V. However, it is lower than 900 V of PiN diode. Figure 6 (b) shows the simulated results of the electric field at  $V_{DS} = 650$  V for the DC-MOSFETs with each  $W_{cell}$ . The cell pitch reduction suppresses the electric field for the shielding structure at the bottom of the trench gate. This is attributed to the suppression of the potential drop near the channel. Additionally, a reduction in the  $W_{cell}$  also contributed to the relaxation of the electric field for the gate oxide at the bottom corner of the trench gate, which is advantageous for improving the reliability of the trench gate structure.

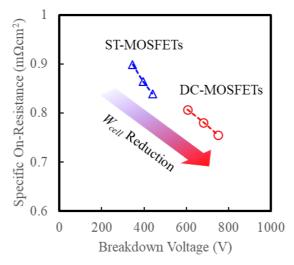

Figure 7 exhibits the  $R_{on}A$  and  $V_B$  trends for the  $W_{cell}$  reduction. The results up to  $W_{cell} = 1.6 \, \mu m$  demonstrated in this study indicate that both the  $R_{on}A$  and  $V_B$  characteristics improve simultaneously with the  $W_{cell}$  reduction. The  $R_{JFET}$  does not increase under this CSL concentration of  $6.0 \times 10^{16} \, \mathrm{cm}^{-3}$  because the JFET width of 0.9  $\mu$ m is wide even with  $W_{cell} = 1.6 \, \mu$ m. The novel structure and process for DC-MOSFETs which enable easy fabrication of the device with  $W_{cell} < 2.0 \, \mu$ m reveal that further  $W_{cell}$  reduction and characteristics improvement are possible in the future.

Fig. 6. (a) Breakdown characteristics at  $V_{GS} = 0$  V for the DC-MOSFETs with  $W_{cell} = 2.0$  (dotted), 1.8 (dashed), 1.6 µm (red solid) and PiN diode (gray solid). (b) Simulation results of the electric field at  $V_{DS} = 650$  V for the DC-MOSFETs with each  $W_{cell}$ .

Fig. 7. Trend of  $R_{on}A$  and  $V_B$  for  $W_{cell}$  reduction.

#### Summary

The first prototype DC-MOSFET applying the n<sup>+</sup> source self-aligned process was demonstrated. DC-MOSFETs with a deep n<sup>+</sup> source and buried ILD can reduce the  $W_{cell}$  efficiently than conventional ST-MOSFETs, and are less prone to process failures. The DC-MOSFET with a minimum  $W_{cell}$  of 1.6 µm was demonstrated, and it exhibited  $R_{on}A = 0.75 \text{ m}\Omega\text{cm}^2$  (in the case of a substrate thickness of 100 µm) and  $V_B = 750 \text{ V}$ . Because the reduced  $W_{cell}$  can simultaneously improve the  $R_{on}A$  and  $V_B$  characteristics, the DC-MOSFET using the n<sup>+</sup> source self-aligned process is one of the promising structures for further development in SiC power MOSFETs.

## Acknowledgements

This work was implemented under a joint research project of Tsukuba Power Electronics Constellations (TPEC). The author, Shinichi Kimoto is assigned from Toshiba Corporation.

## References

- [1] T. Kojima, S. Harada, Y. Kobayashi, M. Sometani, K. Ariyoshi, J. Senzaki, M. Takei, Y. Tanaka and H. Okumura, Jpn. J. Appl. Phys. 55, 04ER02 (2016)

- [2] Y. Fukui, K. Sugawara, R. Tanaka, H. Koketsu, H. Hatta, Y. Miyata, H. Suzuki, K. Taguchi, Y. Kagawa, S. Tomohisa and N. Miura, Mater. Sci. Forum 924, 761 (2018)

- [3] H. Takaya, T. Misumi, H. Fujiwara and T. Ito, Proceedings of the 32<sup>nd</sup> International Symposium on Power Semiconductor Devices and ICs (ISPSD), Austria, 2020, pp. 118-121.

- [4] M. Sampath, A. Salemi, D. Morisette and J. Cooper, Mater. Sci. Forum 1004, 751 (2020)