# Early Burn-In Parasitic Conduction in 500 °C Durable SiC JFET ICs

Submitted: 2022-09-02

Revised: 2022-10-21

Online: 2023-06-06

Accepted: 2022-11-25

Philip G. Neudeck<sup>1,a\*</sup>, David J. Spry<sup>1,b</sup>, Dorothy Lukco<sup>2,c</sup>, Liangyu Chen<sup>3,d</sup>

<sup>1</sup>NASA Glenn Research Center, 21000 Brookpark Road MS 77-1, Cleveland, OH 44135 USA

<sup>2</sup>HX5, LLC, NASA Glenn, 21000 Brookpark Road MS 77-1, Cleveland, OH 44135 USA

<sup>3</sup>Ohio Aerospace Institute, 21000 Brookpark Road MS 77-1, Cleveland, OH 44135 USA

<sup>a</sup>Neudeck@nasa.gov, <sup>b</sup>david.j.spry@nasa.gov,

<sup>c</sup>dorothy.lukco-1@nasa.gov <sup>d</sup>liangyu.chen-1@nasa.gov

Keywords: JFET, Burn-In, Field-FET, Parasitic MOSFET, Mobile Ions, Integrated Circuit

**Abstract.** All prior reports of long-term 500 °C operation of SiC JFET-R ICs have noted the existence of an initial "burn-in" period of changes in measured electrical characteristics for the first few hundred hours oven-testing. This work reports measurements of "burn-in parasitic MOSFET conduction" that can substantially impact the performance of some circuits during initial heat-up of JFET ICs, but then subsequently disappears after a few hours of operation at 500 °C. The behavior appears generally consistent with the known MOS phenomenon of bias-temperature driven redistribution of mobile ionic contamination. Approaches for further mitigating this initial burn-in conduction mechanism are discussed.

## Introduction

Substantial expansion of the practical environmental envelope for integrated circuit (IC) operation offers important benefits to a variety of automotive, aerospace, deep-well drilling, and manufacturing applications [1]. Prior NASA Glenn work has reported fabrication, packaging, and testing of SiC Junction Field Effect Transistor – Resistor (JFET-R) ICs with two levels of interconnect that have uniquely achieved operation in extreme environments including over a year at temperature (T) of 500 °C [2,3]. These reports have noted that the largest observed changes in SiC JFET-R IC electrical properties (prior to eventual passivation cracking induced failure) occur during the initial few hundred hours of high temperature electrical testing. While this circuit behavior in early-testing has been classified as an "initial burn-in" phenomena, the physical mechanisms behind the observed burn-in remain to be investigated. It is important to gain improved understanding of all parameter-drift effects towards achieving mitigation as well as increased technology confidence for infusion. This report describes recent studies of the behavior of one previously identified early burn-in mechanism that we refer to as "burn-in parasitic MOSFET conduction" [4].

# **Background**

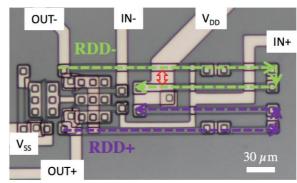

In our prior work [4], we observed large imbalance of resistor conduction in a SiC JFET-R differential amplifier circuit fabricated in the prototype run we denoted as IC Gen. 8 (Fig. 1) that we attributed to parasitic Metal Oxide Semiconductor Field Effect Transistor (MOSFET) conduction. During initial heating above 200 °C under intended amplifier biasing, the n-SiC mesa resistor running beneath the positive power supply V<sub>DD</sub> interconnect trace (denoted by the lighter green dashed line in Fig. 1) exhibited substantially increased current compared to its nearby twin mesa resistor (purple dashed line). The resulting resistance imbalance was fatally detrimental to the operation the during initial heating of the differential amplifier circuit. It was surmised that the +30 V biased V<sub>DD</sub> trace was helping to create a parasitic inversion n-channel MOSFET enabling an additional current path denoted by red arrows between the two adjacent legs of the green-dashed resistor in Fig. 1. In other words,

the  $V_{DD}$  trace functioned as the gate terminal of an inversion channel n-MOSFET formed between the two n-mesas functioning as n-doped source and drain. It was also observed that the resistor current imbalance could be eliminated by applying negative voltage to the  $V_{DD}$  trace for two hours at 300 °C [4].

The observed reversible bias-temperature-time stress behavior appears consistent with mobile positive-charge ion contamination phenomenon well-known to be detrimental to MOS devices [5]. Positive ions in the oxide become mobile at elevated T and are repelled by positive  $V_{DD}$  bias to migrate closer to the SiC-oxide interface beneath the  $V_{DD}$  metal, which in turn reduces the turn-on threshold voltage  $V_{T}$  of the parasitic n-MOSFET. Negative

Fig. 1. Annotated optical image of the IC Gen. 8 differential amplifier that exhibited severe resistance imbalance arising from parasitic MOSFET conduction that formed in the p-type SiC beneath the positively biased V<sub>DD</sub> trace [4].

V<sub>DD</sub> terminal bias high-T attracts positive ions back towards the gate, increasing threshold voltage to turn off the parasitic MOSFET conduction.

After surface analysis confirmed the presence of a mobile ion contaminant (sodium) on IC Gen. 8 SiC JFET-R chips, a concerted effort to eliminate sources of mobile ion contamination in the NASA fabrication laboratory was undertaken, including replacement of chemical and wafer handling hardware. Some contamination mitigation practices of the silicon IC industry were also incorporated into the SiC JFET-R IC process (starting with IC Gen. 9), including the introduction of stoichiometric Low-Pressure Chemical Vapor Deposited (LPCVD) Si<sub>3</sub>N<sub>4</sub> passivation layers as well as p-type "field stop" (also known as "channel-stop") ion implants into regions between n-mesas. Subsequent mask layouts also avoided V<sub>DD</sub>-biased first-layer interconnect (Metal 1) traces spanning/bridging separated n-mesas, especially for the case of analog differential amplifier circuits [6].

#### **Experimental**

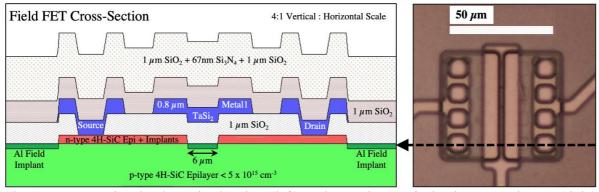

Fig. 2 illustrates the primary test device employed in IC Gen. 10 to study the parasitic MOSFET conduction behavior, wherein the drawing on the left depicts the cross section along the black dashed arrow on the right top view photo (see [2,3] for SEM cross-section of JFET and interconnects from IC 10.1 wafer). This "Field FET" is effectively an inversion channel SiC MOSFET wherein TaSi<sub>2</sub> Metal 1 interconnect functions as a 6  $\mu$ m long by 48  $\mu$ m wide gate terminal between adjacent n-mesas that function as source and drain terminals. Aluminum was implanted at room temperature into the SiC surface field regions between mesas (self-aligned prior to stripping the mesa etch masks) as the field stop implant towards suppressing conduction between separate n-mesas in the IC. Shallow (~ 0.1  $\mu$ m) profiles, doping density near 7 x 10<sup>16</sup> cm<sup>-3</sup> (5 x 10<sup>11</sup> cm<sup>-2</sup> @ 70 keV + 1.8 x 10<sup>11</sup> @ 35 keV) for Wafer 10.1 and 2 x 10<sup>17</sup> cm<sup>-3</sup> (1.4 x 10<sup>12</sup> cm<sup>-2</sup> @ 70 keV + 5.0 x 10<sup>11</sup> cm<sup>-2</sup> @ 35 keV) for

Fig. 2. Cross-sectional schematic drawing (left) and top view optical microscope image (right) illustrating the "Field FET" device structure fabricated on NASA Glenn SiC JFET-R IC Gen. 10 wafers towards characterizing the behavior of parasitic MOSFET conduction mechanism.

Wafer 10.2 were activated along with the n-type SiC JFET-R process implants using SiO<sub>2</sub> capped anneals in nitrogen tube furnace for 100 hours at 1360 °C [2]. Field FET current vs. voltage (I-V) properties were characterized on high-T packaged devices inside air-ambient ovens with gold wires running outside the oven to a terminal strip and connected to computer-controlled DC source measure units (SMU's) that were swept at rates below 1 V/sec. It is worth noting that the high-T packaging process subjects diced chips to 2.5 hours of heat treatment at 600 °C to attach the chip backside to Pt pad patterned on the high temperature co-fired ceramic alumina package with gold thick-film materials [7].

# **Theory**

Simplistically, an inversion-channel n-MOSFET turns on when the applied gate voltage  $V_G$  exceeds its threshold voltage  $V_T$ . If  $V_T$  of the parasitic MOSFET is always larger than  $2xV_{DD}$ , parasitic MOSFET conduction in SiC JFET-R ICs would be suppressed for even the worst case of a  $V_{DD}$  biased Metal 1 trace (+ 25 V) passing overhead of separated n-mesas biased near  $V_{SS}$  (-25 V). Since the shortest n-mesa to n-mesa spacing rule of IC Gen. 10 was 6  $\mu$ m, the long-channel approximation applies for theoretically estimating  $V_T$  of the parasitic MOSFET [5]:

$$V_{T} = V_{FB} + 2\phi_{F} + \frac{\epsilon_{S}t_{ox}}{\epsilon_{ox}} \sqrt{\frac{4qN_{A}}{\epsilon_{S}}} \phi_{F}$$

(1)

where  $t_{ox}$  is the SiO<sub>2</sub> thickness (1 µm for Metal 1 gate, or 2 µm for Metal 2 [2,3]),  $\epsilon_s$  and  $\epsilon_{ox}$  are the 4H-SiC and SiO<sub>2</sub> dielectric constants (8.6 x 10<sup>-13</sup> F/cm and 3.4 x 10<sup>-13</sup> F/cm) and N<sub>A</sub> is the p-type aluminum doping density in the 4H-SiC MOSFET channel region. The  $\emptyset_F$  term is the bulk semiconductor bulk Fermi potential governed by N<sub>A</sub>, T, 4H-SiC intrinsic carrier concentration n<sub>i</sub> (itself a function of T) and reverse substrate bias V<sub>S</sub> applied relative to the grounded MOSFET source:

$$\phi_{\rm F} = \frac{kT}{q} \ln \left( \frac{N_{\rm A}}{n_{\rm i}} \right) + V_{\rm S} \tag{2}$$

where k and q are the Boltzmann and electron charge physical constants. The flat band voltage  $V_{FB}$  is governed by:

$$V_{FB} = \emptyset_{MS} - \frac{Q_F}{C_{OY}} - \frac{Q_M \gamma_M}{C_{OY}} - \frac{Q_{IT}}{C_{OY}}.$$

(3)

The  $\emptyset_{MS}$  term is the gate metal-semiconductor work function difference and  $C_{ox}$  (i.e.,  $\epsilon_{ox}/t_{ox}$ ) is the areanormalized oxide capacitance (3.4 x 10<sup>-9</sup> F/cm<sup>2</sup> for 1 um thick SiO<sub>2</sub>). The charge densities in the insulator are fixed oxide charge QF, charge due to mobile ions in the oxide Q<sub>M</sub>, and interface trap charge Q<sub>IT</sub> in Coulombs/cm<sup>2</sup>. As discussed in [5], the unitless term  $\gamma_{\rm M}$  accounts for the integral average depth position of the mobile charge distributed throughout the oxide thickness:  $\gamma_{\rm M} = 1$  implies the mobile ion charge resides entirely at the oxide-semiconductor interface (where mobile ions have the largest impact on V<sub>FB</sub> and  $V_T$ ), whereas  $\gamma_M = 0.5$  for a uniform mobile ion distribution throughout the oxide thickness. At sufficiently high-T that enables ion migration, y<sub>M</sub> will increase as positive gate bias repels positive mobile ions closer to the SiC/SiO<sub>2</sub> interface, or oppositely y<sub>M</sub> will decrease under negative gate bias as the mobile ions are attracted towards the gate.

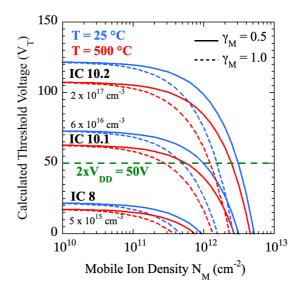

Fig. 3. Plots of theoretical  $V_T$  for turn-on of parasitic MOSFETs as a function of mobile positive ion charge density calculated for three different prototype SiC JFET-R IC processes (see text).

Fig. 3 plots a comparison of theoretical V<sub>T</sub> calculated at 25 °C and 500 °C using Eqs. (1-3) as a function of the areal density of mobile ions in the oxide N<sub>M</sub> (i.e., Q<sub>M</sub>/q in units of #/cm²) for IC Gen. 8 (N<sub>A</sub>  $\leq$  5 x 10<sup>15</sup> cm<sup>-3</sup>), 10.1 (N<sub>A</sub> = 6 x 10<sup>16</sup> cm<sup>-3</sup>) and 10.2 (N<sub>A</sub> = 2 x 10<sup>17</sup> cm<sup>-3</sup>). Bookend values of T and  $\gamma_M$  are compared:  $\gamma_M$  = 0.5 representing a presumed "initial" state of uniform positive ion distribution prior to bias-temperature stressing and "worst case"  $\gamma_M$  = 1.0 wherein all positive ions have (repelled by positive gate bias) piled up at the SiC/SiO<sub>2</sub> interface. As the three IC generations were fabricated using the same metal (TaSi<sub>2</sub>) and insulator processing, it is reasonable to surmise minimal differences in  $\phi_{MS}$ , Cox, Q<sub>F</sub>, and Q<sub>IT</sub> terms in Eq. 3 amongst the three devices. T-independent values falling within literature spreads for  $\phi_{MS}$  = 1 V, Q<sub>F</sub> = -1 x 10<sup>12</sup> cm<sup>-2</sup> and Q<sub>IT</sub> = 1 x 10<sup>12</sup> cm<sup>-2</sup> were assumed for the Fig. 3 calculation, with the understanding that more realistic T-dependent values specific to the SiC JFET-R process remain to be ascertained by future work.

Increasing T from 25 °C to 500 °C has far less impact on Fig. 3 plotted V<sub>T</sub> than 4H-SiC doping N<sub>A</sub>. The typically employed SiC JFET-R 2xV<sub>DD</sub> of 50 V is marked by the green dashed line in the plot. For IC Gen. 8 that did not employ a field-stop p-type implant, V<sub>T</sub> is well below 2xV<sub>DD</sub> = 50 V regardless of N<sub>M</sub> indicating susceptibility to parasitic MOSFET channel formation. The p-type field-stop implants employed in IC Gen. 10 devices desirably push V<sub>T</sub> above 50 V for N<sub>M</sub> below 2 x 10<sup>11</sup> cm<sup>-2</sup>. However, Fig. 3 indicates that burn-in parasitic MOSFET channel formation remains a risk

in IC Gen. 10.2 as ion contamination density  $N_M$  exceeds

$10^{12} \text{ cm}^{-2}$ .

#### **Measurements and Results**

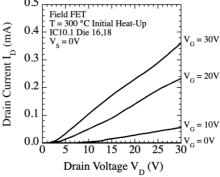

Data shown in Figs. 4-7 illustrate examples of the main temperature-bias-time dependent electronic behaviors observed in the IC Gen. 10 Field FET measurements. The packaged Field FET exhibits insignificant conduction until the initial heat-up of the Field FET exceeds 150 °C. With further T increase, parasitic conduction arises under positive Metal 1 gate bias that peaks around 300 °C. Fig. 4 plots a drain current I<sub>D</sub> vs. drain voltage V<sub>D</sub> characteristic measured with the device at 300 °C during initial heating up to 500 °C roughly corresponding to conditions that largest Field FET currents were observed. It is important to note that V<sub>G</sub> bias was applied for 60 seconds prior to the start of each V<sub>D</sub> sweep for intended purpose of promoting parasitic conduction. The I<sub>D</sub> vs. V<sub>D</sub> characteristic does not saturate in a manner consistent with  $V_T < 10 \text{ V}$  indicated by initial turn-on at  $V_G \le 10$  V, which suggests that electrically significant ion migration is occurring over the several-minute duration of the SMU I-V measurement.

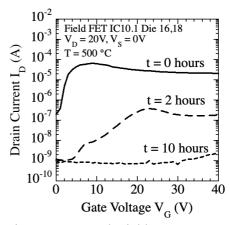

Fig. 5 illustrates the SMU measured Field FET drain current  $I_D$  vs. gate voltage  $V_G$  behavior of the Fig. 4 device measured at constant  $V_D = 20$  V drain bias for 0 hours, 2 hours, and 10 hours of electrically biased testing time (t) from initially reaching 500 °C. At 0 hours, the  $I_D$ - $V_G$  characteristic near  $V_G = 0V$  exhibits exponentially increasing current consistent with MOSFET sub-threshold conduction but then saturates and declines following device turn-on. Most importantly, the Field FET current effectively vanished by 10 hours to nA levels consistent with the leakage current floor of the 500 °C packages.

Fig. 4. Measured Field FET I-V characteristics demonstrating increasing parasitic MOSFET conduction with positive gate bias as the device is initially heated to 300 °C (during ramp to 500 °C). No parasitic MOSFET turn-on is observed prior to heating.

Fig. 5. Measured Field FET  $I_D$  vs.  $V_G$  plots demonstrating extinction of parasitic MOSFET conduction within 10 hours of biased testing at 500 °C.

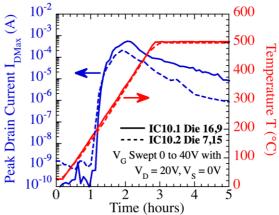

It is worth noting that drain current peaks in Fig. 5 at different V<sub>G</sub>. Given this observed behavior, the term I<sub>DMax</sub> is defined to be the peak drain current observed during I<sub>D</sub> vs. V<sub>G</sub> sweeps measured at under fixed positive drain bias. Fig. 6 plots a comparison between IC10.1 and 10.2 peak Field FET current I<sub>DMax</sub> measured during I<sub>D</sub> vs V<sub>G</sub> sweeps under identical initial T ramps to 500 °C. The behavior is similar, but the IC 10.2 Field FET exhibits lower I<sub>DMax</sub> peak than the IC 10.1 device.

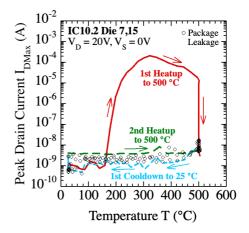

Fig. 7 displays the behavior of I<sub>DMax</sub> for the IC 10.2 device over two thermal ramps to 500 °C. Between the thermal ramps, the device was burned in at 500 °C for 141 hours and cooled to 25 °C. The 40 V open-circuit package leakage measured between adjacent pads is also plotted. The large parasitic MOSFET conduction observed for the first ramp completely vanishes during the 500 °C burn-in and does not return during subsequent thermal ramping.

X-ray Photoelectron Spectroscopy (XPS) surface analysis conducted following electrical testing observed K (0.6-0.8 at%), Fe (0.4-0.6 at%), and Na (0.3-0.4 at%). The Na was removed after a 1-minute (~ 100 Å) in-situ sputter, but trace amounts of K and Fe remained. The Pt conductive traces showed Ga (6 at%), Fe (3 at%), and Na (2 at%) contaminants on their surfaces. Again, Na was removed after sputtering, but smaller amounts of Ga and Fe remained. The white Al<sub>2</sub>O<sub>3</sub> field regions of the packages showed Mg (4-5 at%), Na (1-2 at%), and Ca (0.5-0.9 at%). The die attach material was found to be pure gold after C and O surface contamination was removed by sputtering. Other than a trace amount of S on one of the samples, no other trace elements were detected on the die attach material.

Fig. 6. Comparison of IC10.1 and 10.2 peak Field FET drain current  $I_{DMax}$  observed during identical initial T ramps to 500 °C.

Fig. 7. Plot of IC10.2 peak parasitic MOSFET current  $I_{DMax}$  vs. T recorded during 1st heatup and 141 hour bake at 500 °C (red), cooldown (blue), and 2nd heatup to 500 °C (green). The measured package leakage current is also plotted.

## **Discussion**

Despite processing revisions implemented since IC Gen. 8, the results of this study indicate that parasitic MOSFET formation remains as an issue for design and deployment of SiC JFET-R ICs. Given the experimental evidence gathered to date, O<sub>2</sub>:N<sub>2</sub> (simulated air) annealing of the wafers prior to dicing should be attempted to ascertain if effective burn-in after heating in oxygen might be accomplished prior to dicing and packaging. Additionally, alternative packaging and ovens should be investigated towards minimizing mobile ion contamination. Presently, the wafer processing is done in reducing environments such as Ar:H or N:H forming gas with dielectrics deposited using tetraethyl orthosilicate (TEOS), ammonia, and dichlorosilane precursors. These chemistries could conceivably leave non-fully reacted ions at the SiC/SiO<sub>2</sub> interface. Additional impurities (including Fe) in the TaSi<sub>2</sub> sputtering and/or reactive ion etching could be left at the metal interconnect surfaces. All these possible sources of mobile ions might be passivated or migrate out of the sensitive MOSFET channel region under electrically biased high-T air annealing. The observed permanent extinction of parasitic MOSFET conduction upon exposure to 500 °C suggests that mobile ion source is finite in nature. If the mobile ions were supplied by the ceramic packaging materials, such an impurity source would be expected to sustain parasitic conduction for far longer duration (as a nearly indefinite supply of impurities) inconsistent with the observed short-term burn-in electrical behavior.

Engineering tradeoffs remain to be investigated for accomplishing further reduction of burn-in parasitic MOSFET conduction, complete suppression of which would improve technology capability and infusion. For example, Metal 1 traces tied to -Vss bias can be routed to interrupt parasitic channel MOSFET conduction between mesas/devices residing beneath Metal 2 V<sub>DD</sub> power. Greatly increased field-stop implant doping can also shift the parasitic MOSFET V<sub>T</sub> towards withstanding higher contamination levels, but this could also require significantly higher implant and/or activation temperatures. If completely successful, the higher field-stop implant dose approach would remove metal routing restrictions to achieve higher circuit packing density while perhaps also supporting lower-purity packaging materials and operational environments.

#### Conclusion

Further electrical studies of parasitic MOSFET conduction that can adversely impact SiC JFET-R IC operation during the first hours of high temperature operation have been described. While burn-in and layout strategies exist for effective mitigation of this short-duration burn-in effect, it is hoped that future work will lead to complete elimination of this phenomenon.

# Acknowledgements

This work conducted by NASA Glenn Research Center in Cleveland, OH USA with funding from the NASA Science Mission Directorate under the High Operating Temperature Technology (HOTTech) and Long-Lived In-Situ Solar System Explorer (LLISSE) projects. The authors are grateful to G. Hunter, G. Beheim, K. Moses, J. Gonzalez, M. Mrdenovich, S. Rajgopal, R. Okojie, A. Trunek, R. Buttler, A. Miller, A. Izadnegahdar, S. Booth, C. Chang, W. John, F. Lam, T. Vanderwyst, L. Greer, D. Centeno-Gomez, M. Lienhard, and T. Kremic for their support.

Notice for Copyrighted Information: This manuscript is a joint work of employees of the National Aeronautics and Space Administration and employees of Ohio Aerospace Institute under Contract No. 80GRC020D0003 with the National Aeronautics and Space Administration. The United States Government may prepare derivative works, publish, or reproduce this manuscript and allow others to do so. Any publisher accepting this manuscript for publication acknowledges that the United States Government retains a non-exclusive, irrevocable, worldwide license to prepare derivative works, publish, or reproduce the published form of this manuscript, or allow others to do so, for United States Government purposes.

#### References

- [1] J. Cressler and H.A. Mantooth, Extreme Environment Electronics, CRC Press, Boca Raton, 2013.

- [2] P. Neudeck et al., Proc. 2018 IMAPS Int. Conf. High Temperature Electronics, p. 71.

- [3] P. Neudeck and D. Spry, Mat. Sci. Forum 1004 (2020) 1057.

- [4] D. Spry et al., Mat. Sci Forum 828 (2016) 1112.

- [5] R.F. Pierret, Field Effect Devices, in Modular Series on Solid State Devices, Vol. 4, Addison-Wesley, Reading MA, 1983.

- [6] P. Neudeck and D. Spry, Graphical Primer of NASA Glenn SiC JFET Integrated Circuit (IC) Version 12 Layout, https://ntrs.nasa.gov/citations/20190025716 (2019).

- [7] L. Chen et al., Proc. 2022 IMAPS Int. Conf. High Temperature Electronics Network, July 18-20, Oxford, United Kingdom, https://ntrs.nasa.gov/citations/20220010638.