# Design of Monolithically Integrated Temperature Sensors in 4H-SiC JFETs

Submitted: 2023-09-01

Accepted: 2024-04-10

Online: 2024-08-22

F. Monaghan<sup>1,a\*</sup>, A. Martinez<sup>1,b</sup>, J.E. Evans<sup>1,c</sup>, C. Fisher<sup>1,d</sup>, O. Guy<sup>1,e</sup> and M. Jennings<sup>1,f</sup>

<sup>1</sup>Centre for Integrative Semiconductor Materials, Swansea University, Fabian Way, Swansea SA1 8EN, UK

<sup>a</sup>909302@swansea.ac.uk, <sup>b</sup>a.e.martinez@swansea.ac.uk, <sup>c</sup>j.e.evans@swansea.ac.uk, <sup>d</sup>c.a.fisher@swansea.ac.uk, <sup>e</sup>o.j.guy@swansea.ac.uk <sup>f</sup>m.r.jennings@swansea.ac.uk

**Keywords:** Monolithic integrated sensor, P-type SiC, JFET, incomplete ionization, silicon carbide, temperature sensor

**Abstract.** In this paper we study and compare two designs of a temperature sensor monolithically integrated to a vertical SiC JFET. One sensor utilizes the standard JFET P+ aluminum gate implantation scheme. The advantage of this sensor is that the integration with a JFET process flow can be achieved with no additional process steps or mask layers. The other sensor uses a combination P-body and a low energy P+ implantation scheme, typically seen in MOSFETs. Both sensors exploit the variation of resistance with temperature of Al doped SiC. Drift-Diffusion simulations of both designs are carried out at fixed temperatures, exhibiting an excellent ~53% relative reduction in sensor resistance from 300 to 450K. However, neither design shows linear behavior with temperature, beginning to saturate at 450K. Electrothermal simulations are also deployed to verify the sensor robustness as the sensor is locate relatively far from the JFET junction. Due to the high thermal conductivity of SiC, the sensor average temperature follows closely the junction temperature. Current crowding (or 2D effects) close to the contact edges is observed in both sensors. We also deploy a simple analytical model to calculate the resistance as a function of the temperature for both sensors. The model agrees with the drift-diffusion calculations, however due to the 2D nature of current flow, a maximum 19.6% relative error is obtained. In general, both sensors deployed similar relative sensitivity, however the P-body sensor resistance changes in a range of  $10.6k\Omega$  to  $4.95k\Omega$  compared to  $700\Omega$  to  $330\Omega$  for the P+ sensor.

# Introduction

Sensors and electrical control systems are desired for harsh environment operation, in applications such as natural resource extraction, automotive, aerospace and energy production. Silicon based electronics are typically limited to a maximum operating temperature of 200°C due high leakage currents [1]. Due to Silicon Carbides (SiC) larger bandgap of 3.26eV, leakage current is significantly improved, and thus is more suited to high temperature power electronics. Furthermore, the excellent thermal stability of SiC and radiation hardness enables operation in extreme environments such as nuclear systems or space exploration [2]. Typically, temperature sensors are located outside the device packaging away from the device surface. Package temperature is expected to be vastly different to internal device temperature due to the typically poor thermal conductivity of the passivation layers alongside packaging materials. As a result, monolithic integration of a temperature sensor would provide valuable real-time information on the junction temperature (T<sub>i</sub>) of the device.

A common approach to developing such a sensor is to monitor a temperature sensitive parameter, such as forward current ( $I_f$ ) in an Schottky Barrier Diode [3]. Another such design is to use a region uniformly doped with dopants that sit deep in the SiC bandgap. Due to large activation energies, the dopants are significantly affected by incomplete ionization [4]. This results in a varying in the conductivity of the doped region with temperature. In this case, using aluminum, a common P-type dopant which as an ionization energy of 265meV is suitable [5].

Owing to SiC's wider bandgap and excellent thermal conductivity, in theory SiC devices can operate at higher temperatures than silicon devices. In practice, due to thermal limits of aluminum

wire bonds, and silicon gel used in encapsulation, devices are limited to under 200°C. Furthermore, SiC MOSFETs gate oxide utilizes the SiC/SiO<sub>2</sub> interface. This interface typically has an order of magnitude higher density of interface traps (D<sub>it</sub>) than the Si/SiO<sub>2</sub> interface, which hampers SiC MOSFETs reliability and thus also its ability to operate at extreme temperatures. The SiC gate oxide interface has been an active area of research for the past 15 years and is still being improved to this day [6], [7].

JFETs do not feature a gate oxide, and as such have great potential in high temperature, high reliability applications. In this work, we propose a lateral P+ temperature sensor which utilizes the same implantation schedule as a standard JFET P-type gate implant. This enables the integration of such a sensor into a JFET fabrication process without additional mask layers, or process steps. The second proposed design utilizes a traditional MOSFET P-body and shallow P+ implant schedule, as seen in [4]. This would require an additional mask layer, and further adaption of the JFET process flow. In the following sections, we evaluate the sensors capabilities using a Drift-Diffusion model.[8] This allowed assessment of the sensitivity and linearity of both designs over a temperature range of 300-450K. A simple model has been developed to illustrate the main physical phenomena the sensor experiences with temperature variation, namely increase in dopant ionization and mobility degradation. Electrothermal simulations are also completed to ensure that the sensor temperature will accurately reflect the junction temperature of the device.

# **Device and Simulation Methodology**

In SiC, the impurity level for aluminum sits relatively deep compared to the thermal energy  $k_BT$  (265meV). Due to the deep level of the aluminum dopant, it is expected that not all the dopants present in the lattice are ionized in the 300-450K temperature range. The quadratic equation to find the density of ionized dopants or the free hole concentration (p) as a function of  $N_A$  (acceptor concentration),  $E_A$  (activation energy of the dopant) and  $N_V$  (effective density of states of the valence band) is given by.[9]

$$p(N_a, T) = \frac{N_A}{1 + g_A \frac{p}{N_V} \exp\left(\frac{E_A}{k_B T}\right)}$$

(1)

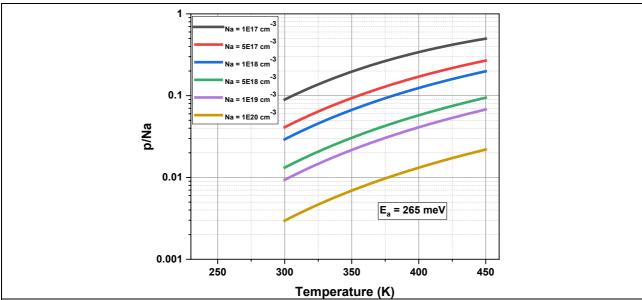

Where  $k_B$  is Boltzmann's constant, and  $g_A$  is the degeneracy factor for acceptor impurities, equal to 4 in SiC. As stated in the introduction, the aluminum energy level considered for this model is 265meV [5]. Fig. 1 shows Eq.1 plotted as a function of T for multiple values of  $N_a$ .

**Fig.1.** Calculated ratio of active carriers to aluminum impurities in P-type SiC, plotted against temperature. Different aluminum concentrations ranging from 1E17 cm<sup>-3</sup> to 1E20 cm<sup>-3</sup> have been considered.

As is clearly shown above in Fig.1, as  $N_A$  increases the ratio of p to  $N_A$  drastically reduces at all temperatures. Therefore, at higher values of  $N_A$ , the effect of incomplete ionization is considerably larger, resulting in ~10% activation for  $N_A = 1E19$  cm<sup>-3</sup> at 500K, compared to 65% for  $N_A = 1E17$  cm<sup>-3</sup> at the same temperature. The carrier mobility degradation due to dopants and phonons is parametrized by using Eq. 2. [9]. The 4H-SiC values for the parameters  $\mu_{max}$ ,  $\mu_{min}$ ,  $N_{ref}$ ,  $\gamma$  and  $\alpha$  are shown below in Table 1. [10]

$$\mu_h(T, N_a) = \left(\mu_{min} + \frac{\mu_{max} - \mu_{min}}{1 + \left(\frac{p(N_a, T)}{N_{ref}}\right)^{\gamma}}\right) \times \left(\frac{T}{300}\right)^{\alpha}$$

(2)

Table 1. Material dependent coefficients for 4H-SiC to be used in the mobility model presented in Equation 2. [10].

| Symbol            | Value                | Unit                  |

|-------------------|----------------------|-----------------------|

| $\mu_{	ext{max}}$ | 125                  | [cm <sup>2</sup> /Vs] |

| $\mu_{min}$       | 15.9                 | $[cm^2/Vs]$           |

| N <sub>ref</sub>  | $1.7 \times 10^{19}$ | [cm <sup>-3</sup> ]   |

| γ                 | 0.34                 | 1                     |

| α                 | 2.15                 | 1                     |

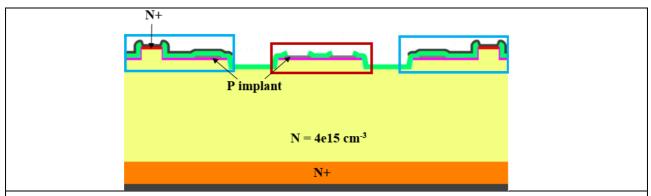

The doping profile of the proposed monolithic sensor, alongside active JFET channels is shown in Fig 2. The drift doping  $N_D$  was set to 4E15 cm<sup>-3</sup>, with a layer thickness of  $10\mu m$ . Additionally, a standard 350 $\mu$ m substrate thickness with a doping of 1E19 cm<sup>-3</sup> was used.

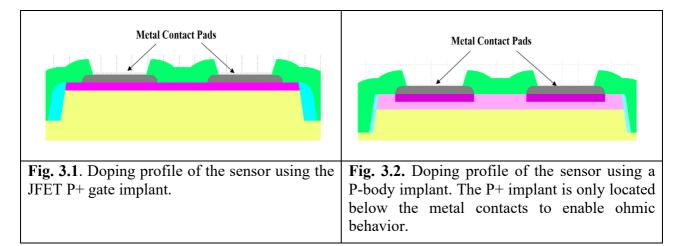

The JFET P+ implant has a target concentration of 1E20 cm<sup>-3</sup>, whilst the MOSFET P-body and P+ ohmic implants have target concentrations of 5E17 cm<sup>-3</sup> and 1E20 cm<sup>-3</sup>, respectively. These doping profiles are shown in Fig 3.1. and Fig 3.2. The JFET P+ and P-body implant have been modelled as box profiles with a depth of 1µm. The implants were simulated using kinetic Monte Carlo simulations.[11] To achieve the 1µm box profile, a total of 5 individual implant shots were used, with energies ranging from 40-680keV. Further explanation of Monte Carlo calculation in Synopsys can be found in [12]. The distance between sensor contact pads is modelled as 40µm and contacts are 2µm wide, giving a total sensor length of 44µm. The sensor extends 100µm in the Z-direction.

Fig. 2. Doping profile of the proposed design of a monolithically integrated temperature sensor in a vertical JFET. The sensor is highlighted in red, and JFET active cells are highlighted in blue.

The calculation of current-voltage characteristics utlises the drift-diffusion approach combined with the Poisson equation. Fermi-Dirac statistics are used to high carrier concentrations (>10<sup>19</sup> cm<sup>-3</sup>) being present in the both the P+ regions and the active area of the JFET cells.[13] Bandgap narrowing is also considered. Carrier recombination is captured by both Shockley-Read-Hall (SRH) and Auger models at high concentrations.[14] The doping dependance of the carrier mobility due to lattice (phonon), coulomb and impurity scattering is active. [10] Additionally, the effect of the anisotropic 4H-SiC lattice is also considered. [10] All parameters used for the incomplete ionization model are shown in Table 1. For electrothermal simulations, to solve the heat equation, thermal resistances are used on the top and bottom of the device, and Neumann boundary conditions for the lateral (left/ right) boundary.

#### **Results and Discussion**

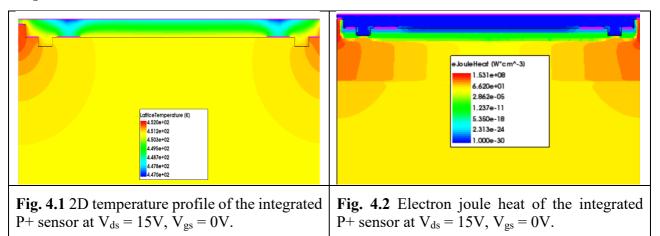

An electrothermal simulation was firstly completed to verify the main localized sources of power dissipation in the JFET active cells, and furthermore how this translated to the sensor. Fig. 4.1 Shows the 2D temperature profile of the P+ sensor at  $V_{ds} = 15V$ ,  $V_{gs} = 0V$ . The temperature is highest in the JFET channels, which is the highest resistance region of the device. This is reflected in the electron joule heat profile of the device, shown in Fig. 4.2.

It is also observed that the blanket deposited dielectric on the topside of the device, intended to imitate passivation layers on a practical device, experiences a large temperature gradient compared to the rest of the structure. This is due to the poor thermal conductivity of dielectrics, in this case SiO<sub>2</sub>.

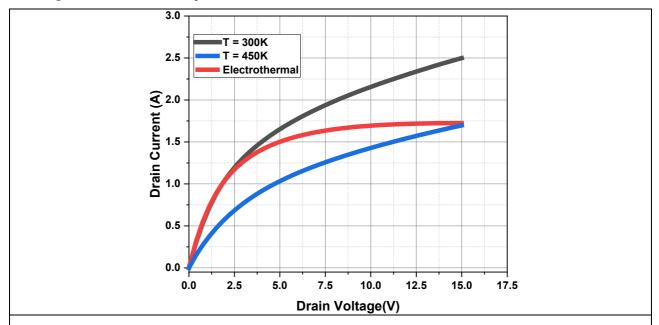

Output characteristics at  $V_{gs} = 0V$  for both electrothermal and fixed temperature values of 300K and 450K are shown below in Fig. 5. The electrothermal curve closely resembles the 300K at low  $V_{ds}$ , due to the small power dissipation, and thus  $T_j$  stays close to 300K. As  $V_{ds}$  increases, the power dissipation of the device vastly increases, resulting in  $T_j$  to increase significantly. For the JFET active cells, as  $T_j$  increases the electron mobility degrades significantly due to elevated levels of phonon

scattering. Thus, the conductivity and therefore  $I_{ds}$  reduces in the JFET active cells as  $T_j$  increases. As  $V_{ds}$  approaches 15V, the electrothermal curve closely resembles the fixed 450K curve. This agrees with Fig. 4.1, which shows  $T_i$  is close to 450K at  $V_{ds} = 15V$ .

**Fig. 5.** JFET output characteristics at Vgs = 0V for fixed temperatures of 300K and 450K, compared to the output characteristic from an electrothermal simulation.

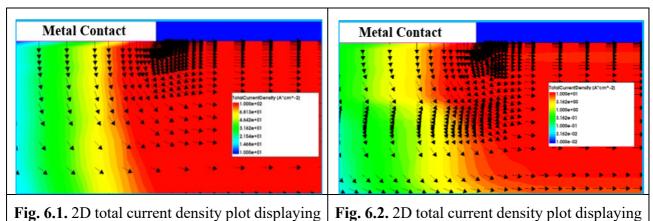

When one of the sensor contacts is biased a nominal amount whilst the other is grounded, current flow between the sensor contacts occurs. Current crowding effects are observed at the contact edges in both designs. This is shown below in Fig. 6.1 and Fig. 6.2 for the P+ and P-body sensor, respectively. Due to the higher resistance path of travelling through the P-body region below the contact instead of travelling through the P+ region, a greater degree of current crowding in the P-body design is observed. This may induce contact degradation in practice. Conversely, as the P+ sensor possesses uniform P+ doping throughout the whole sensor region, thus current crowding is reduced. This current crowding is a 2D effect, as the current flow is two dimensional.

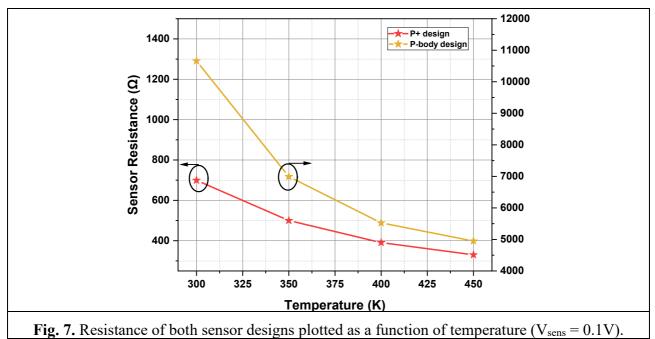

Sensor resistance ( $R_{sens}$ ) was tested at fixed temperatures in the range of 300-450K for both designs.  $R_{sens}$  as a function of temperature is shown below in Fig. 7. The P+ design has a far lower resistance of  $700\Omega$  at 300K, compared to  $10.6k\Omega$  for the P-body design. This is expected, as the conductivity of the P+ sensor should be considerably higher, due to  $N_A$  being 100 times higher than the P-body. Both designs exhibit an excellent ~53% relative reduction in resistance at 450K compared to 300K to 330 $\Omega$  and 4.95k $\Omega$ , respectively. This is 40% higher than the sensitivity observed in [15] over the same temperature range.

current vectors for the P-body.

current vectors for the P+ sensor.

However, it is recognized that  $R_{sens}$  does not behave linearly with temperature and is approaching saturation at 450K. Between 400K and 450K, the P+ sensor experiences an 8% reduction in  $R_{sens}$ , compared to 29% between 300K and 350K. The P-body sensor is more severely affected – with a 11% and 35% reduction over the same temperature ranges. Primarily, this is due to the diminishing impact of incomplete ionization around 450K, whilst simultaneously  $\mu_h$  continuously degrades as temperature increases. Thus, incomplete ionization and  $\mu_h$  partially compensate for each other at 400-450K temperatures, result in resistivity saturating.

The behavior of the  $R_{sens}$  for both designs' shown in Fig. 7 can be explained by a simple model that combines Eq. 1 and Eq. 2 to calculate sensor resistance. This model considers the sensor as a uniform section of doped 4H-SiC in which the current flow is assumed homogeneous, with contacts located at each end. This is a crude representation of the sensors depicted in Fig 3.1/3.2. For this model, both an area A and a length L must be defined to calculate  $R_{sens}$  from the resistivity. Although the total length of the sensor is 44 $\mu$ m, due to the current crowding effects shown in Fig. 6.1 and Fig. 6.2, the total length of the sensor is reduced to 41 $\mu$ m. The width in the Z-direction at 100 $\mu$ m as previously stated. For the depth of sensor, it is assumed that there is minimal vertical current crowding in the bulk of the sensor. Therefore, the depth of the sensor is set to the maximum implantation depth of 1 $\mu$ m.

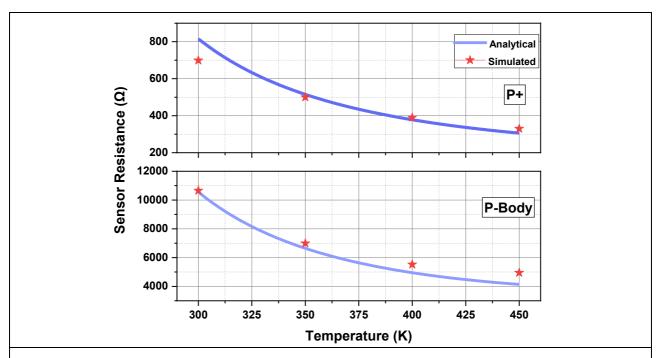

The analytical model closely agrees with the simulated  $R_{sens}$  values for both designs, at all temperatures modelled, as shown below in Fig. 8. At 300K, the model predicts a  $R_{sens}$  value of  $815\Omega$  for the P+ sensor,  $115\Omega$  higher than the drift-diffusion simulation. At 450K, the model predicts  $R_{sens} = 306\Omega$ , compared to the simulated  $330\Omega - a$  7.2% difference. The P-body design is also predicted accurately at room temperature, with a predicted  $R_{sens} = 10556\Omega$  compared to  $10660\Omega - a < 1\%$  absolute error. At high temperature, the analytical model diverges slightly for the P-body sensor, predicting to be 16.7% lower than simulated at  $R_{sens} = 4137\Omega$  in contrast to 4950  $\Omega$ . In general, the model has a minimum 19.6% accuracy over this temperature range. This is to be expected due as the model assumes uniform current flow through the sensor, which our simulation demonstrated is not the case.

**Fig. 8.** Comparison of simulated sensor resistance to analytical model over the 300-450K temperature range.

## **Summary**

We have carried out drift-diffusion/electrothermal simulations of a vertical 4H-SiC JFET with a monolithically integrated temperature sensor. The sensor is based in the incomplete ionization of Aluminum dopants in SiC. Two sensor designs have been studied. One design utilizes deep P+ doping and thus is more suitable for integration into a JFET fabrication process. The other follows the standard MOSFET P-body profile. The resistance calculated by the drift-diffusion method agreed within a 17 % error, with a simple analytical model that consider the sensor as a p-doped 4H-SiC region. The deviation between the model and simulation is expected to be associated to two dimensional crowding effects of the current flow close to the metal contacts. The P-body design experienced a larger current crowding effect at the corner of the sensor contacts, which in practice could affect the reliability of the device. The effect of incomplete ionization on the hole concentration induces larger changes in resistance between 300-350K compared to 400-450K, where sensor resistance begins to saturate. The 2D thermal profiles from electrothermal simulation show that sensor temperature follows close the JFET junction temperature in the range of temperatures studied. Neither sensor exhibits linear behavior in the range of temperature studied. From the fabrication point of view, implementing the P-body design into a JFET process would result in a further mask layer being required, unlike the P+ design. Further work will include fabricating the P+ integrated sensor design to verify the simulation work.

### References

- [1] L. C. Yu, G. T. Dunne, K. S. Matocha, K. P. Cheung, J. S. Suehle, and K. Sheng, 'Reliability Issues of SiC MOSFETs: A Technology for High-Temperature Environments', *IEEE Transactions on Device and Materials Reliability*, vol. 10, no. 4, pp. 418–426, Dec. 2010, doi: 10.1109/TDMR.2010.2077295.

- [2] N. G. Wright, A. B. Horsfall, and K. Vassilevski, 'Prospects for SiC electronics and sensors', *Materials Today*, vol. 11, no. 1, pp. 16–21, Jan. 2008, doi: 10.1016/S1369-7021(07)70348-6.

- [3] S. Rao, L. Di Benedetto, G. Pangallo, A. Rubino, S. Bellone, and F. G. Della Corte, '85–440 K Temperature Sensor Based on a 4H-SiC Schottky Diode', *IEEE Sensors Journal*, vol. 16, no. 17, pp. 6537–6542, Sep. 2016, doi: 10.1109/JSEN.2016.2591067.

- [4] M. Berthou, P. Godignon, and J. Millán, 'Monolithically Integrated Temperature Sensor in Silicon Carbide Power MOSFETs', *IEEE Transactions on Power Electronics*, vol. 29, no. 9, pp. 4970–4977, Sep. 2014, doi: 10.1109/TPEL.2013.2289013.

- [5] A. Koizumi, J. Suda, and T. Kimoto, 'Temperature and doping dependencies of electrical properties in Al-doped 4H-SiC epitaxial layers', *Journal of Applied Physics*, vol. 106, no. 1, p. 013716, Jul. 2009, doi: 10.1063/1.3158565.

- [6] S. M. Thomas, M. R. Jennings, Y. K. Sharma, C. A. Fisher, and P. Mawby, 'Impact of the Oxidation Temperature on the Interface Trap Density in 4H-SiC MOS Capacitors', *Materials Science Forum*, vol. 778–780, pp. 599–602, 2014, doi: 10.4028/www.scientific.net/MSF.778-780.599.

- [7] H. Chen, K. Yu, J. Ding, C. Li, J. Wang, and Y. Wang, 'Comprehensive Investigation of Gate Oxide Instability in 4H-SiC MOSFETs and MOS Capacitors Under High Gate Bias Stress', *IEEE Transactions on Electron Devices*, pp. 1–8, 2023, doi: 10.1109/TED.2023.3294458.

- [8] Synopsys Inc., 'Sentaurus Device User Guide: Version S-2021.06', Jun. 2021.

- [9] M. Rambach, A. J. Bauer, and H. Ryssel, 'Electrical and topographical characterization of aluminum implanted layers in 4H silicon carbide', *physica status solidi (b)*, vol. 245, no. 7, pp. 1315–1326, 2008, doi: 10.1002/pssb.200743510.

- [10] W. J. Schaffer, G. H. Negley, K. G. Irvine, and J. W. Palmour, 'Conductivity Anisotropy in Epitaxial 6H and 4H Sic', *MRS Online Proceedings Library*, vol. 339, no. 1, pp. 595–600, Dec. 1994, doi: 10.1557/PROC-339-595.

- [11] S. Tian, 'Monte Carlo Simulation of Ion Implantation in Crystalline SiC With Arbitrary Polytypes', *IEEE Transactions on Electron Devices*, vol. 55, no. 8, pp. 1991–1996, Aug. 2008, doi: 10.1109/TED.2008.926664.

- [12] F. Monaghan, A. Martinez, F. Craig, and M. Jennings, 'Impact of Dimensions and Doping on the Breakdown Voltage of a Trench 4H-SiC Vertical JFET', *Key Engineering Materials*, vol. 948, pp. 69–75, 2023, doi: 10.4028/p-e6c13m.

- [13] P. P. Altermatt *et al.*, 'Numerical modeling of highly doped Si:P emitters based on Fermi–Dirac statistics and self-consistent material parameters', *Journal of Applied Physics*, vol. 92, no. 6, pp. 3187–3197, Aug. 2002, doi: 10.1063/1.1501743.

- [14] A. Galeckas, J. Linnros, V. Grivickas, U. Lindefelt, and C. Hallin, 'Auger recombination in 4H-SiC: Unusual temperature behavior', *Appl. Phys. Lett.*, vol. 71, no. 22, pp. 3269–3271, Dec. 1997, doi: 10.1063/1.120309.

- [15] K. Han and B. J. Baliga, '1.2-kV 4H-SiC SenseFET With Monolithically Integrated Sensing Resistor', *IEEE Electron Device Letters*, vol. 41, no. 3, pp. 437–440, Mar. 2020, doi: 10.1109/LED.2020.2964773.