# 150 mm SiC Engineered Substrates for High-Voltage Power Devices

Submitted: 2021-10-21

Revised: 2022-02-14

Online: 2022-05-31

Accepted: 2022-03-10

Séverin Rouchier<sup>1,a\*</sup>, G. Gaudin<sup>1b</sup>, J. Widiez<sup>2,c</sup>, F. Allibert<sup>1,d</sup>, E. Rolland<sup>2,e</sup>, K. Vladimirova<sup>2,f</sup>, G. Gélineau<sup>2,g</sup>, N. Troutot<sup>2,h</sup>, C. Navone<sup>2,i</sup>, G. Berre<sup>3,j</sup>, D. Bosch<sup>3,k</sup>, Y.L. Leow<sup>3,l</sup>, A. Duboust<sup>3,m</sup>, A. Drouin<sup>1,n</sup>, J-M. Bethoux<sup>1,o</sup>, R. Boulet<sup>1,p</sup>, A. Chapelle<sup>1,q</sup>, E. Cela<sup>1,r</sup>, G. Lavaitte<sup>1,s</sup>, A. Bouville-Lallart<sup>1,t</sup>, L. Viravaux<sup>1,u</sup>, F. Servant<sup>2,v</sup>, S. Bhargava<sup>3,w</sup>, S. Thomas<sup>3,x</sup>, I. Radu<sup>1,y</sup>, C. Maleville<sup>1,z</sup>. W. Schwarzenbach<sup>1,ab</sup>

<sup>1</sup>Soitec SA, Bernin (France), <sup>2</sup>CEA-LETI, Grenoble (France), <sup>3</sup>Applied Materials, Bernin (France)

aseverin.rouchier@soitec.com, bgweltaz.gaudin@soitec.com, cjulie.widiez@cea.fr, dfrederic.allibert@soitec.com, emmanuel.rolland@cea.fr, fkremena.vladimirova@cea.fr, gguillaume.gelineau@cea.fr, hnicolas.troutot@cea.fr, ichristelle.navone@cea.fr, iGuillaume\_Berre@amat.com, kDaphnee\_Bosch@amat.com, yenlin\_LEOW@amat.com, mAlain\_Duboust@amat.com, alexis.drouin@soitec.com, ojean-marc.bethoux@soitec.com, promain.boulet@soitec.com, audrey.chapelle@soitec.com, renrica.cela@soitec.com, sguillaume.lavaitte@soitec.com, tadeline.bouville-lallart@soitec.com, alexis.drouin@soitec.servant@cea.fr, wshivan\_Bhargava@amat.com, alexis.drouin@soitec.com, zchristophe.maleville@soitec.com, xShawn\_Thomas@amat.com, yionut.radu@soitec.com, zchristophe.maleville@soitec.com, abwalter.schwarzenbach@soitec.com

**Keywords:** Smart Cut<sup>™</sup>, SmartSiC<sup>™</sup>, Low resistivity, SiC layer transfer

**Abstract.** Silicon Carbide (SiC) Power Devices have emerged as a breakthrough technology for a wide range of applications in the frame of high power electronics. Despite the continuously improving quality and supply of 4H-SiC substrates, the availability of such wafers is still insufficient. An advantageous opportunity is offered by the Smart Cut<sup>TM</sup> technology with the integration of a very high quality SiC layer transferred to a low resistivity handle wafer. This bi-layer material enables a significant yield optimization and improvement of the device's electrical performance. Moreover, an additional key feature of the Smart Cut<sup>TM</sup> technology is the possibility to re-use multiple times the donor wafer, leading to reduced manufacturing costs and enabling the high volume production of SiC wafers. In this paper, we report the latest advances in the development of such so called SmartSiC<sup>TM</sup> substrates.

## Introduction

Among its unique properties, including high electric field breakdown strength and high thermal conductivity, Silicon carbide (SiC) is a material of choice for power devices allowing a higher frequency operation but also to reduce the size and the power losses of the devices. Thus, SiC is a key material for devices developed for high growth applications such as automotive or renewable energy [1]. Semiconductor companies are currently facing an urgent need for capacity expansion to meet the growing market demands. Despite the recent progress in 4H-SiC material with a continuous improvement of the quality and the supply, the availability of near defect-free wafers, enabling very high yields, is still insufficient. In this context, we have developed an innovative bi-layer SiC substrate, and installed a dedicated Pilot Line to support the technology development and initial sampling. Thanks to the Smart Cut<sup>TM</sup> technology [2], a very high quality 4H-SiC layer is transferred to a specific handle wafer with low resistivity leading to improvement of the device yield and electrical performance.

# Smart Cut<sup>TM</sup> Technology and Low Resistivity Material

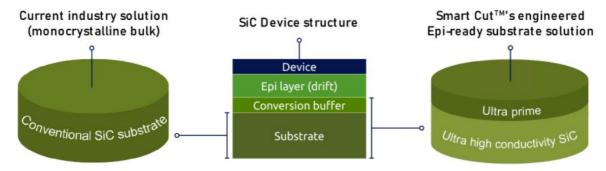

For over 30 years, the Smart Cut<sup>TM</sup> technology has been used to produce several millions of wafers, through high volume manufacturing processes, mostly silicon wafers. The process has been successfully adapted for SiC material by transferring a high quality crystalline SiC layer to a low resistive wafer support (Fig. 1) [2-5]. Thereby the engineered SmartSiC<sup>TM</sup> substrate is epi-ready and the epitaxy growth process to be performed is simpler than for conventional SiC wafers, as the conversion buffer layer is already done.

Figure 1: SmartSiC<sup>TM</sup> versus bulk 4H-SiC substrates for power devices [2-3]

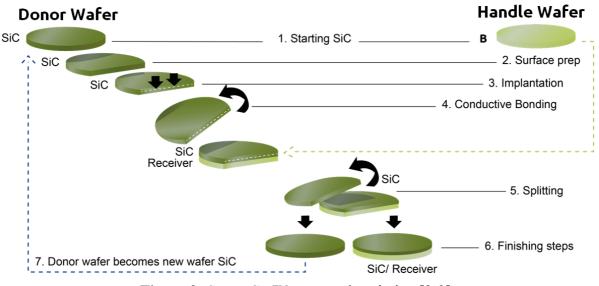

The Smart  $Cut^{TM}$  technology, described in the following figure (Fig. 2), is based on several key steps like the hydrogen implantation of the donor wafer, allowing to control the thickness of the transferred layer (from 0.1  $\mu$ m to 1  $\mu$ m). A key element of the transfer process is the realization of a highly conductive bonding interface to ensure excellent vertical conductivity through the newly formed substrate. The finishing steps ensure excellent roughness and thermal stability, to prepare an EPI-ready surface. The donor wafer is re-used multiple times, opening the path for high volume wafer production.

**Figure 2:** Smart Cut<sup>TM</sup> process description [2-3]

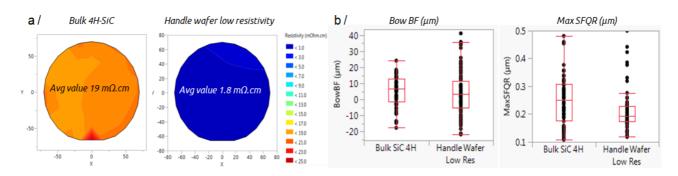

The geometrical and electrical properties of the finished product are closely driven by those of the handle wafer. Fig. 3 illustrates the low resistivity values obtained within the engineered substrate in comparison to commercially available bulk 4H-SiC (Fig. 3a) – the electrical resistivity of the innovated substrate is at least 4 times lower than standard bulk 4H-SiC. Moreover, in addition to the improved electrical conductivity, the shape of product, measured through wafer diameters, the thickness, the edge shape, the bow, the warp, the Site Front sQuare focal plane Range (SFQR) and the Total Thickness Variation (TTV) is equivalent to commercial bulk 4H-SiC wafers. (Fig. 3b)

**Figure 3:** 3.a/ Resistivity mapping by Eddy Current measurement on 4H-SiC compared to handle wafer low resistivity. 3.b/ BOW & SFQR values distribution on both the reference 4H-SiC bulk wafer and the low resistivity handle wafer

#### **SmartSiC<sup>TM</sup> Performance and Validation**

An excellent 4H-SiC layer integrity and quality is demonstrated. The picture on Fig 4 shows a 150 mm SmartSiC<sup>TM</sup> substrate, highlighting the defect-free surface quality, including the small edge crown width (< 5 mm).

Figure 4: Picture of a Smart SiC<sup>TM</sup> substrate

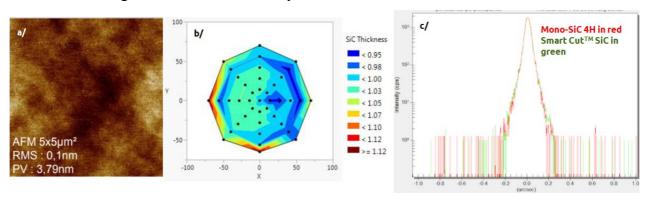

Intensive physical, chemical and electrical characterizations have been conducted on the SmartSiC<sup>TM</sup> to assess the performance of the engineered substrate. Thus, the roughness measurements carried out by AFM in  $5x5~\mu m^2$  scan confirm the achievement of a smooth surface with Rq < 1Å (Fig. 5a), similar to a standard 4H-SiC substrate. The thickness uniformity of the transferred layer was also measured and a standard deviation lower than 4% was determined (Fig. 5b). The grazing incidence diffraction by X-Ray (GID) on {11-20} plane shows that the 4H-SiC layer on the final product is fully stress relaxed (Fig. 5c). Thus, the top 4H-SiC layer on the Smart Cut<sup>TM</sup> substrate is guaranteed to be EPI-ready.

**Figure 5:** 5.a/ AFM on SmartSiC<sup>TM</sup> & 5.b/ SmartSiC<sup>TM</sup> Layer uniformity & 5.c/ GID on {11-20} plane 4H-SiC comparison with SmartSiC<sup>TM</sup>

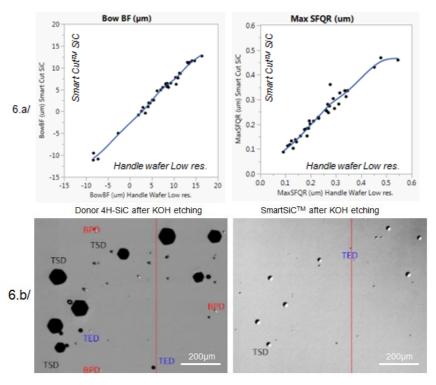

From the well-known manufacturing experience, the Smart Cut<sup>TM</sup> process does not impact the geometry of the incoming material. Thus, SmartSiC<sup>TM</sup> exhibits the same performance on wafer geometry parameters like flatness, bow, warp and TTV compared to the handle wafer low resistivity (Fig. 6a). The crystal quality of the final substrate is directly linked to that of the donor wafer. We have developed a specific characterization by KOH etching (specially adapted to analyze a thin film), and this one confirms the absence of crystal defect creation during the Smart Cut<sup>TM</sup> process. SICA inspections on SmartSiC<sup>TM</sup> and 4H-SiC donors after KOH etching show exactly the same defect density trend (Fig. 6b).

**Figure 6:** 6.a/ SmartSiC<sup>TM</sup> geometry & 6.b/ SICA on 4H-SiC donor & SmartSiC<sup>TM</sup> after KOH etching (same scan position)

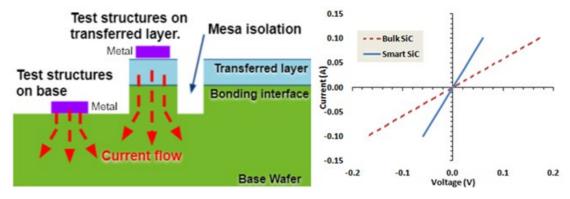

Last but not least, to monitor the electrical performance of the composite wafer, a test structure has been developed to determine the resistivity of the bonding interface (Ohmic behavior with an interface resistivity < 0.1 m $\Omega$ .cm<sup>2</sup>). I(V) curves show that SmartSiC<sup>TM</sup> has a lower resistivity than conventional 4H-SiC (Fig. 7). Thus, this SiC substrate improves the total vertical resistance by a factor of at least 2 (wafer thickness at 100 µm) to 3 (wafer thickness at 350 µm) versus 4H-SiC.

Figure 7: Electrical test structure and I(V) result

## **Conclusions**

The Smart Cut<sup>TM</sup> technology provides for the power devices manufacturers an innovative SmartSiC<sup>TM</sup> substrate with high crystal quality and low electrical resistivity. The recycling of the initial (donor) SiC wafer enables cost-effective manufacturing of very large volumes with reduced investments. A pilot line is currently ready for 150 mm substrates and 200 mm substrates preparation will be engaged beginning of 2022.

## References

- [1] T. Kimoto *et al.*, "Material science and device physics in SiC technology for high-voltage power devices." Japanese Journal of Applied Physics 54.4 (2015): 040103.

- [2] W. Schwarzenbach *et al.*, "Smart Cut<sup>TM</sup> SiC Substrates for Manufacturing of High Quality Power Devices", Electron Devices Technology and Manufacturing Conference (2021)

- [3] L. Di Cioccio *et al.*, "Silicon carbide on insulator formation using the Smart Cut process" Electronics Letters 32.12 (1996): 1144-1145.

- [4] F. Letertre *et al.* "SiC Power Devices on QUASIC and SiCOI Smart-Cut® Substrates: First Demonstrations." Materials Science Forum. Vol. 433. Trans Tech Publications Ltd, 2003.

- [5] https://www.soitec.com/en/products/auto-smartsic