# Study of Laser Backside Ohmic Contact Formation of SiC-Ni Interface to Evaluate the Process Influence on the Electrical Characteristics

Submitted: 2021-10-15

Revised: 2022-03-12

Online: 2022-05-31

Accepted: 2022-03-13

Dirk Lewke<sup>1,a\*</sup>, Frank Supplieth<sup>2,b</sup>, Maik von Ringleben<sup>1,a</sup> and John Ransom<sup>2,d</sup>

<sup>1</sup>3D-Micromac AG, Technologie-Campus 8, 09126 Chemnitz, Germany <sup>2</sup>X-FAB, 2301 N University Ave, Lubbock, TX 79415, USA

<sup>a</sup>Lewke@3d-micromac.com, <sup>b</sup>Frank.Supplieth@xfab.com, <sup>c</sup>Ringleben@3d-micromac.com, <sup>d</sup>John.Ransom@xfab.com

**Keywords:** laser, annealing, ohmic contact formation, metallization, Silicon Carbide, 4H-SiC.

**Abstract.** Within this paper, we will present the results of a study on the ohmic contact formation process with nanosecond (ns) pulsed UV lasers. For the study we compared two laser processes: The base line process with a 100-300 ns pulsed laser with Gaussian beam profile and the 3D-Micromac AG process with a 50-100 ns pulsed laser with top hat beam profile. The forward voltage characteristics at wafer level was analyzed and proves a clear benefit of the top hat laser process. Besides, the forward voltage characteristics of a second run was performed to analyze the influence of increasing energy density to the electrical characteristic of heat sensitive front side structures. Also with high energy density no negative influence could be detected.

#### Introduction

4H-SiC power semiconductor devices like diode, MOSFET or JFET are vertical devices with structures at the chip front side and a metallization stack at the chip back side. The current flow at this kind of devices is vertical between the front side and the back side. By thinning of the chips, the resistance can be reduced [1] and this is done more and more. While producing those power devices, the front side will be processed first. After this, the SiC wafer is thinned from the back side by a grinding process. After the grinding step, the metallization stack is produced on the back side of the wafer.

Typically, nickel (Ni) is used as a first metallization layer. However, combinations of titanium (Ti) and silicon (Si) can also be realized[2]. Directly after metal deposition, the electrical characteristics of the metal SiC interface correlate with a Schottky characteristic curve. The Ohmic Contact Formation (OCF) process is performed after the first metallization layer is deposited. This process applies heat to the back side of the wafer to convert the Schottky contact into an ohmic contact. In additional process steps, more metal layers are applied to finish the back side processing. For standard thick SiC wafers without back side grinding (e.g. 350 µm thickness), flash lamps were used to perform the OCF process. Due to the wafer thickness reduction, this annealing cannot be performed anymore due to the high heat load at the front side of the wafers. This is why, with thinner wafers down to 80 µm thickness and below, nano-second (ns) laser systems are used to perform the OCF process. Within this paper two possible ns lasers systems were compared regarding resulting electrical characteristics. With one system it was demonstrated that the heat of the back side do not harm the electrical characteristics of the front side.

## **Ohmic Contact Formation**

After applying the first metallization layer at the back side of power semiconductor wafers, an ohmic contact between semiconductor and metallization has to be formed. For SiC power semiconductors, typically Ni or Ti layers with thickness of 40 to 100 nm are used. To form an ohmic contact with oven annealing, a heat treatment of approx.  $900 - 1000^{\circ}$ C at the wafer back side is necessary [3,4]. While applying the heat, the back side metal together with the Silicon from the SiC forms a metal silicide e.g. a nickel silicide (Ni<sub>x</sub>Si<sub>y</sub>). The residual carbon forms carbon clusters at the

interface of SiC and Ni<sub>x</sub>Si<sub>y</sub>. [4, 5]. For thin wafers, short pulsed lasers have major benefits due to not influencing the front side of the SiC wafers while the heat treatment is performed at the back side.

## **Experimental Setup**

Two laser systems were used. Both laser systems were equipped with a solid state nanosecond laser with 355 nm wavelength. The first system is the base line process and runs under production. At the laser interaction zone the beam profile of this laser has a Gaussian TEM00 characteristic. The pulse length of the single laser pulses is approx. 100-300 ns. The process runs under oxygen reduced atmosphere. Therefore, a nozzle applies nitrogen to the wafer surface irradiated by laser.

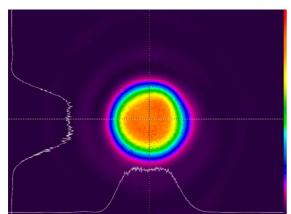

Fig. 1: Flat Top profile of laser spot

The second system was the 3D-Micromac AG's microPRO<sup>TM</sup> XS OCF. This system is equipped with a 25 W nanosecond laser with a pulse length between 50 and 100 ns. The laser beam at the interaction zone has a flat top profile of approx. 80 μm in diameter (Fig. 1).

The benefit of a flat top profile compared to a Gaussian beam is the homogenous energy distribution over the wafer. With such a system, larger laser spots are possible which leads to an increase of throughput. A galvo scanner system is used to guide the laser over the surface of the sample. To reduce the oxygen level, a process chamber is purged with N<sub>2</sub>. The oxygen level during processing was <300 ppm.

The used wafers were fully processed power electronic 4H-SiC wafers. The diameter of the wafers is 150 mm and their thickness is between 80  $\mu$ m and 175  $\mu$ m. For wafer thinning, two different grinding processes (Grinding A and B) were used to check if an influence on forward resistance can be seen. At the back side of the wafers, a 75 nm thick nickel layer was sputtered. After the laser-based ohmic contact formation, the wafers were cleaned, and the back side metallization stack was finished with 4  $\mu$ m to 5  $\mu$ m thick of Aluminum layer. Subsequently, to finishing the processing, the forward resistance was measured for each device at wafer level.

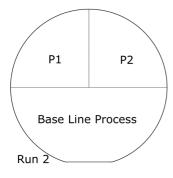

Two wafer runs were performed. The first run was with six wafers with vertically resistor structures. Two thicknesses (80 and  $175 \mu m$ ) as well as the two different grinding processes are shown in this paper. For this evaluation, low forward resistance was the main quality criteria. For the base line process, only one parameter set was used. For the 3D-Micromac process, a parameter sweep was performed (Fig. 2). Hereby, the pulse energy density and the pulse overlap was varied (Table 1).

The second run was performed on 110 µm and 150 µm thick wafers with SiC JBS diodes, to analyze the influence of the back side heat load, generated by the laser OCF processing, on the front side structures. These JBS structures are chosen because they are one of the products running in xfab production, which are most sensitive to heat at front side structures. If head load at the front side is too high, this will be seen in the electrical characteristic. This test is to prove the usability of the process for production. One parameter was used for the base line process and a parameter sweep for the 3D-Micromac process was performed by variation of energy density and pulse overlap (Fig. 4 and Table 2).

## Results

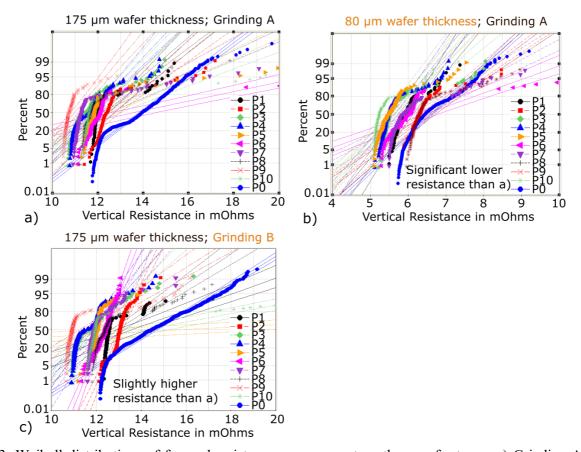

In Fig 3. exemplary electrical results of run 1 are shown. As a result, it was demonstrated that all tested parameters with a top hat profile result in comparable or lower forward resistance as with a Gaussian energy profile – so all parameters are comparable or better than for the base line process. Furthermore, it could be shown that by tuning the pulse to pulse overlap and pulse energy, density an optimum forward resistance can be achieved. Higher energy density or higher pulse overlap results in lower forward resistance. Nevertheless, with reduction of the overlap, an increase of throughput

can be achieved. By reading the results it has to be taken into account, that there is also an influence of wafer raw material to the electrical results. This is due to inhomogeneous dopant concentration in wafer material. The effect can be seen in Fig 5.

Since vertical devices are used, the forward resistance will be reduced with reduction of the wafer thickness. The wafer thickness has a much higher influence on the forward resistance than the laser parameters (Compare Fig 3 a) and b)). Nevertheless, with reduction of the wafer thickness, the influence of the laser parameters will be more and more important.

The grinding process also has an influence on the forward resistance values. The influence of the grinding process is comparable with the influence of the laser parameters (Compare Fig 3 a) and c)).

P1

P2 P3 P4 P5

P6 P7 P8 P9 P10

Base Line Process

Run 1

Fig. 2: Overview of parameter field for run 1

| Table 1. Run 1: Process p | parameter fields | per each wafer |

|---------------------------|------------------|----------------|

|---------------------------|------------------|----------------|

| Parameter | Pulse energy | Pulse overlap | Beam     |

|-----------|--------------|---------------|----------|

| #         | density [%]  |               | profile  |

| P0        | Base line    | Base line     | Gaussian |

| P1        | 78           | Max           | Top hat  |

| P2        | 78           | Middle        | Top hat  |

| Р3        | 85           | Max           | Top hat  |

| P4        | 85           | Middle        | Top hat  |

| P5        | 93           | Max           | Top hat  |

| P6        | 93           | Middle        | Top hat  |

| P7        | 93           | Min           | Top hat  |

| P8        | 93           | Min           | Top hat  |

| P9        | 100          | Max           | Top hat  |

| P10       | 100          | Middle        | Top hat  |

Fig. 3: Weibull distributions of forward resistance measurement on three wafer types. a) Grinding A with 175  $\mu$ m thickness, b) Grinding A with 80  $\mu$ m thickness, c) Grinding B with 175  $\mu$ m thickness. Aim is to reduce vertical resistance. Top Hat process shows lower vertical resistance than base line process

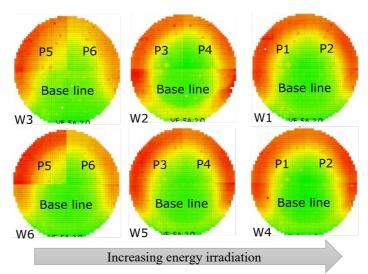

In Fig 5. the results of wafer run 2 are shown. Only at the parameter with the lowest energy irradiation – P5 at wafer 3 and 6 – a change from the base line to the other parameter fields is visible. At these fields, the laser energy irradiation was not high enough to form a proper ohmic contact. Hence, the resistance is higher. By analyzing all other parameter fields, it can be seen, that with increasing energy irradiation, the resistance does not significantly change from base line process to the parameter field. This proves that higher energy irradiation do not affect the electrical characteristic of the wafer's front side for 150 and 110  $\mu$ m thick wafers.

Fig. 4: Overview of parameter field for run 2 (wafer 1 and 4)

Table 2. Run 2: Process parameter fields for each wafer

| Parameter # | Wafer #     | Pulse energy density [%] | Pulse<br>overlap | Beam<br>profile |

|-------------|-------------|--------------------------|------------------|-----------------|

| P0          | 1,2,3,4,5,6 | Base line                | Base line        | Gaussian        |

| P1          | 1, 4        | 100                      | Min              | Top hat         |

| P2          | 1, 4        | 100                      | Max              | Top hat         |

| Р3          | 2, 5        | 90                       | Min              | Top hat         |

| P4          | 2, 5        | 90                       | Max              | Top hat         |

| P5          | 3, 6        | 78                       | Min              | Top hat         |

| P6          | 3, 6        | 78                       | Max              | Top hat         |

Fig. 5: Forward Voltage: Colors green to red correspond to minimum to maximum per wafer. Wafer 1-3 are 150 μm thick. Wafer 4-6 are 110 μm thick. For parameter see Table 2. From left to right the energy irradiation is increased from min. to max.. It can be seen that at minimum energy irradiation results in forward voltage increase due to not fully performed ohmic contact formation. An increase to maximum energy irradiation do not change the forward voltage. Higher forward voltage at wafer edge region is a result of inhomogeneous dopant distribution in wafer material.

Within this paper, the influence of the process parameters on laser-based ohmic contact formation was evaluated and compared with the influence of the wafer parameters such as wafer thickness and grinding process. With this knowledge, the optimal process regime can be adjusted. In an additional wafer run it could be shown that laser thermal annealing for ohmic contact formation does not affect the surface structures even with higher laser energy and  $110~\mu m$  thin wafers.

### References

- [1] Yasuhisa Sano et.al., "Back-Side Thinning of Silicon Carbide Wafer by Plasma Etching Using Atmospheric-Pressure Plasma", Key Engineering Materials Volume 516, 2012, p. 108-112

- [2] Milantha De Silva et.al., "Low resistance Ti-Si-C ohmic contacts for 4H-SiC power devices sing laser annealing", Materials Science Forum Volume 897, 2017, pp 399-402

- [3] Sang Youn Han et.al., "Ohmic contact formation mechanism of Ni on *n*-type 4H–SiC", Appl. Phys. Lett. 79, 1816, 2001

- [4] Roland Rupp et.al., "Laser backside contact annealing of SiC power devices: A prerequisite for SiC thin wafer technology", 25th International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2013, pp. 51-54

- [5] Benedikt Adelmann et.al., "Temperature and Stress Simulation of 4H-SiC during Laser-Induced Silicidation for Ohmic Contact Generation", Metals, Vol. 7, no. 12, 2017, p. 545