Submitted: 2021-10-23 Revised: 2022-03-15 Accepted: 2022-03-15 © 2022 The Author(s). Published by Trans Tech Publications Ltd, Switzerland. Online: 2022-05-31

# Ohmic Contact Formation on 4H-SiC with a Low Thermal Budget by **Means of Shallow Phosphorous Ion Implantation**

Vinoth Sundaramoorthy a\*, Stephan Wirthsb and Lars Knollc

Hitachi Energy, Fabrikstrasse 3, 5600 Lenzburg, Switzerland

<sup>a</sup>vinoth.sundaramoorthy@hitachienergy.com, <sup>b</sup>stephan.wirths@hitachienergy.com, clars.knoll@hitachienergy.com

**Keywords:** Ohmic contacts, Schottky barrier, shallow implantation, barrier modulation, annealing.

Abstract. In this manuscript Ohmic contact formation at low annealing temperatures is demonstrated using shallow implantation technique. Remarkably, Ni Ohmic contacts with a specific contact resistivity of 1.9x10<sup>-5</sup> Ωcm<sup>2</sup> have been achieved at as-deposited condition. Smooth interfaces along with reduced Schottky barrier at the metal/SiC interface contributed to improved Ohmic performance at as-deposited and 450°C anneal conditions.

### Introduction

Conventional Ohmic contact formation on n-type 4H SiC requires high temperature annealing. Typically, nickel-based metal layers are deposited on SiC layers and annealed at temperatures above 950°C in inert atmosphere [1-5]. Ni silicide alloy is already formed in SiC at 600°C annealing temperature, but the metal semiconductor contact becomes Ohmic only at high temperatures >950°C. This has been attributed to many factors that include an increase of net donor concentration at the silicide/SiC interface; recrystallization of Ni<sub>2</sub>Si phase on SiC surface during high annealing temperature; formation of nanocrystalline graphitic layer on SiC surface [1-5]. All these factors require higher annealing temperature for the respective mechanism to occur at the metal/SiC interface during silicidation.

This high temperature annealing may not be compatible with the fabrication of SiC devices based on dielectric layers that cannot withstand temperatures above 500°C. Annealing at high temperature to form Ohmic contact causes the metal layer to interact with SiC layer. This forms metal silicide or carbides and have a rough surface. The rough morphology of contacts annealed at high temperature could be detrimental to the device performance in the long term. Hence, it is essential to develop a Ohmic contact formation process at low annealing temperatures for device process integration. Ohmic contacts with a low thermal budget have been investigated earlier using high dose implantations [6]. It was followed by a high temperature activation that may not be compatible with device processing.

In order to achieve Ohmic contacts at low anneal temperature, it is key to increase the doping concentration and, thus, reduce the Schottky barrier height at the metal/semiconductor interface. We have developed a process that is based on implanting a high dose of n-type dopants only on the SiC surface to increase the background doping without activation.

## **Experimental Details**

A thin n-SiC epilayer with a doping concentration of  $\sim 3 \times 10^{18}$  cm<sup>-3</sup> on a 4H-SiC substrate with a doping concentration of  $\sim 10^{18}$  cm<sup>-3</sup> was used as the starting material and implanted with phosphorous. Here, we have used a phosphorous dose of 1x10<sup>16</sup> cm<sup>-2</sup> at an energy of 15 keV. Ni contacts have been deposited on these samples and annealed at different temperature starting from 450°C to 1000°C. All the samples have been treated in rapid thermal anneal chamber at 1000°C for 5 minutes in vacuum before the metal deposition.

#### **Results**

#### **Electrical characterization**

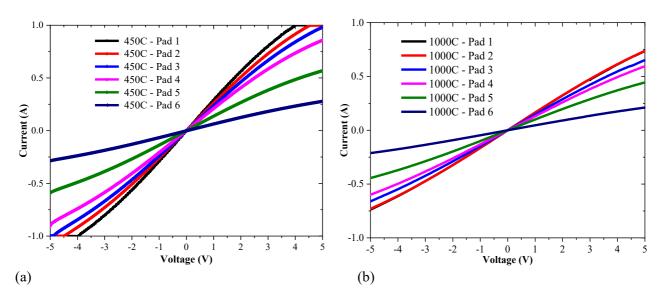

The results of the I-V measurements on the contacts annealed from 450 °C to 1000 °C is shown in fig 1. The specific contact resistivity was measured using Transfer Length Measurement (TLM) technique at different anneal conditions and shown in table 1. We observed that the contacts were Ohmic at all anneal conditions, although the best performance was achieved at as-deposited and 450 °C anneal condition. The contacts start to become more resistive beyond 550 °C annealing and recover the performance after annealing at 1000 °C.

Fig. 1. I-V curves measured on TLM pads at (a) 450 °C, (b) 1000 °C. *Legend:* Pad 1, 2, 3, 4, 5, 6 refers to 5  $\mu$ m, 10  $\mu$ m, 15  $\mu$ m, 25  $\mu$ m, 50  $\mu$ m, 75  $\mu$ m spacing respectively between the inner and outer circular contacts in TLM pad.

Table I. Comparison of specific contact resistivity for Ni Ohmic contact at different annealed condition.

| Anneal Temperature [°C] | Specific contact resistivity [ $\Omega$ cm <sup>2</sup> ] |

|-------------------------|-----------------------------------------------------------|

| Non anneal              | 1.9x10 <sup>-5</sup>                                      |

| 450                     | $2.3 \times 10^{-5}$                                      |

| 550                     | $1.9 \times 10^{-4}$                                      |

| 1000                    | 6x10 <sup>-5</sup>                                        |

#### Structural characterization

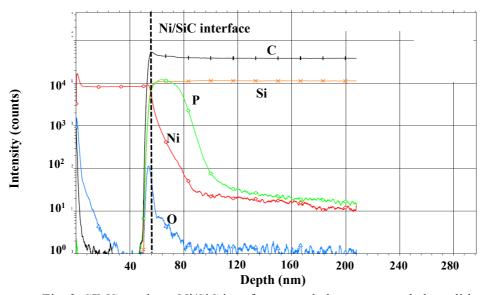

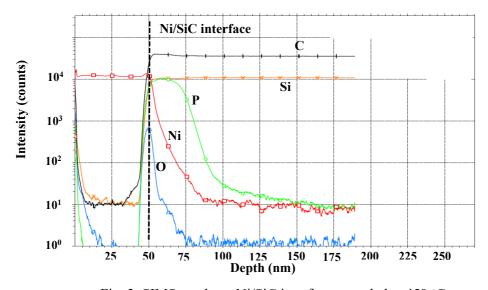

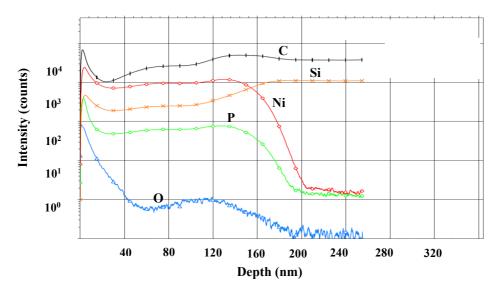

To support the electrical measurements, the secondary ion mass spectrometry (SIMS) was performed for nickel contacts annealed at different conditions. It can be seen from the SIMS analysis at as-deposited condition and 450°C anneal condition as shown in figs 2 and 3, that the metal SiC/interface is very similar. The nickel silicide is not yet formed at 450 °C and there is a smooth abrupt interface between the nickel and SiC layer. It can also be seen that the peak of the implanted phosphorous appears at the SiC/Ni interface, thereby reducing the Schottky barrier height to enable Ohmic contact formation already at as-deposited condition. It was observed that the nickel silicide is completely formed at 550°C due to strong reaction between nickel and SiC surface (not shown). Phosphorous dopants move away from the metal/SiC interface and embeds with nickel silicide. Annealing at 1000°C causes more stronger reaction, causing uniform distribution of phosphorous throughout the silicide (fig 4).

Fig. 2. SIMS results at Ni/SiC interface annealed at non-annealed condition.

Fig. 3. SIMS results at Ni/SiC interface annealed at 450 °C.

Fig. 4. SIMS results at Ni/SiC interface annealed at 1000 °C.

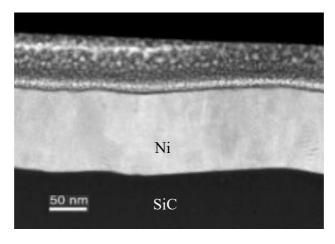

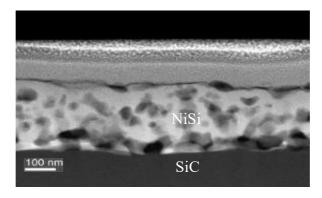

The TEM analysis of contacts annealed at 450 °C and 1000 °C is shown in figs 5 and 6. From fig 5, it could be seen that Ni layer did not react with the underlying highly doped SiC material at 450 °C. It has smooth interface with the SiC layer. Smooth metal/SiC interface coupled with reduced Schottky barrier at the interface contributes to superior Ohmic performance at non-annealed & 450 °C anneal condition (fig 5). Annealing at 1000 °C causes strong reaction between nickel and SiC layer, thereby forming nickel silicide contacts with rough morphology (fig 6). A relatively high proportion of nickel silicide is formed at an interface layer, disturbing the SiC material below.

Fig. 5. TEM results at Ni/SiC interface annealed at 450 °C.

Fig. 6. TEM results at Ni/SiC interface annealed at 1000 °C.

## **Summary**

A method to form Ohmic contacts at low annealing temperatures has been developed by implanting a phosphorous dose of 1E16cm<sup>-2</sup> at an energy of 15 keV in SiC epilayers. This caused an increase in carrier concentration at the metal/SiC interface and modulated the Schottky barrier height at the interface. Due to this, Ohmic contacts with a specific contact resistivity of 1.9x10<sup>-5</sup> Ωcm<sup>2</sup> was achieved already at as-deposited condition. Annealing at 450°C produced similar results, as the nickel had not yet reacted with SiC layer and interface was similar to as-deposited condition. However, annealing at 550°C degraded the performance, as nickel silicide have been formed at this temperature giving rise to a traditional Ohmic behavior. The electrical behavior was analyzed further by SIMS and TEM. From these analyses, it could be seen that there was a decrease in Schottky barrier and nickel had a smooth morphology at the metal/SiC interface at as-deposited and 450°C anneal condition. Smooth interface in combination with modified carrier concentration contributed to improved Ohmic performance at these conditions.

## References

- [1] S. Y. Han, K. H. Kim, J. K. Kim, H. W. Jang, K. H. Lee, N. –K. Kim, E. D. Kim and J. –L. Lee, Appl. Phys. Lett. **79**, 1816 (2001).

- [2] I. P. Nikitina, K. V. Vassilevski, N. G. Wright, A. B. Horsfall, A. G. O'Neill and C. M. Johnson, J. Appl. Phys. **97**, 083709 (2005).

- [3] A.V. Kuchuk, V. P. Kladko, K. Golaszewska, M. Guziewicz, M. Wzorek, E. Kaminska and A. Piotrowska, Mat. Sci. Forum. **717-720**, 833 (2012).

- [4] F. Roccaforte, F. La Via, V.Raineri, Int. J. High Speed Electronics and systems. 15, 781 (2005).

- [5] S. Tanimoto, H. Okushi, K. Arai, Silicon Carbide Recent major advances (Springer, 2004), p. 651.

- [6] V. Sundaramoorthy, R. Minamisawa, L. Kranz, L. Knoll, G. Alfieri, Materials Science Forum **924**: 413, June 2018.