doi:10.4028/p-43627c

© 2022 The Author(s). Published by Trans Tech Publications Ltd, Switzerland.

Submitted: 2021-10-15 Revised: 2022-02-08 Accepted: 2022-03-10 Online: 2022-05-31

# Decoration and Density Increase of Dislocations in PVT-Grown SiC Boules with Post-Growth Thermal Processing

Gil Chung<sup>1,a\*</sup>, Ian Manning<sup>1,b</sup>, Andrey Soukhojak<sup>1,c</sup>, Matt Gave<sup>1,d</sup> and Charles Lee<sup>1,e</sup>

<sup>1</sup>SK siltron css, 5300 Eleven Mile Rd, Auburn, MI, USA

<sup>a</sup>gil.chung@sksiltron.com, <sup>b</sup>ian.manning@sksiltron.com, <sup>c</sup>andrey.soukhojak@sksiltron.com, <sup>d</sup>matthew.gave@sksiltron.com, <sup>e</sup>charles.lee@sksiltron.com

**Keywords:** 4H-SiC, bulk crystal growth, post-growth thermal processing, dislocation density, X-ray topography, dislocation decoration, surface inspection tools

**Abstract.** Post-growth thermal processing at higher temperature generates more BPDs (basal plane dislocations). It is observed that dislocation visibility in surface inspection tool images varies significantly even at comparable dislocation densities. Combination of dislocation decoration and light absorbance from SiC matrix by point defects or dopants has been proposed as a working hypothesis to explain dislocation visibility variations.

### Introduction

SiC is a leading material for power electronics to control, convert, and distribute electric power efficiently. The widespread adoption of SiC semiconductor technologies continues to grow, and markets for several applications such as e-mobility, renewable energies and high-end power supplies are rapidly expanding [1, 2]. SiC wafers grown by physical vapor transport (PVT) have improved in crystal quality, with significant reductions in crystal dislocations. Concurrently, in-line surface inspection tools with photoluminescence (PL) capabilities have been introduced in the SiC wafer industry to detect and count dislocations accurately [3, 4]. In this paper, dislocation density changes by post-growth thermal processing will be discussed. Also, dislocation visibility changes in surface inspection tool images will be reviewed and a working hypothesis will be proposed to explain the dislocation visibility changes.

# **Experimental**

4H n-type crystals were grown by the PVT process and post-growth thermal processing at different temperatures were performed. Charge concentrations of the tested wafers range from 2 to 4 x10<sup>18</sup>/cc. Industry standard wafering, grinding, slicing and polishing techniques were also employed for wafer generation. Dislocations were measured by 1) counting etch pits formed at the intersection of dislocations with wafer surfaces following immersion in molten KOH, and 2) by XRT images from Rigaku XRT micron. KLA Candela 8520, Lasertec SICA 88 and Etamax MiPLATO tools were used to inspect wafer level defectivities. Table 1 shows specifications for different surface inspection tools.

Table 1. Specifications for three surface inspection tools.

| Company          | Lasertec                         | KLA                         | EtaMax                    |

|------------------|----------------------------------|-----------------------------|---------------------------|

| Model            | SICA-88                          | Candela CS8520              | MiPLATO-SiC               |

| Scan method      | X-Y with TDI camera              | R-Theta with PMT            | R-Theta with PMT          |

|                  |                                  |                             |                           |

| Detection method | PL 2 ch & Surface (confocal+DIC) | PL, reflection & scattering | PL 3 ch/Surface/Spectrum  |

|                  | Hg-Xe lamp                       | 355 nm normal laser         | Laser                     |

|                  | Surface : 546nm                  | 405 nm oblique laser        | Surface : 355nm laser DIC |

| Light source     | PL: 313nm/365nm                  |                             | PL: 355nm                 |

#### **Results and Disussion**

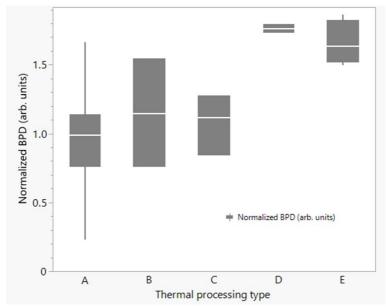

It is found that higher post-growth thermal processing temperatures generated more BPDs in wafers as shown in Fig. 1, but the correlation is not strong due to different sampling sizes at different processing temperatures. The driving force for BPD multiplication is the shear stresses in 1) the primary slip direction, that is, the  $a/3 < 11\overline{2}0 >$  and 2) in prismatic slip caused by thermal gradients during the boule growth [5, 6]. The Frank-Read source could be also responsible for multiplication. Higher post-growth thermal processing temperature causes more dislocation gliding and multiplication to result in higher BPD values.

Figure 1. Normalized mean BPD values measured for different post growth thermal processing. Thermal temperatures are increasing from A to E. Processing duration time and cooling rate were fixed. The quantile box plot shows median, 25th and 75th pecentiles. Wafers in this plots include multiple crystals grown from different seeds. BPD values are counted by XRT imaging and counting method.

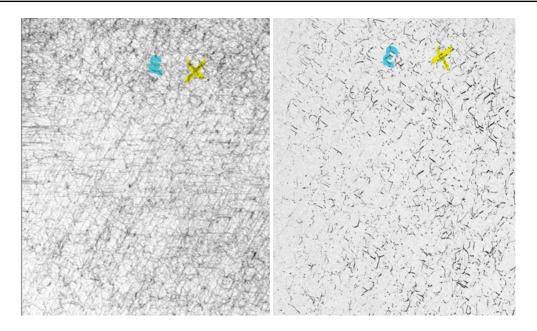

Features in the CS8520 ScN image (scattering channel images from the normal laser) match well with BPD lines in XRT images from (1128) as shown in Fig. 2. Wafers processed at different thermal processing temperatures, however, show different CS8520 feature densities as shown in Fig. 3 even at very comparable disloction densities. It was also learned later that those features in CS8520 images could be eliminated or made invisible by further thermal processing. Dislocation decoration by point defects or dopants has been proposed to explain dislocation visiblity in CS8520 images. Interaction between strain fields associated with dislocation lines and point defects/dopants could be a thermal process and depend on energy and entropy of the process. This decoration process seems sensitive to post-thermal processing temperatures and is more aggressive in middle temperature ranges like process C and D as compared to the lowest and highest temperatures (process A and E) in fig. 1.

Figure 2. XRT (left) and CS8520 ScN (right) images from the same area. Marks in blue and yellow are only for visual guidance.

Figure 3. CS8520 ScN images from wafers processed at different post-growth thermal processing temperatures. 36-08 (left) and 71-10 (right) were processed at process D and A, respectively. Bright lines in the images might be decorated dislocation lines. These two wafers show very comparable wafer resistivities and BPD densities.

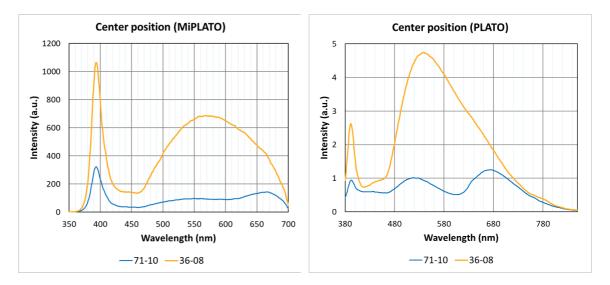

To understand roles of point defects/dopants for dislocation visibilty (dislocation decoration) changes, room temperature PL spectra was obtained as shown in Fig. 4. The highly decorated wafer shows a stonger band-edge emission (390 nm) than the un-decorated wafer. The peak around 500 nm could be the nitrogen donor-boron acceptor recombination-related emission [7]. The un-decorated wafer shows two peaks around 527 and 675 nm in the yellow region while the decorated wafer shows a single and dominant peak at 537 nm (PLATO data). The peak at 537 nm could be sum of the two separate peaks at 520 and 675 nm. Previously  $N_{\rm C}V_{\rm Si}$  centers were characterized by the near infrared PL peak around 1300 nm in SiC [8] but origins of peaks from 500 to 700 nm in SiC are not clear at the moment. Wafers at different dislocation visibilities show differnt PL spectra in yellow region. Further work is needed to understand this observation.

Figure 4. PL Spectra from two spectrometer tools. Laser Power/Diameter: 200mW/1200um (PLATO), 15mW/2.5um (MiPLATO), Spectrometer: Andor SR303i/idus Du-420A-BU2, 150G gratings/500um entrance slit, exposure time: 500msec(PLATO) and 50msec (MiPLATO), MiPLATO use a mirror for laser beam reflection and PL transmission. Data collection and analysis by courtesy of EtaMax. 36-08 and 71-10 were processed at process D and A, respectively.

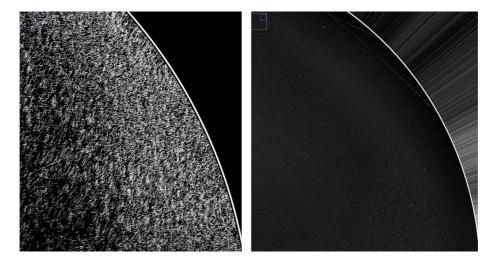

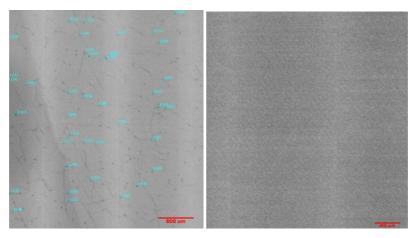

Some of processed wafers in this study show dark lines and dots in PL images from SICA 88 (NIRW filter) tool as shown in Fig. 5. Those lines and dots correspond to BPDs and TDs, respectively and non-radiative recombination centers along the dislocations formed by decoration of point defects/dopants were proposed [7]. It is also observed that dislocation visibility changes in SICA PL image are significant (a few orders of magnitude in area density) even at very comparable dislocation densities.

Figure 5. SICA 88 NIRW PL images. Decorated wafer (left) and un-decorated wafer (right). Dots in the left image are classfied as PL black dots from the tool vendor defect count recipe. These two wafers are very comparable in both dislocation density and crystal quality. Markers and IDs in the image (left) are generated by the defect recipe.

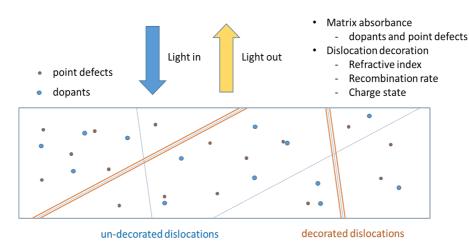

To explain dislocation visibility changes, a simple sketch as shown in Fig. 6 has been proposed as a working hypothsesis. Two major factors play a role to determine dislocation visilibity. First is matrix absorbance, which is light absorbance by SiC wafer itself. Nitrogen dopants or various point defects including complexes could be major variables to control light absorbance. Second could be dislocation decoration itself. Local refractive index, recombination rate or charge states along the dislocations lines could be changed significantly to alternate light scattering or PL generation.

Figure 6. Schematic sketch to visualize dislocation decoration and SiC matrix light absorbance for dislocation visibility changes.

# **Summary**

Post-growth thermal processing temperature affects BPD densities significantly. Higher temperature generates more BPDs through multiple slip mechanisms. Large variations in dislocation visibility from different surface inspection tool images are observed. Combination of matrix light absorbance and dislocation decoration has been proposed as a working hypothesis. Further work is needed to understand dislocation decoration by point defects or dopants. Better understanding of dislocation visibility changes in various surface inspection tool images is critical to assess wafer quality accurately.

## References

- [1] Semiconductor Today, Microelectronics, 11/16/2020

- [2] Ian Manning et al., Materials Science Forum Vol. 1004 (2020) 37-43

- [3] https://www.lasertec.co.jp/en/products/environment/sic/sica88.html

- [4] https://www.kla-tencor.com/products/instruments/defect-inspectors

- [5] B. Gao and K. Kakimoto, Cryst. Growth Des., 14 (2014) 1272-1278

- [6] J. Guo et al., J. of Electronic Materials, 46 (2017) 2040-2044

- [7] C. Kawahara et al., Jpn. J. Appl. Phys. 53 (2014) 020304

- [8] T. Narahara et al., Materials Science Forum, Vol. 1004 (2020) 349-354