© 2022 The Author(s). Published by Trans Tech Publications Ltd, Switzerland.

# Observation of Fast Near-Interface Traps in 4H-SiC MOS Capacitors Using Capacitance Voltage Analysis at Cryogenic Temperatures

Submitted: 2021-10-14

Accepted: 2022-03-07

Revised: 2022-02-09

Online: 2022-05-31

A.M. Vidarsson<sup>1,a\*</sup>, J.R. Nicholls<sup>2,3,b</sup>, D. Haasmann<sup>2,3,c</sup>, S. Dimitrijev<sup>2,3,d</sup> and E.Ö. Sveinbjörnsson<sup>1,4,e</sup>

<sup>1</sup>Science Institute, University of Iceland, 107 Reykjavik, Iceland

<sup>2</sup>Queensland Micro- and Nanotechnology Centre, Griffith University, QLD 4111 Brisbane, Australia <sup>3</sup>School of Engineering and Built Environment, Griffith University, QLD 4111 Brisbane, Australia <sup>4</sup>Department of Physics, Chemistry and Biology (IFM), Linköping University, SE-58183 Linköping,

E-mail: a\*amv10@hi.is, bjordan.nicholls@griffithuni.edu.au, cd.haasmann@griffith.edu.au, ds.dimitrijev@griffith.edu.au, eeinars@hi.is

**Keywords:** 4H-SiC, MOS capacitors, Near-interface traps, Capacitance analysis, Cryogenic temperatures

**Abstract.** The inversion channel electron mobility in 4H-SiC MOSFETs with NO annealed gate oxides is still well below its theoretical limit. The physical reason behind the reduced mobility is not yet fully established but has for example been attributed to a high density of very fast interface traps close to the conduction band edge. These traps are not detected by high-low CV analysis at room temperature but are observed by conductance spectroscopy at low temperatures. In this study we demonstrate how conventional high-low CV analysis of MOS capacitors at cryogenic temperatures can be applied to detect and quantify these very fast traps.

## Introduction

High power SiC MOSFETs are now commercially available. However, moderate inversion channel mobility has inhibited the development of low power devices (300 - 650 V) where the channel resistance is adversely affecting the power efficiency. The limited mobility is commonly attributed to large density of carbon-related interface defects [1-3].

Compared to the  $SiO_2/Si$  interface, the  $SiC/SiO_2$  interface contains a rather high density of interface traps as well as near-interface traps that are located 1-2 nm inside the gate oxide. Currently the most successful method to neutralize these traps is to use post annealing in  $N_2O$  or pure NO at high temperatures (1150 – 1350°C) [4-7]. This process is able to suppress the density of interface traps by an order of magnitude with energy levels located 0.1-0.5 eV below the SiC conduction band edge as revealed by CV analysis [6]. However, the inversion channel mobility is still only about 25-35 cm<sup>2</sup>/Vs which suggests that there are still some interface defects hampering the electron mobility that cannot be detected at room temperature [7].

Recent studies using conductance spectroscopy at cryogenic temperatures have observed very fast interface traps labelled NI, that are detected both in dry thermal oxides and nitrided oxides [8-10]. Subsequent studies have showed that the NI signal is due to direct tunnelling in and out of near-interface traps located very close to the SiC conduction band edge [8]. Here we demonstrate that the NI traps are observed at cryogenic temperatures using conventional high-low CV analysis.

## **Experimental**

In this study we use dry thermal oxide and dry oxide annealed in pure NO grown on 4° off-axis nepitaxial 4H-SiC with a net doping of ~10<sup>16</sup> cm<sup>-3</sup>. MOS capacitors were made with aluminium as the gate metal. The dry oxide (32 nm) was grown at 1240°C for 40 min. The NO annealed oxide (41 nm) was made by dry oxidation at 1250°C for 60 min followed by annealing in pure NO for 60 min at 1250°C.

Measurements were performed in a closed loop helium cryostat that is controlled using Lakeshore 331 temperature controller. Capacitance measurements were carried out using Agilent E4980A LRC meter and Keithley 6517B electrometer at fixed temperatures between 50 K and 300 K. High frequency measurements (1 kHz - 1 MHz) were conducted by sweeping the samples from -10 V to 10 V DC, using 10 mV AC test signal. Quasi static measurements were performed by sweeping the samples from -10 V to 10 V with 0.5 V/s ramp measuring the charge and the capacitance is calculated.

#### **Results and Discussion**

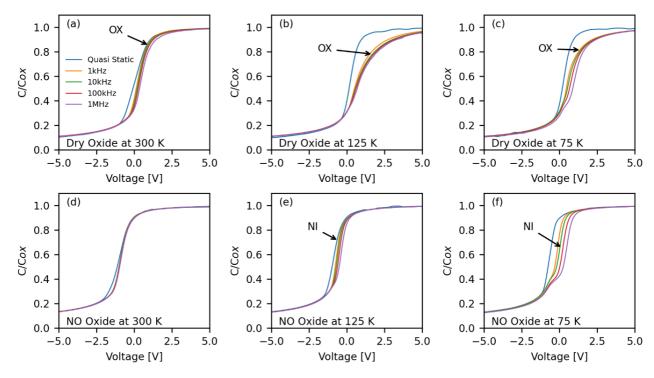

Figure 1 shows capacitance sweeps of both samples using quasi-static and high frequency signals at room temperature, 125 K and 75 K. Fig.1.a of the dry oxide sample at room temperature shows significant frequency dispersion, whereas the dispersion in the NO sample is much smaller (Fig.1.d). This well-known difference in the NO sample has been attributed to lower density of slow interface traps (labelled OX) with energy levels within the SiC bandgap [9]. At 125 K, a large portion of the slow traps in the dry oxide sample do not follow the high frequency signal, resulting in a stretch-out in accumulation due to electron trapping as seen in Fig.1.b [11]. As expected, this stretch-out is not observed in the NO sample due to the lack of OX traps, but frequency dispersion appears (Fig.1.e). At 75 K, a significant stretch-out in accumulation is observed in the dry oxide sample and the dispersion is enhanced (Fig.1.c) while a clear frequency dispersion is observed in the NO sample but no stretch-out in accumulation (Fig.1.f). Due to the stretch-out in the dry oxide sample the higher frequency curves asymptotically reach the accumulation capacitance at higher voltages (not shown). The dispersion starts in weak depletion at a similar surface potential as the NI signal is observed by

Fig. 1. Quasi-static and high frequency capacitance spectra of both samples at room temperature, 125 K and 75 K.

conductance spectroscopy [10]. At the onset of dispersion, the capacitance is at first influenced by traps that are responding near the test frequency and contribute to the capacitance. Then when the gate bias is increased further, the electron capture rate exceeds the test frequency and the traps remain filled and do not influence the CV curve. The dispersion behaviour versus voltage at 75 K is similar

in both samples. Overall, the data suggests that the dispersion at 75 K is due to the NI traps [10]. It is evident that some of the NI traps have electron emission rate that is temperature dependent. The kink that is visible in weak depletion in figures 1 (c), (e) and (f) is assigned to the onset of electron trapping in NI traps.

For comparison, CV and conductance analysis was performed on sodium-enhanced oxides (SEO) samples. MOSFETs using such oxides exhibit about three times higher inversion channel mobility than NO annealed devices [12]. Neither the OX nor NI traps were observed in both types of measurements within the detection limit (not shown). This further indicates that the CV dispersion at low temperatures is due to NI traps.

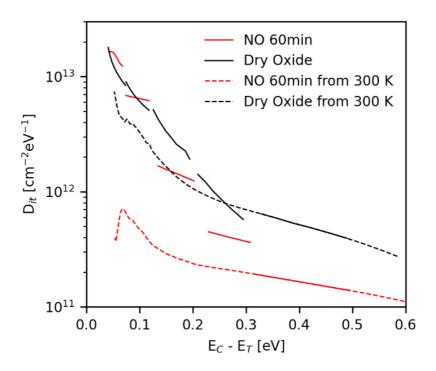

Fig. 2. Density of interface traps of both samples extracted from room temperature data (dashed lines) and at cryogenic temperatures (solid lines).

Figure 2 shows density of interface traps (D<sub>it</sub>) from high-low CV analysis of both samples. The dashed lines show the D<sub>it</sub> if only room temperature data is used and extended over a large energy range. The energy range extraction is based on thermal emission and using an electron capture cross section of 1.5x10<sup>-15</sup> cm<sup>2</sup>. At low temperatures when the near-interface NI trap is the main contribution to the D<sub>it</sub> such approach is not physically correct [10,12]. However, such simplification is justified when comparing relative differences in D<sub>it</sub> between different gate oxides containing the NI trap. Solid lines show the D<sub>it</sub> extracted using CV data at different temperatures, using a limited energy range for each temperature. The figure shows that using room temperature data results in an underestimation of D<sub>it</sub> close to the conduction band edge, especially for the NO sample. At cryogenic temperatures, the NO sample shows similar or higher D<sub>it</sub> than the dry oxide due the presence of a high density of NI traps that are too fast to be detected at room temperature. Measuring only at room temperature severely underestimates the density of traps closer to the conduction band edge. In addition, one should keep in mind that substantial surface potential fluctuations (the order of 100 mV) are present

at the SiC/SiO<sub>2</sub> interface [13,14] which makes definitive energy level localization of the interface traps questionable. Nevertheless we can compare the extracted D<sub>it</sub> from the cryogenic capacitance measurements for differently prepared gate oxides. Similar trend can be seen from the conductance spectroscopy analysis where the D<sub>it</sub> of the NI peak increases as we probe closer to the conduction band edge [9]. The CV analysis provides the total number of Dit (the sum of NI and OX traps) while the conductance spectroscopy can separate between the NI and OX traps. The high density of NI traps in NO annealed samples suggests that they are the main cause of limited inversion channel electron mobility in SiC MOSFETs.

## **Summary**

Very fast near-interface traps (NI) are observed in 4H-SiC MOS capacitors using high-low CV analysis at cryogenic temperatures in both dry oxides and NO annealed oxides. Comparison between differently prepared gate oxides suggests that electron trapping and scattering due to these traps is responsible for the rather low inversion channel electron mobility in NO annealed SiC MOSFETs.

## Acknowledgement

J. R. Nicholls, D. Haasmann, and S. Dimitrijev were supported in part by SICC material Co., Ltd., China, as the industry partner in the Australian Research Council Linkage Project under Grant ARC LP 50100525. A. M. Vidarsson and E. Ö. Sveinbjörnsson were supported by the Icelandic Centre for Research (Rannis) and the University of Iceland Research Fund. Parts of this work were performed at the Queensland node of the Australian National Fabrication Facility (ANFF), a company established under the National Collaboration Research Infrastructure Strategy to provide nanofabrication and microfabrication facilities to Australia's researchers.

## References

- [1] V. Afanasev, M. Bassler, G. Pensl and M. Schulz, Physica Status Solidi (a) 162, 321-337 (1997).

- [2] J.M. Knaup, P. Deák, Th. Frauenheim, A. Gali, Z. Hajnal and W.J. Choyke Phys. Rev. B 72, 115323 (2005)

- [3] S. Wang, M. Di Ventra, S.G. Kim and S.T. Pantelides Phys. Rev. Lett. 86, 5946 (2001)

- [4] M. Cabello, V. Soler, G. Rius, J. Montserrat, J. Rebollo, and P. Godignon, Materials Science in Semiconductor Processing 78, 22 31 (2018).

- [5] D. P. Ettisserry, N. Goldsman, A. Akturk, and A. J. Lelis, J. Appl. Phys 116, 174502 (2014).

- [6] G.Y. Chung, C.C. Tin, J.R. Williams, K. McDonald, M. Di Ventra, S.T. Pantelides, L.C. Feldman and R.A. Weller, Appl. Phys. Letters 76, 1712 (2000).

- [7] G.Y. Chung, C.C. Tin, J.R. Williams, K. McDonald, M. Di Ventra, S.T. Pantelides, L.C. Feldman and R.A. Weller, Appl. Phys. Letters 76, 1713 (2000).

- [8] H.Yoshioka, T. Nakamura and T. Kimoto, J. Appl. Phys. 112, 024520 (2012).

- [9] H.Yoshioka, T. Nakamura and T. Kimoto, J. Appl. Phys. 115, 014502 (2014).

- [10] J.R. Nicholls, A.M. Vidarsson, D. Haasmann, E.Ö. Sveinbjörnsson and S. Dimitrijev, IEEE Trans. on Electr. Dev. Vol. 67, (9) 3722 3728 (2020).

- [11] E.H. Nicollian and J.R. Brews, MOS Physics and Technology, 1st ed. (John Wiley & Sons Inc., 1982) p. 321-322.

- [12] F. Allerstam, H.Ö. Ólafsson, G. Gudjónsson, D. Dochev and E.Ö. Sveinbjörnsson, J. Appl. Phys. 101, 124502 (2007).

- [13] E. Bano and T. Ouisse, Appl. Phys. Letters Vol. 65, (21) 2723-2724 (1994)

- [14] T. Ouisse, Phys. Stat. Sol. (a) Vol. 162, 339-368 (1997)