# The Improved Reliability Performance of Post-Deposition Annealed ALD-SiO<sub>2</sub>

Submitted: 2021-10-21

Revised: 2022-02-25

Online: 2022-05-31

Accepted: 2022-03-07

A.B. Renz<sup>1,a\*</sup>, O.J. Vavasour<sup>1,b</sup>, P.M. Gammon<sup>1,c</sup>, F. Li<sup>1,d</sup>, T. Dai<sup>1,e</sup>, G.W.C. Baker<sup>1,f</sup>, N.E. Grant<sup>1,</sup>, J.D. Murphy<sup>1,g</sup>, P.A. Mawby<sup>1,h</sup> and V.A. Shah<sup>1,i</sup>

<sup>1</sup>School of Engineering, University of Warwick, Coventry, UK

<sup>a</sup>A.Renz@warwick.ac.uk, <sup>b</sup>o.vavasour.1@warwick.ac.uk, <sup>c</sup>P.M.Gammon@Warwick.ac.uk, <sup>d</sup>f.li.3@warwick.ac.uk, <sup>e</sup>Tianxiang.Dai@warwick.ac.uk, <sup>f</sup>Guy.Baker@warwick.ac.uk, <sup>g</sup>john.d.murphy@warwick.ac.uk, <sup>h</sup>P.A.Mawby@warwick.ac.uk, <sup>i</sup>vishal.shah@warwick.ac.uk

**Keywords:** 4H-SiC, MOSCAP, Atomic layer deposition, Post-deposition annealing,  $N_2O$ , SiO<sub>2</sub>, Reliability, TDDB

Abstract. A systematic capacitance-voltage (C-V) and time-dependent dielectric breakdown (TDDB) study on silicon carbide (SiC) metal-oxide-semiconductor capacitors (MOSCAPs) that use silicon dioxide (SiO<sub>2</sub>) is shown in this paper. Oxides were formed using atomic layer deposition (ALD), low-pressure chemical vapour deposition (LPCVD) or direct thermal growth in nitrous oxide (N<sub>2</sub>O) ambient, where both deposited oxides were post-deposition annealed in N<sub>2</sub>O ambient, too. The electrical characterisation results reveal that the ALD-deposited and N<sub>2</sub>O-annealed oxides show the best capacitance-voltage (C-V) characteristics, with flatband and hysteresis voltages (V<sub>FB</sub>) averaging 1.44 V and 0.41 V, respectively. When measuring the leakage current levels at 175°C, the ALD-deposited MOSCAPs' breakdown electric fields are averaging similar to their counterparts at 9.71 MV/cm. MOSCAPs which utilized ALD-deposited SiO<sub>2</sub> also showed 29% and 345% increased average injected charge-to 63% failure (Q<sub>BD,63%</sub>) at 9 MV/cm and 9.6 MV/cm, respectively, when comparing these devices to their direct thermally grown SiO2 counterparts.

## Introduction

Reliability aspects in 4H-silicon carbide (4H-SiC) gate dielectrics, such as an insulator lifetime, threshold voltage ( $V_{TH}$ ) stability and high leakage currents, remain an issue of paramount importance, which hamper the further development of 4H-SiC power MOSFETs [1]. Most of the SiO<sub>2</sub>/SiC interface problems, such as carbon clusters, hydrogen (H) and oxygen (O) vacancies, are directly related to the thermal oxidation process [2] and can be bypassed by using deposition processes. Among deposition techniques, atomic layer deposition (ALD) offers specific advantages, such as very low deposition temperature, excellent process control[3] and suitability for conformal deposition of gate oxides in trench structures [4]. Deposition of oxide layers is then usually followed by a post-deposition anneal (PDA) in a nitrogen-containing ambient[5], such as nitrous oxide (N<sub>2</sub>O) or nitric oxide (NO)[2], to overcome the as-deposited layer's poor electrical quality.

In this investigation, we present the excellent reliability performance of ALD-deposited SiO<sub>2</sub> layers on SiC, specifically time-dependent dielectric breakdown (TDDB) characterisation of metal-oxide-semiconductor capacitors (MOSCAPs). The results will be shown for N<sub>2</sub>O post-deposition annealed samples. Here, the distribution of interface parameters, as well as the results from TDDB, will be investigated as metrics of improvement following the PDA process. For benchmarking, processes will be compared to LPCVD-deposited devices, which have undergone the same PDA, and direct thermally grown oxides[5], to demonstrate the superior process quality.

## **Experimental**

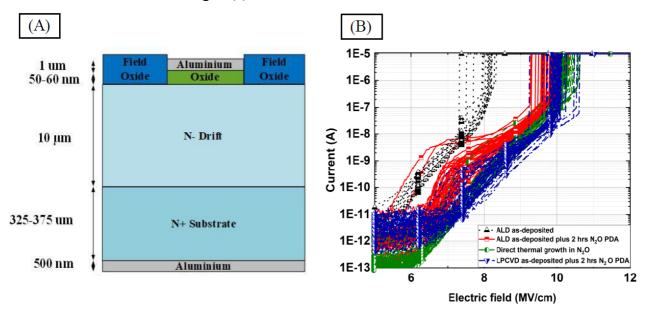

The active 10  $\mu$ m thick epitaxial layer of 4 × 10<sup>15</sup> cm<sup>-3</sup> n-type doping was grown in house on 100 mm diameter, 4° off-axis 4H-SiC wafers. Growth was performed using a 30  $\mu$ m/hr growth rate and nitrogen (N<sub>2</sub>) as a dopant, in an LPE ACiS M8 chemical vapour deposition (CVD) reactor. After an initial clean, a 1  $\mu$ m thick field oxide was deposited and a window was opened via photolithography and reactive ion etching (RIE). Then, quarter wafers underwent one of the three oxidation routines: 1. SiO<sub>2</sub> plasma deposition at 200°C using bis(diethylamino)silane (BDEAS) and O<sub>2</sub> plasma precursors in an Ultratech Fiji G2 Plasma-Enhanced ALD system. 2. SiO<sub>2</sub> deposition at 750 °C using tetraethyl orthosilicate (TEOS) as a precursor in a Thermco LPCVD system. 3. Direct thermal growth of SiO<sub>2</sub> in a HiTech furnace at 1300°C for 5 hrs in N<sub>2</sub>O ambient. Samples from the first two routines then underwent a PDA in the HiTech furnace, in N<sub>2</sub>O at 1300°C for 2 hrs. All oxidation measurements resulted in oxide thicknesses between 50 and 60 nm, which were verified using cross-sectional transmission electron microscopy (TEM) measurements. Finally, 500 nm aluminium (Al) backside contacts were deposited, before a 1  $\mu$ m Al layer was deposited on the topside of the samples by means of a liftoff process. A cross-sectional diagram of the fabricated final device structure is shown in Fig. 1 (a).

Figure 1: (a) Cross-section of the fabricated device structures. (b) Leakage current distribution of the measured devices at  $175^{\circ}$ C, with a device area of  $7.86 \times 10^{-5}$  cm<sup>2</sup>.

#### **Results**

Table 1 shows the key electrical parameters, extracted using room temperature capacitance-voltage (C-V) measurements, combined with current-voltage (I-V) and constant field TDDB measurements at 175°C. C-V measurements reveal the already poor quality of ALD as-deposited SiO<sub>2</sub> layers, with flatband voltages averaging 13.94 V and high frequency dispersion in accumulation. All MOSCAPs utilising oxides which were formed in a N<sub>2</sub>O ambient showed significant improvements. V<sub>FB</sub> is greatly improved for all N<sub>2</sub>O-processed samples, with the ALD oxide with PDA offering the lowest flatband voltage, at 1.44 V. Frequency dispersion was greatly reduced for all N<sub>2</sub>O-processed samples, down to a negligible level of <0.2 % per decade. Although the ALD as-deposited sample shows the lowest hysteresis, the other two deposited layers still showed hysteresis values of 0.41 V, lower than the 0.60 V of the thermally-grown oxide. These results indicate a good general quality of the thermal oxide and of the deposited oxides after PDA.

Figure 1 (b) shows the leakage current distribution of the MOSCAPs at 175°C, analysed as a precursor to TDDB, and table 1 shows the extracted breakdown electric field (E<sub>BD</sub>) values. The ALD as-deposited samples showed high leakage current at low voltage and premature breakdown at 8.58 MV/cm and were therefore excluded from the TDDB study. The remaining samples, all formed in a N<sub>2</sub>O ambient, showed significant improvement, with E<sub>BD</sub> averaging in a similar range, between 9.71 MV/cm (ALD SiO<sub>2</sub> with PDA) and 10.04 MV/cm (direct thermal growth). TDDB measurements were then performed for constant field values of 9 MV/cm and 9.6 MV/cm, and both the time to 63% failure (T<sub>fail,68%</sub>) and injected charge to 63% failure (Q<sub>BD,63%</sub>) were extracted.

Table 1: Key electric parameters of the different MOSCAPs. For flatband voltage, hysteresis and frequency dispersion values, at least 20 devices were measured for each annealing condition at room temperature and all values are given with standard deviations. For I-V analysis and TDDB analysis, at least 50 devices were measured for each split, at 175°C.

| Sample                 | E <sub>BD</sub> (MV/cm) | V <sub>FB</sub> (V) | Hysteresis<br>(V) | Freq. disp. (% per decade) | 9 MV/cm               |                      | 9.6 MV/cm             |                      |

|------------------------|-------------------------|---------------------|-------------------|----------------------------|-----------------------|----------------------|-----------------------|----------------------|

|                        |                         |                     |                   |                            | T <sub>fail,63%</sub> | Q <sub>BD,63</sub> % | T <sub>fail,63%</sub> | Q <sub>BD,63</sub> % |

|                        |                         |                     |                   |                            | (s)                   | (C/cm <sup>2</sup> ) | (s)                   | (C/cm <sup>2</sup> ) |

| ALD                    | 8.58                    | 13.94               | 0.31              | 12.27                      |                       |                      |                       |                      |

| As-dep.                | ± 0.87                  | $\pm 0.71$          | ± 0.08            | ± 14.10                    | -                     | -                    | -                     | -                    |

| SiO <sub>2</sub>       | ± 0.67                  | ± 0.71              | ± 0.06            | ± 1 <b>4.</b> 10           |                       |                      |                       |                      |

| ALD SiO <sub>2</sub>   | 9.71                    | 1.44                | 0.41              | 0.18                       |                       |                      |                       |                      |

| plus N <sub>2</sub> O  | ± 1.38                  | ± 0.20              | ± 0.03            | ± 0.06                     | 4786                  | 7.79                 | 120                   | 0.76                 |

| PDA                    | ± 1.36                  | ± 0.20              | ± 0.03            | ± 0.00                     |                       |                      |                       |                      |

| LPCVD SiO <sub>2</sub> | 9.83                    | 1.77                | 0.41              | 0.13                       |                       |                      |                       |                      |

| plus N2O               | ± 1.09                  | ± 0.23              | ± 0.15            | ± 0.06                     | 3715                  | 5.40                 | 65                    | 0.13                 |

| PDA                    | ± 1.07                  | ± 0.23              | ± 0.15            | ± 0.00                     |                       |                      |                       |                      |

| Direct                 | 10.04                   | 2.20                | 0.60              | 0.16                       |                       |                      |                       |                      |

| thermal                | ± 1.38                  | $\pm 0.12$          | ± 0.26            | ± 0.03                     | 3020                  | 5.86                 | 75                    | 0.22                 |

| growth                 | ± 1.50                  | 0.12                | ± 0.20            | ± 0.05                     |                       |                      |                       |                      |

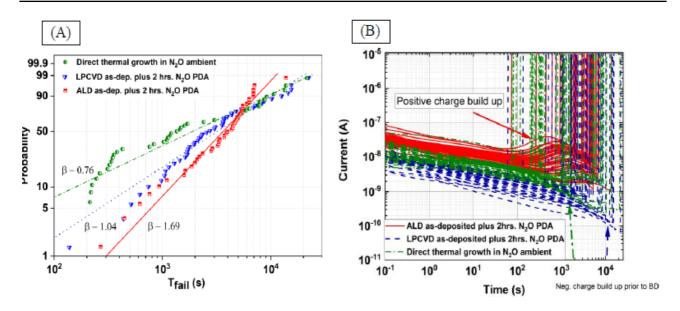

Weibull plots and I-t graphs are shown in Fig. 2, panel (a) and (b) respectively. The ALD oxide with PDA showed the best reliability for all 4 metrics, whereas the LPCVD and thermal oxides gave similar, lower values. For the lower field value of 9 MV/cm, the ALD oxide improves  $T_{fail,63\%}$  by 29%, compared to the LPCVD oxide, and  $Q_{BD,63\%}$  by 33%, compared to the thermal oxide. For the higher field value of 9.6 MV/cm, the ALD oxide offers a larger improvement, increasing  $T_{fail,63\%}$  by 60% and  $Q_{BD,63\%}$  by 345%, compared to the thermal oxide. Fig. 2 (b) shows that the breakdown mechanism has changed for the ALD oxide with PDA, showing buildup of positive charge in the MOSCAPs before negative charge triggers breakdown.

Figure 2: (a) Weibull probability distribution and shape factors of more than 50 MOSCAPs for each fabrication process, when stressed at a constant field of 9 MV/cm at T=175°C. (b) Current over time for the same devices which were stressed at 9 MV/cm, T = 175°C. ALD N<sub>2</sub>O samples showed distinct positive charge build up prior to negative charge build up and breakdown, which could be seen for the whole dataset.

#### Conclusion

High-quality, high-reliability SiO<sub>2</sub> layers, formed by ALD and post-deposition anneal (PDA), have been demonstrated. Flatband voltage and hysteresis are reduced, compared to thermally grown oxide, and frequency dispersion in accumulation is negligible. At 175°C, the oxide critical electric field is in line with thermally grown oxide and LPCVD oxide with PDA. The ALD oxide with PDA has demonstrated higher reliability than LPCVD and thermal oxide in TDDB, offering 29% to 345% improvement. The ALD oxide shows different degradation mechanisms to the LPCVD and thermal oxides, with positive charge building up before breakdown.

# Acknowledgement

The work presented in this paper has been carried out as part of EPSRC projects EP/P017363/1 and EP/R00448X/1.

#### References

- [1] P. Moens, J. Franchi, J. Lettens, L. De Schepper, M. Domeij, and F. Allerstam, "A charge-to-breakdown (q bd) approach to sic gate oxide lifetime extraction and modeling," in 32<sup>nd</sup> International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 78-81, 2020.

- [2] P. Fiorenza *et al.*, "Interfacial electrical and chemical properties of deposited SiO2 layers in lateral implanted 4H-SiC MOSFETs subjected to different nitridations," *Applied Surface Science*, vol. 557, p. 149752, 2021.

- [3] S. M. George, "Atomic layer deposition: an overview," *Chemical reviews*, vol. 110, no. 1, pp. 111-131, 2010.

- [4] A. Renz *et al.*, "The improvement of atomic layer deposited SiO2/4H-SiC interfaces via a high temperature forming gas anneal," *Materials Science in Semiconductor Processing*, vol. 122, p. 105527, 2021.

- [5] K. Tachiki, M. Kaneko, T. Kobayashi, and T. Kimoto, "Formation of high-quality SiC (0001)/SiO<sub>2</sub> structures by excluding oxidation process with H<sub>2</sub> etching before SiO<sub>2</sub> deposition and high-temperature N<sub>2</sub> annealing," *Applied Physics Express*, vol. 13, no. 12, p. 121002, 2020.