Submitted: 2021-10-14 Revised: 2022-03-01 Accepted: 2022-03-02 ublications Ltd, Switzerland. Online: 2022-05-31

# Electrical Scanning Probe Microscopy Investigation of Schottky and Metal-Oxide Junctions on Hetero-Epitaxial 3C-SiC on Silicon

F. Giannazzo<sup>1,a\*</sup>, P. Fiorenza<sup>1,b\*</sup>, E. Schilirò<sup>1,c</sup>, S. Di Franco<sup>1,d</sup>, S. Monnoye<sup>2,e</sup>, H. Mank<sup>2,f</sup>, M. Zielinski<sup>2,g</sup>, F. La Via<sup>1,h</sup> and F. Roccaforte<sup>1,i</sup>

<sup>1</sup>CNR-IMM, Strada VIII 5 95121, Catania, Italy <sup>2</sup>NOVASiC, Savoie Technolac, BP267, F-73375 Le Bourget-du-Lac Cedex, France

<sup>a</sup>filippo.giannazzo@imm.cnr.it, <sup>b</sup>patrick.fiorenza@imm.cnr.it, <sup>c</sup>emanuela.schiliro@imm.cnr.it, <sup>d</sup>salvatore.difranco@imm.cnr.it, <sup>e</sup>smonnoye@novasic.com, <sup>f</sup>hmank@novasic.com, <sup>g</sup>mzielinski@novasic.com, <sup>h</sup>francesco.lavia@imm.cnr.it, <sup>i</sup>fabrizio.roccaforte@imm.cnr.it

\*corresponding author

**Keywords:** scanning capacitance microscopy; conductive atomic force microscopy; 3C-SiC; Schottky; MOS

**Abstract.** This paper presents a macro- and nanoscale electrical investigation of Schottky and metaloxide junctions with hetero-epitaxial 3C-SiC layers grown on Si. Statistical current-density-voltage (J-V) characterization of Pt/3C-SiC Schottky diodes showed an increase of the reverse leakage current with increasing the devices diameters. Furthermore, C-V and J-V analyses of  $SiO_2/3C$ -SiC capacitors revealed non-idealities of the thermal oxide, such as a high trapped positive charge ( $3\times10^{12}$  cm<sup>-2</sup>) and a reduced breakdown field ( $E_{BD}$ =6.5 MV/cm) compared to ideal  $SiO_2$ . Nanoscale electrical characterizations by conductive atomic force microscopy (CAFM) and scanning capacitance microscopy (SCM) allowed to shed light on the origin of non-ideal behavior of Schottky and thermal oxide junctions, by correlating the morphological features associated to 3C-SiC crystalline defects with local current transport and carrier density.

#### Introduction

The cubic polytype of silicon carbide (3C-SiC) has been studied since a long time, as it could give some advantages with respect to 4H-SiC in MOSFET devices, i.e. a high inversion channel mobility [1,2]. Hence, it is considered a good candidate for power electronics applications in the voltage range 600-900V [3]. However, the large density of defects in hetero-epitaxial 3C-SiC on Si currently limits the performances of both Schottky and MOS devices based on this material. In particular, the impact of stacking faults (SF) and anti-phase-boundaries (APBs) on the reverse leakage current and on the forward turn-on voltage of Schottky diodes is debated [4,5]. Furthermore, the origin of the extrinsic mechanisms responsible for the observed degradation and premature breakdown of 3C-SiC MOS capacitors [6] is still unclear. Considering the detrimental effect of crystalline defect (such as the threading dislocation) in 4H-SiC MOSFETs reliability under high temperature reverse bias stress[7], it is mandatory to fully investigate the role of crystalline defects in 3C-SiC MOS-based structures to address the real intrinsic reliability for future power electronics application.

In this paper, Schottky contacts and thermal oxide (SiO<sub>2</sub>) insulators on hetero-epitaxial 3C-SiC/Si layers have been investigated by means of nanoscale electrical characterizations [8,9], i.e. conductive atomic force microscopy (CAFM) and scanning capacitance microscopy (SCM), with the aim to correlate the morphological features associated to 3C-SiC crystalline defects with local current transport and carrier density.

## **Experimental**

Unintentionally doped 10.2 µm thick 3C-SiC layers were grown on on-axis Si(100) substrates by chemical vapor deposition (CVD) using silane (SiH<sub>4</sub>) and propane (C<sub>3</sub>H<sub>8</sub>) as silicon and carbon precursors [10]. After the growth, a chemical mechanical polishing of the surface was carried out to reduce the roughness.

On a first sample, Pt Schottky diodes were fabricated by formation of a Ni<sub>2</sub>Si Ohmic front contact (by Ni lift-off and thermal annealing at 950 °C), followed by lift-off of circular Pt contacts with different radius (from 5 to 25  $\mu$ m) [8]. On a second 3C-SiC sample, a ~40 nm thermal oxide (SiO<sub>2</sub>) was grown at 1150 °C, 1 hour, in dry O<sub>2</sub>. Lateral metal—oxide semiconductor (MOS) capacitors were obtained by lift-off of Ni/Au metal electrodes, consisting of a circular inner gate (radius 50  $\mu$ m), surrounded by a large-area electrode. Electrical characterization (I-V and/or C-V) of the Schottky diodes and MOS capacitors were carried out in a CASCADE Microtech probe station, using a Keysight B1505A parameter analyzer. Nanoscale electrical characterizations, namely Conductive Atomic Force Microscopy (CAFM) and Scanning Capacitance Microscopy (SCM), have been performed using a DI3100 system by Bruker with a Nanoscope V controller, using conductive (Pt or diamond coated) tips. Current maps were acquired on the bare 3C-SiC surface and after the growth of a thin (~10 nm) thermal oxide, properly chosen to apply an electric field up to 10 MV/cm with the tip using the maximum bias (10 V) allowed by our CAFM setup. Furthermore, the same CAFM tip was used to contact the Pt diodes with different areas and perform current—voltage measurements.

#### **Results and Discussion**

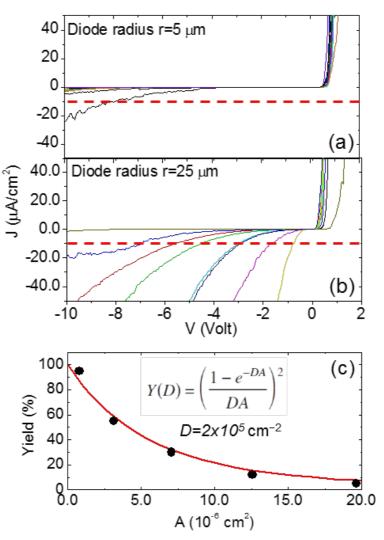

Fig. 1(a) and (b) show two sets of J-V curves collected on arrays of Pt/3C-SiC Schottky diodes with 5 and 25  $\mu$ m radius. Noteworthy, the curves collected on the larger diodes showed a significantly higher leakage current density at negative bias, with a larger spread between different devices. Fig.1(c) shows the "yield" of working devices, defined as the percentage of analyzed diodes with a leakage below a threshold current density of  $10~\mu\text{A/cm}^2$ . The red line is the fit of the data with the function reported in the insert of Fig.1(c), commonly employed to describe the yield of electronic devices, where A is the contact area and D is the areal density of defects responsible for devices failure [4]. The evaluated density (D=2×10<sup>5</sup> cm<sup>-2</sup>) from the fit can be associated with the extended defects responsible for a leakage current exceeding the fixed threshold. This areal density corresponds to a typical average distance L=D<sup>-1/2</sup>≈20  $\mu$ m between the defects.

**Fig.1** J-V curves collected on arrays of diodes with (a) 5  $\mu$ m and (b) 25  $\mu$ m radius. (c) Percentage of diodes (yield) with a reverse leakage lower than 10  $\mu$ A/cm<sup>2</sup>, as a function of diode area. The red line is the fit with the function reported in the insert, where D is the density of defects responsible for the leakage.

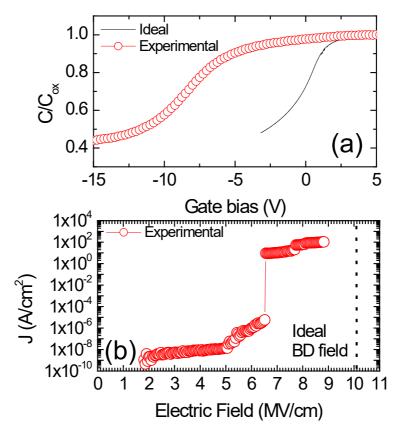

The electrical quality of the thermal oxide on 3C-SiC was evaluated by means of C-V and J-V measurements on MOS capacitors. Fig. 2(a) shows the measured C-V curve compared with the calculated one. The nominal oxide thickness (~40 nm) was confirmed by the measured accumulation capacitance, whereas the net doping concentration ( $N_D$ - $N_A$ =2×10<sup>16</sup> cm<sup>-3</sup>) in the 3C-SiC layer was estimated from the depletion capacitance. As compared to the ideal curve, the experimental C-V curve exhibits a negative shift, with a flat band voltage  $V_{FB}$ =-7.5 V, corresponding to a 3×10<sup>12</sup> cm<sup>-2</sup> density of trapped positive charges in the thermal oxide. Furthermore, using the conductance method, an interface states density  $D_{it}$ =8×10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup> was estimated at 0.1 eV below the 3C-SiC conduction band edge. Fig. 2(b) shows the J-V curve collected on the lateral MOS capacitor, showing a significantly lower breakdown field ( $E_{BD}$ =6.5 MV/cm) with respect to the theoretical value for SiO<sub>2</sub> (~10 MV/cm).

**Fig.2** (a) C-V curve measured at 1 kHz on a 3C-SiC MOS capacitor compared with the calculated curve; (b) Current density vs voltage (J-V) curve of a 3C-SiC MOS capacitor. The value of the ideal SiO<sub>2</sub> breakdown electric field is indicated by the dashed line.

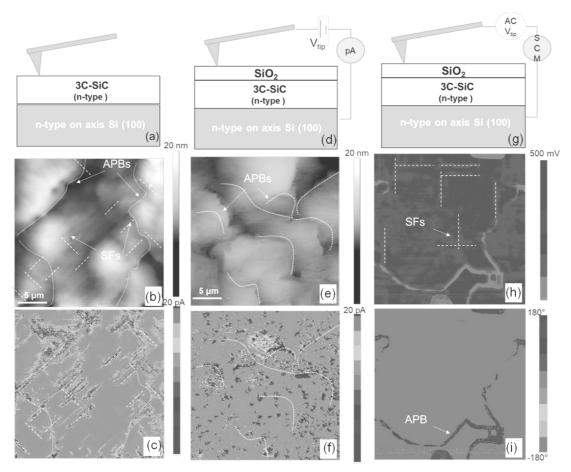

In the following, the nanoscale electrical characterization of the bare 3C-SiC surface and after the growth of a thin (~10 nm) thermal oxide are reported. The CAFM metal tip (working as local Schottky contact) was preliminarily employed to probe the conduction on the 3C-SiC bare surface, as illustrated in Fig. 3(a). Fig. 3(b) and (c) show the surface morphology and the current map, collected simultaneously with a tip bias  $V_{tip}$ =0.5V. Under this forward polarization, preferential conductive paths are visible on the 3C-SiC bare material, such as the anti-phase boundaries (APBs), indicated as dotted curved lines, and stacking faults (SFs), indicated as straight dashed lines [8]. Furthermore, current maps collected at negative tip bias (not shown) revealed that APBs are the main conductive defects under reverse polarization. Interestingly, their distance (10-20  $\mu$ m) is similar to the average value obtained from statistical analysis of macroscopic diodes.

Fig. 3(d) shows a schematic illustration of the CAFM setup on the SiO<sub>2</sub>/3C-SiC system [9]. The morphology of the as-grown oxide (Fig. 3(e)) resembles the one of the bare 3C-SiC material, i.e., characterized by terraces separated by darker lines associated with the APBs. The SiO<sub>2</sub> surface roughness (RMS) was in the order of 5 nm, a value comparable to those measured directly on 3C-SiC layer before oxidation, demonstrating the conformal growth of the oxide onto the substrate, confirmed also by cross-section TEM analyses [9].

Fig. 3(f) reports the simultaneously collected current map by the positively biased conductive tip with  $V_{tip}$ =8 V. It can be considered as a breakdown map of an array of nano-MOS capacitors simultaneously stressed at 8 MV/cm. The BD events are not randomly distributed but there are some regions with a larger density, located in correspondence with some APBs. Noteworthy, the SFs were not visible in the case of 3C-SiC covered by thermal SiO<sub>2</sub>. The SCM experimental setup is illustrated in Fig. 3(g), whereas Fig. 3(h) and (i) show two representative images of the SCM signal amplitude  $|\Delta C|$  and of the phase signal. In particular, both straight line features resembling SFs (dashed lines) and curved line features resembling APBs can be distinguished in the SCM amplitude image in Fig. 3(h), whereas only APBs features can be observed in the phase map in Fig. 3(i). The spatial variations in the SCM amplitude are related to local changes in the carrier density in the 3C-SiC layer.

Interestingly, Fig. 3(i) shows a strong change of the SCM phase signal from 180° on APBs to -180° on the surrounding regions indicating a local increase of the minority carriers (holes) concentration in the 3C-SiC material. Thus, the APBs may act also as a preferential sites for positive charges trapping. On the other hand, the presence of positively charged APBs can cause an enhanced electron injection from the semiconductor into the insulator and the preferential dielectric breakdown close to these extended defects. This can explain the reduced E<sub>BD</sub> observed in large area MOS capacitors.

**Fig.3** (a) C-AFM setup for current mapping of 3C-SiC/Si, (b) surface morphology and (c) current map. (d) CAFM setup for current mapping of SiO<sub>2</sub>/3C-SiC, (e) surface morphology and (f) current map. (g) SCM setup for surface carrier profiling of SiO<sub>2</sub>/3C-SiC, maps of SCM amplitude (h) and phase (i) signal.

#### Conclusion

Electrical characterization of Schottky and thermal-oxide junctions with 3C-SiC showed non-idealities in the device behavior, e.g. high reverse leakage current in Schottky diodes and premature dielectric breakdown of MOS capacitors. Nanoscale electrical characterizations by CAFM and SCM allowed to shed light on the microscopic origin of these phenomena, by correlating the morphological features associated to 3C-SiC crystalline defects with local current transport and carrier density.

### Acknowledgements

M. Zimbone and C. Bongiorno (CNR-IMM, Catania) are acknowledged for their contributions with TEM analyses. This work has been supported by the European project CHALLENGE (Call: H2020-NMBP-2016-2017, grant. agreement 720827).

## References

- [1] H. Nagasawa, M. Abe, K. Yagi, T. Kawahara, N. Hatta, phys. stat. sol. (b) 245, 1272 (2008)

- [2] M. Kobayashi, et al., Mater. Sci. Forum 679-680, 645 (2011)

- [3] F. Li, F. Roccaforte, G. Greco, P. Fiorenza et al., Materials 14, 5831 (2021).

- [4] J. Eriksson, M-H. Weng, F. Roccaforte, F. Giannazzo, et al., Appl. Phys. Lett. 95, 081907 (2009).

- [5] G. Fisicaro, C. Bongiorno, I. Deretzis, F. Giannazzo, et al., Appl. Phys. Rev. 7, 021402 (2020).

- [6] F. Li, Q. et al. IEEE Trans. Electr. Dev., 67, 237 (2020).

- [7] P. Fiorenza, et al. Nanotechnology 31, 125203 (2020)

- [8] F. Giannazzo, et al. Adv. Electron. Mater., 6, 1901171 (2020)

- [9] P. Fiorenza, et al. Appl. Surf. Sci. 526, 146656 (2020).

- [10] M. Zielinski, et al., Mater. Sci. Forum 924, 306 (2018).