# Design and Characterization of 10 kV High Voltage 4H-SiC p-Channel IGBTs with Low V<sub>F</sub>

Submitted: 2021-09-24

Revised: 2022-02-15

Online: 2022-05-31

Accepted: 2022-03-17

Xiaoli Tian<sup>1,a\*</sup>, Chengzhan Li<sup>3,b</sup>, Yu Yang<sup>1,2,c</sup>, Wang Feng<sup>1,2,d</sup>, Jiang Lu<sup>1,e</sup>, Changwei Zheng<sup>3,f</sup>, Chengyue Yang<sup>1,g</sup>, Yun Bai<sup>1,h</sup> and Xinyu Liu<sup>1,i</sup>

<sup>1</sup>Institute of Microelectronics of Chinese Academy of Sciences, Beijing, China <sup>2</sup>College of Microelectronics, University of Chinese Academy of Sciences, Beijing, China <sup>3</sup>CRRC Times Electric Co. Ltd, Zhuzhou, China

<sup>a</sup>tianxiaoli@ime.ac.cn, <sup>b</sup>lichengzhan@ime.ac.cn, <sup>c</sup>yangyu@ime.ac.cn, <sup>d</sup>fengwang@ime.ac.cn, <sup>e</sup>lujiang@ime.ac.cn, <sup>f</sup>zhengcw@csrzic.com, <sup>g</sup>yangchengyue@ime.ac.cn, <sup>h</sup>baiyun@ime.ac.cn, <sup>i</sup>liuxinyu@ime.ac.cn

Keywords: 4H-SiC, IGBT, High Voltage, Forward Voltage Drop

Abstract. The 10 kV silicon carbide p-channel insulated gate bipolar transistors (IGBTs) with low forward voltage drop ( $V_F$ ) have been fabricated and characterized successfully. The novel edge termination structure of Four-Region Multistep Field Limiting Rings (FRM-FLRs) and the optimum JFET region design proposed in our previous work is adopted to improve the blocking performance and the on-state characteristics. The fabricated device with a chip size of 6 mm  $\times$  6 mm and an active area of 0.16 cm<sup>2</sup> exhibits a high blocking voltage of -10 kV with a small leakage current below -200 nA. Meanwhile, a low forward voltage drop of -8 V at the collector current of -10 A with a gate bias of -20 V is obtained at room temperature, corresponding to a current density of 62.5 A/cm<sup>2</sup>. Besides, a lower gate leakage current is measured less than 2 nA at the gate voltage of -30 V. Experimental results demonstrate that a better trade-off between the blocking voltage and the on-state characteristics is achieved for the fabricated device, which is desirable for the high power applications.

#### Introduction

The increasing pursuit of the efficient power conversion for the high voltage applications like smart grid and traction has generated significant interest in the silicon carbide (SiC) devices due to its superior material properties, such as the wide bandgap, high critical electric field, and high thermal conductivity. Compared with SiC MOSFET, 4H-SiC IGBTs are considered to be favorable due to the low on-state loss because of their conductivity modulation [1]. Both p-channel and n-channel 4H-SiC IGBTs have been demonstrated with high voltage ability [2-4]. Meanwhile, the p-channel IGBTs have received much attention from some research groups due to the easier fabrication and low resistivity n-type SiC substrates [5]. In recent years, much research has been focused on achieving high blocking performance and low on-state characteristics simultaneously [6-9]. The first 5.8kV 4H-SiC planar p-IGBT was demonstrated in 2006 [10]. A 12 kV p-IGBT with the V<sub>F</sub> of 5.3V at 100A/cm<sup>2</sup> was presented by Zhang et al. in 2008 [4]. Ryu et al. has reported the 20kV n-channel SiC IGBT with the on-state voltage of 6.4V in 2014 [7]. Recently, the blocking voltage of 27kV and the V<sub>F</sub> of 11.7V at 20A has been achieved by Brunt et al. [9]. However, some issues should still be solved to improve the performance of SiC IGBTs, such as the low carrier lifetime, the low channel mobility, relatively high leakage current and forward voltage drop  $(V_F)$ . To achieve the best device performances, many technical solutions have been made to pursue a better trade-off between the high blocking ability and low  $V_{\rm F}$  [11,12].

In this paper, a domestic 10kV 4H-SiC p-channel IGBTs with low  $V_F$  is designed by using Silvaco TCAD simulation and fabricated with experimental verification. Experimental results indicate that a better trade-off between the blocking voltage and the on-state characteristics is achieved.

### **Design and Fabrication**

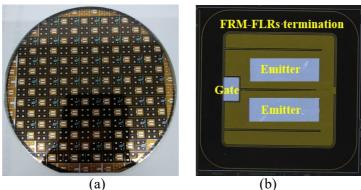

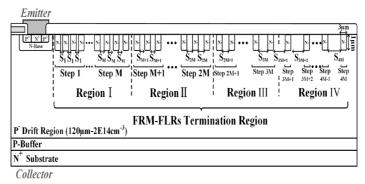

Fig. 1 shows a schematic structure of the 4H-SiC p-channel IGBT. The epitaxial layers were grown on a 4-inch n-type 4H-SiC substrate with 4° off axis. The 100 µm thick p-type drift layer with a doping concentration of  $4 \times 10^{14}$  cm<sup>-3</sup> and a 2.5 µm thick p-type buffer layer at a doping concentration of  $1.5 \times 10^{17}$  cm<sup>-3</sup> were utilized for the device fabrication [13]. The n-type substrate served as the electron injector layer for the p-IGBTs. The n-base with a retrograde profile was formed by implantation of nitrogen  $(2.8 \times 10^{13} \text{ cm}^{-2})$  to meet the needs of the threshold voltage and blocking voltage. The n+ contact and p+ emitter were implanted with nitrogen  $(4.35 \times 10^{15} \text{ cm}^{-2})$  and aluminum ( $7 \times 10^{14}$  cm<sup>-2</sup>), respectively [13]. All the implants were activated at 1800 °C with a carbon capping on the surface to avoid the step-bunching effect [14]. The channel length was about 1 µm formed by a non-self-aligned implantation technique. A four-region multistep field limiting rings (FRM-FLRs) termination structure demonstrated in our previous work was used around the device periphery to relieve the electric field crowding and decrease the leakage current at high blocking voltage [15]. The gate oxide with a thickness of 50 nm was grown by dry thermal oxidation and then annealed in nitric oxide at 1300 °C to reduce the density of interface states and improve the channel carrier mobility. Polysilicon was deposited as a gate. Al/Ti contacts were deposited as the p-type ohmic metal, and Ni was deposited as the n-type collector contact metal. The fabricated IGBT has a chip size of 6 mm × 6 mm and an active area of 0.16 cm<sup>2</sup>. Fig. 2 shows the photograph of the fabricated 4H-SiC p-IGBT wafer and the top view of a 4H-SiC p-IGBT.

Fig. 1. Schematic structure of the 4H-SiC p-IGBT

**Fig. 2.** Photograph of the fabricated SiC p-IGBT wafer (a) and top view of the SiC p-IGBT (b)

In order to obtain a better trade-off between breakdown voltage (BV) and  $V_F$ , the device structure is optimized by TCAD simulation based on our previous work [13]. The bandgap narrowing model, Auger recombination (AUGER) and Shockley-Read-Hall (SRH) recombination model, incomplete ionization model, doping and temperature dependent mobility models are used in the ATLAS device simulator. The material parameters of 4H-SiC used in the device simulations are presented in Table 1.

| Parameters                | Value                 | Meaning                                                 |

|---------------------------|-----------------------|---------------------------------------------------------|

| Eg300 (eV)                | 3.26                  | Band gap at 300K                                        |

| Permittivity              | 9.8                   | Permittivity                                            |

| Affinity                  | 3.7                   | Affinity                                                |

| AUGN (cm <sup>6</sup> /s) | 5 ×10 <sup>-31</sup>  | Auger recombination parameter for electrons             |

| AUGP (cm <sup>6</sup> /s) | 2 ×10 <sup>-31</sup>  | Auger recombination parameter for holes                 |

| TAUN0 (s)                 | 1.2 ×10 <sup>-6</sup> | Lifetime model parameter for electrons                  |

| TAUP0 (s)                 | 1 ×10 <sup>-7</sup>   | Lifetime model parameter for holes                      |

| Nsrhn (cm <sup>-3</sup> ) | $3 \times 10^{17}$    | SRH concentration-dependent lifetime model for electron |

| Nsrhp (cm <sup>-3</sup> ) | 3 ×10 <sup>17</sup>   | SRH concentration-dependent lifetime model for holes    |

Table 1. 4H-SiC parameters used in p-IGBT simulations

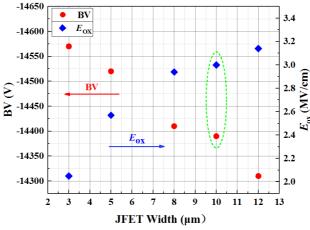

The width of the JFET region ( $L_{\rm JFET}$ ) dependence of the BV and the  $V_{\rm F}$  are investigated particularly. Fig. 3 shows the BV and the maximum gate oxide electric field ( $E_{\rm OX}$ ) above the JFET region with the variations of  $L_{\rm JFET}$ . As  $L_{\rm JFET}$  increases, the BV decreases gradually, while the  $E_{\rm OX}$  is increasing.

Fig. 3. Simulation results of BV and maximum  $E_{OX}$  with different  $L_{JFET}$

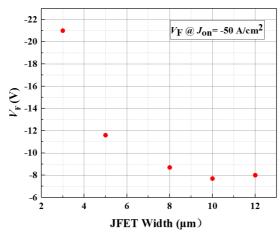

Fig. 4. Effect of  $L_{\text{JFET}}$  on the  $V_{\text{F}}$  at -50 A/cm<sup>2</sup> of current density

Fig. 4 shows the effect of  $L_{\rm JFET}$  on the  $V_{\rm F}$  at -50 A/cm<sup>2</sup> of current density. It can be seen that the  $V_{\rm F}$  decreases gradually with the increase of  $L_{\rm JFET}$  due to the decrease of JFET resistance. According to the simulation results, the  $L_{\rm JFET}$  of 10  $\mu$ m was adopted as the optimum structure to fabricate the 4H-SiC p-IGBT. Simulation results reveal that the BV of -14.38 kV and  $V_{\rm F}$  of -7.7V at the collector current density of -50 A/cm<sup>2</sup> is achieved, while the  $E_{\rm OX}$  is 3 MV/cm at the -10 kV blocking voltage, which is a widely accepted criterion for long-term gate oxide reliability [16].

#### **Results and Discussions**

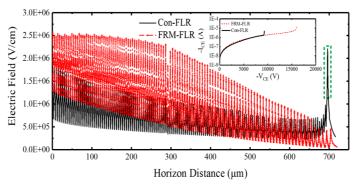

Fig. 5 shows the blocking characteristics of the fabricated 4H-SiC p-IGBT at room temperature. The IGBTs were tested with the gate grounded to the emitter and the high voltage applied to the collector by using Agilent B1505A at a wafer-level chip. During the blocking characteristic measuring, the devices were immersed in Fluorinert liquid to prevent arcing in air. It can be seen that the leakage current is lower than -200 nA at -10 kV without a distinct breakdown behavior. It should be noted that a higher bias voltage (>10 kV) is limited owing to the maximum equipment ability. That means a higher blocking ability can be achieved by using the FRM-FLRs termination structure, which is illustrated in detail in our previous work [15]. As seen in Fig. 6, the FRM-FLRs edge termination is divided into four regions. Each region includes multistep field limiting rings. Therefore, the surface electric field of the FRM-FLRs is more uniform to reduce the electric field crowding around the device periphery effectively and achieve a higher blocking voltage of -16 kV shown in Fig. 7.

**Fig. 5.** Blocking characteristics of the 4H-SiC p-IGBT at 25 °C

**Fig. 6.** Schematic cross-section of FRM-FLRs applied in 4H-SiC IGBT [15]

**Fig. 7.** Comparison of electric field distribution and blocking characteristics for FRM-FLRs and Con-FLRs [15]

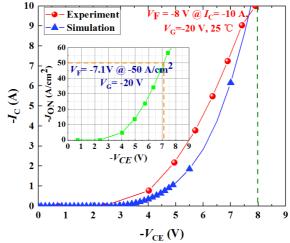

Fig. 8 shows the experimental and simulated forward I-V characteristics of the p-IGBT with a negative gate bias at room temperature. It can be seen that the I-V characteristic of simulation indicates a good fitting effect with the result from the experiment. The measured  $V_F$  is -8 V at a collector current ( $I_C$ ) of -10 A with a gate bias of -20 V, corresponding to a current density of 62.5 A/cm<sup>2</sup>. The on-state current density ( $J_{ON}$ ) characteristics are also shown in Fig. 8. Experimental results prove that the fabricated p-IGBT has the  $V_F$  of -7.1 V at  $J_{ON}$  of -50 A/cm<sup>2</sup> with a gate bias of -20 V.

Fig. 8. On-state I-V characteristics of the fabricated p-IGBTs

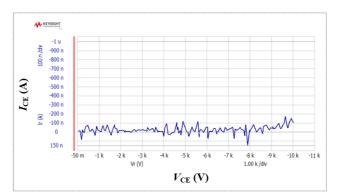

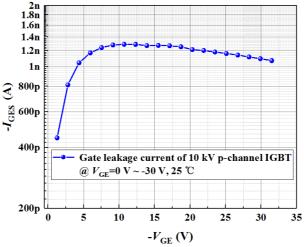

Fig. 9. Experiment result of  $I_{GES}$  under  $V_{GES}$  pressure

Fig. 9 shows the gate leakage current characteristics of the fabricated device at the gate-emitter voltage testing, which is important to evaluate the gate oxide reliability. It can be seen that the gate leakage current of a p-IGBT is lower than -2 nA at the gate bias voltage from 0 to -30 V, which meets the reliability requirement for the actual application.

#### **Conclusion**

A 4H-SiC p-channel IGBT with 10 kV blocking voltage and low  $V_{\rm F}$  has been designed, fabricated and characterized in this paper. The device with a chip size of 6 mm × 6 mm and an active area of 0.16 cm<sup>2</sup> shows that the blocking voltage is -10 kV with a small collector leakage current, which is attributed to the FRM-FLRs termination structure design given by our previous work. Moreover, the  $V_{\rm F}$  of -8 V is achieved at  $I_{\rm C}$ = -10 A and  $V_{\rm GS}$  = -20V, indicating a current density of 62.5 A/cm<sup>2</sup>. The measured gate leakage current of lower than -2 nA at  $V_{\rm GS}$  = -30V is reliable for the actual application. Most importantly, the better trade-off characteristics of the fabricated p-IGBTs are acquired, which is desirable for use in high power electric systems.

## Acknowledgments

This work is supported by the High Technology Industrialization Special Fund of Cooperation between JiLin Province and Academy under Grant No. 2021SYHZ0030 and the Key Research and Development Program of Guangdong Province under Grant No. 2019B090917010.

#### References

- [1] X. Wang, and J. A. Cooper, High-Voltage n-Channel IGBTs on Free-Standing 4H-SiC Epilayers, IEEE Trans. Electron Devices. 57.2 (2010) 511-515.

- [2] S. Katakami, H. Fujisawa, K. Takenaka, et al., Fabrication of a P-channel SiC-IGBT with high channel mobility, Mater. Sci. Forum. 740-742 (2013) 958-961.

- [3] S. Ryu, C. Capell, C. Jonas, et al., 15 kV IGBTs in 4H-SiC, Mater. Sci. Forum. 740-742 (2013) 954-957.

- [4] Q. Zhang, M. Das, J. Sumakeris, et al., 12-kV p-Channel IGBTs with Low On-Resistance in 4H-SiC, IEEE Electron Device Lett., 29.9 (2008) 1027-1029.

- [5] Q. Zhang, J. Wang, C. Jonas, et al., Design and Characterization of High-Voltage 4H-SiC p-IGBTs, IEEE Trans. Electron Devices. 55.8 (2008) 1912-1919.

- [6] E. Brunt, L. Cheng, M. O'Loughlin, et al., 22 kV, 1 cm<sup>2</sup>, 4H-SiC n-IGBTs with Improved Conductivity Modulation, 2014 Proc. 26th Int. Symp. Power Semicond. Devices IC's, Hawaii, America, June 2014, 358-361.

- [7] S. Ryu, C. Capell, C. Jonas, et al., 20 kV 4H-SiC N-IGBTs, Mater. Sci. Forum. 778-780 (2014) 1030-1033.

- [8] K. Fukuda, D. Okamoto, M. Okamoto, et al., Development of Ultrahigh-Voltage SiC Devices, IEEE Trans. Electron Devices. 62.2 (2015) 396-404.

- [9] E. V. Brunt, L. Cheng, M. O'Loughlin, et al., 27 kV, 20 Ampere-rated 4H-SiC n-IGBTs, Mater. Sci. Forum. 821-823 (2015) 847-850.

- [10] Q. Zhang, C. Jonas, S. Ryu, et al., Design and fabrications of high voltage IGBTs on 4H-SiC, in *Proc. ISPSD*, Naples, Italy, June 2006, 285-288.

- [11] D. Okamoto, M. Sometani, S. Harada, et al., Improved Channel Mobility in 4H-SiC MOSFETs by Boron Passivation, IEEE Electron Device Lett., 35.12 (2014) 1176-1178.

- [12] T. Kimoto, K. Kawahara, B. Zippelius, et al., Control of carbon vacancy in SiC toward ultrahigh-voltage power devices, Superlattices and Microstructures. 99 (2016) 151-157.

- [13] X. Tian, B. Tan, Y. Bai, et al., Simulation Study for the Structural Cell Design Optimization of 15kV SiC p-Channel IGBTs, Mater. Sci. Forum, 963 (2019) 666-669.

- [14] H. Shen, Y. Tang, Z. Peng, et al., Fabrication and Characterization of 1700V 4H-SiC Vertical Double-Implanted Metal-Oxide-Semiconductor Field-Effect Transistors, Chin. Phys. Lett., 32. 12 (2015) 127101-1-4.

- [15] B. Tan, X. Tian, J. Lu, et al., Design and Optimization of Four-Region Multistep Field Limiting Rings for 10kV 4H-SiC IGBTs, 2018 Proc. 14th IEEE Int. Conf. Solid-state and Integrated Circuit Technology, Qingdao, China, Nov 2018, 1-3.

- [16] H. Jiang, J. Wei, X. Dai, et al., SiC Trench MOSFET with Shielded Fin-Shaped Gate to Reduce Oxide Field and Switching Loss, IEEE Electron Device Lett., 37.10 (2016) 1324-1327.