Revised: 2022-02-22 Accepted: 2022-03-17 © 2022 The Author(s). Published by Trans Tech Publications Ltd, Switzerland. Online: 2022-05-31

Submitted: 2021-10-13

# Investigation of SiC Thyristors with Varying Amplifying Gate Design

Sigo Scharnholz<sup>1,a\*</sup>, Ralf Hassdorf<sup>1,b</sup>, Dirk Bauersfeld<sup>1,c</sup>, Bertrand Vergne<sup>1,d</sup>, Luong Viêt Phung<sup>2,e</sup> and Dominique Planson<sup>2,f</sup>

<sup>1</sup>French-German Research Institute of Saint-Louis (ISL), 5 rue du Général Cassagnou, 68300 Saint-Louis, France

<sup>2</sup>Univ Lyon, INSA Lyon, Université Claude Bernard Lyon 1, Ecole Centrale de Lyon, CNRS, AMPERE, F-69621, Lyon, France

asigo.scharnholz@isl.eu, bralf.hassdorf@isl.eu, cdirk.bauersfeld@isl.eu, dbertrand.vergne@isl.eu, eluong-viet.phung@insa-lyon.fr, fdominique.planson@insa-lyon.fr

\*corresponding author

Keywords: Thyristor, Amplifying gate, Device fabrication, Etched JTE, Turn-on characteristic, Onstate characteristic.

Abstract. This paper presents experimental 1.2 kV, 10 A SiC thyristors with different amplifying gate design. In contrast to comparative devices (with simple gate) the amplifying gate thyristors show a characteristic snap-back and a higher gate current to trigger. Their gate-anode I-V characteristics comply with the underlying design constraint, regarding the resistances of pilot and main thyristor:  $R_P > R_M$ . Moreover, the turn-on waveforms of well-designed amplifying gate thyristors reveal peakshaped inversions in the gate current and voltage transients, providing clear evidence of the successive triggering of pilot and main thyristor.

## Introduction

Due to their superior performance in terms of current density and blocking voltage, silicon carbide (SiC) thyristors are of particular interest for pulsed power applications [1-3]. Furthermore, in view of the tremendous progress made in SiC crystal quality and wafer size, large-area SiC thyristors appear to be in reach today. In this context, both electrically and optically triggered SiC thyristors require adequate amplifying gate structures. With the aim to investigate this aspect, a mask set featuring numerous SiC thyristor devices with varying amplifying gate structures has been conceived [4]. And based thereon, a 100 mm epitaxial SiC wafer was processed recently. Resulting from this process run, the present paper reports on the electrical characteristics measured on-wafer as well as on singularized and encapsulated SiC thyristor devices with and without amplifying gate.

### **Device Fabrication and Structure**

The fabricated devices are asymmetrically blocking, vertical SiC thyristors, of which the 10 µm thick p-base (drift) layer ( $5 \times 10^{15}$  cm<sup>-3</sup>) is separated by a 4  $\mu$ m p-type buffer ( $5 \times 10^{17}$  cm<sup>-3</sup>) from the wafer substrate (>  $1 \times 10^{19}$  cm<sup>-3</sup>). The n-base (gate) and the anode layers have a nominal thickness (and doping concentration) of 2  $\mu$ m (1×10<sup>17</sup> cm<sup>-3</sup>) and 1  $\mu$ m (1×10<sup>19</sup> cm<sup>-3</sup>), respectively. The gate and the single-step junction termination extension (JTE) are formed simultaneously by reactive ion etching (RIE). A second RIE step was used to define the JTE length and thus the device mesa. Following the etching, the primary metallization of gate/cathode (Ti/Ni) and anode (Ni/Ti/Al) was realized separately by e-beam evaporation, lift-off, and subsequent annealing. The surface was passivated with 1 μm thick, deposited SiO<sub>2</sub>. The over-metallization consists of 1 μm Al and 0.7 μm Ti/Ni/Au on the top-side (anode/gate) and the backside (cathode) contacts, respectively.

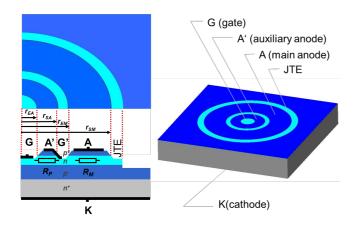

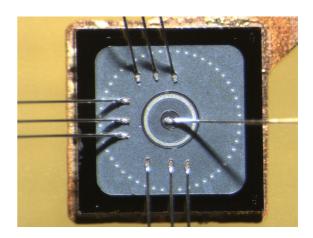

Fig. 1 shows a scheme of a circular SiC amplifying gate thyristor with characteristic dimensions (radii). All fabricated amplifying gate thyristors have a central, circular gate (G) with a radius of  $r_{EA}$  = 160  $\mu$ m and a main anode (A), expanding from an inner radius of  $r_{EM} = 500 \mu$ m to a distance of  $r_{SM} =$ 1200 μm. Therefore, all devices have the same size of the anode and thus the same resistance R<sub>M</sub> of the main thyristor (*cf.* cross-section in Fig.1). At the distance of  $r_{SM}$ , either ring-shaped or dotted anode shorts are situated for devices with a circular or a square-shaped anode, respectively. With a JTE length of 150  $\mu$ m and a security margin to the cutting edge, the die size measures 3.2 mm  $\times$  3.2 mm (0.1 cm<sup>2</sup>). Fig. 2 depicts one of the experimental amplifying gate thyristors with square-shaped anode and dotted anode shorts.

Fig. 1. Scheme of an SiC amplifying gate thyristor, consisting of a pilot thyristor (index P) in the centre and a main thyristor (index M) with the characteristic resistances  $R_P$  and  $R_M$ .

Fig. 2. Micrograph of an experimental,  $3.2 \times 3.2 \text{ mm}^2$  SiC amplifying gate thyristor with square-shaped anode and dotted shorts ( $r_{SA} = 400 \mu m$ ). Gate (centre) and anode wedge-bonded with 50  $\mu m$  Al wires, cathode (backside) solder attached.

In-between gate and main anode, the amplifying gate is located, consisting of the anode A' of the pilot thyristor and the auxiliary gate G'. The etch-step separating A' and G' forms a circle with varying radius of  $r_{SA}$ . This way, the resulting thyristors meet the amplifying gate design criterion ( $R_P > R_M \Rightarrow r_{SA}/r_{EA} > r_{SM}/r_{EM}$ )\* [4, 5] to different degrees:

- safe ( $r_{SA} = 460 \mu m$ ): the pilot thyristor always triggers the main thyristor

- adequate  $(r_{SA} = 400 \mu m)$ : still ok, but susceptible to technological uncertainties

- non-adequate ( $r_{SA} = 300 \mu m$ ): the pilot is less sensitive than the main thyristor, which may reverse the triggering order, negating the benefits of the pilot.

# **Electrical Characterization**

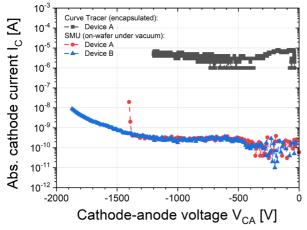

On-wafer (in a vacuum probing chamber), the best devices demonstrated stable blocking up to 2 kV. After dicing, bonding, and encapsulation they were repeatedly tested up to 1.2 kV, the nominal voltage they were conceived for. Fig. 3 exemplarily shows the blocking characteristics (on-wafer and encapsulated) of a square-shaped SiC thyristor with safely designed ( $r_{SA} = 460~\mu m$ ) amplifying gate and dotted anode shorts (device A). For comparison, the characteristic of a thyristor without amplifying gate is shown (device B), representing one of the best devices in terms of blocking capability. The higher leakage current of encapsulated devices is due to the lower current resolution of the curve tracer. The real leakage current (measured using an SMU on an equivalent device) is in the order of some nanoamperes (not shown), and thus only slightly higher than that one measured onwafer under vacuum.

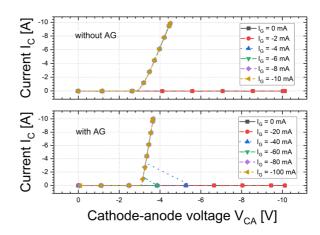

Fig. 4 shows on-state characteristics (at varying gate currents) of the same amplifying gate thyristor (bottom graph) as in Fig. 3 (device A), compared to a device without amplifying gate (top graph). As expected, the amplifying gate thyristor shows a characteristic snap-back. Note that the difference in the differential on-resistance is due to a spread between samples and not a characteristic difference between the two device types.

<sup>\*</sup> The radius r<sub>SA</sub> is the only varying parameter. The other radii, r<sub>EA</sub>, r<sub>SM</sub>, and r<sub>EM</sub> are constant for all devices (cf. text).

By contrast, the fact that the amplifying gate thyristor requires a higher gate current to trigger, means a characteristic difference. For comprehension, note that the amplifying gate thyristors under investigation are experimental devices with a small periphery (main thyristor). They have been conceived only for the purpose of examining the design constraint. Their amplifying gate has about the same size as the gate of the comparative thyristor (without amplifying gate), but due to the parallel current path formed by R<sub>P</sub> and R<sub>M</sub>, they require a larger gate current to trigger. In terms of a reduced gate current, the amplifying gate only takes advantage when it supplies the gate current via an interdigitated structure to a large area (main) thyristor.

Fig. 3. Forward blocking characteristics of two SiC thyristors measured on-wafer with an SMU (up to breakdown) and after bonding and encapsulation with a curve tracer (limited to 1.2 kV).

Fig. 4. On-state characteristics of encapsulated SiC thyristors with and without amplifying gate (AG).

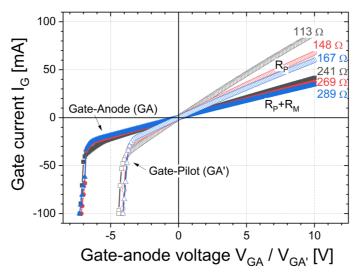

Fig. 5 shows the gate-anode I-V characteristics of three SiC thyristors with differently dimensioned amplifying gate (non-adequate, adequate and safe, cf. above), allowing to determine the characteristic resistances  $R_P$  and  $R_M$  of pilot and main thyristor, respectively.  $R_P$  is directly derived from the slope of the I-V characteristic measured between the gate contact G (in the centre) and the ring shaped anode A' of the pilot thyristor (cf. Fig 1). In the same way,  $R_P + R_M$  (and thus  $R_M$ ) is determined from the slope of the I-V characteristic measured between G and the main anode A. Tab. 1 summarizes the extracted values which confirm the compliance to the above mentioned design rule ( $R_P > R_M$ ).

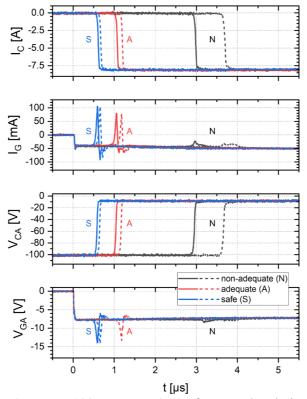

Finally, Fig. 6 shows turn-on characteristics of circular and square SiC thyristors disposing of ring-shaped and dotted anode-shorts, respectively. For each of these two types, the curves of three devices with differently dimensioned amplifying gate are shown. Note, that though giving the impression of a logical sequence, there is no coherence of the turn-on delay time with the individual device dimensions. It appears rather that devices with adequately and safely designed amplifying gate reveal a peak-shaped inversion in the gate current and voltage transients, while non-adequately designed devices do not. These peaks originate from the current passing through the anode A' of the pilot thyristor, delivering the gate current for the main thyristor. This way they prove evidence that the pilot thyristor is triggered in advance of the main thyristor, which obviously does not emerge for thyristors with non-adequately designed amplifying gate.

### Conclusion

The results presented in this paper demonstrate that the experimental SiC amplifying gate thyristors under investigation can be triggered adequately fully compliant to the underlying design constraints. Furthermore, the measurements reveal relatively large resistances R<sub>P</sub> and R<sub>M</sub> of pilot and main thyristor, respectively, being causal for meeting these constraints. Anyway, the main part of the resistance, here quantitatively about 70%, is determined by the sheet resistance of the n-base layer (gate) underneath the two sub-thyristors. The rest, however, as calculations based on TLM

measurements indicate, must be attributed to the contact resistance to the n-base layer. Nevertheless, this relatively high amount does not negatively affect the adherence to the design rule. In so far, the conceived amplifying gate structures can be used as design building blocks for larger area, electrically or optically triggered SiC thyristors.

Fig. 5. Gate-anode characteristics (measured on-wafer) of SiC thyristors with differently dimensioned amplifying gate (cf. Tab.1).

Tab. 1. Resistance R<sub>P</sub> and R<sub>M</sub> extracted from Fig. 5.

|         | Non-adequate | Adequate | Safe  |

|---------|--------------|----------|-------|

| $R_{P}$ | 113 Ω        | 148 Ω    | 167 Ω |

| $R_{M}$ | 125±3 Ω      |          |       |

Fig. 6. Turn-on characteristics ( $V_{CA,0} = -100 \text{ V}$ ,  $I_{C,on} = -8 \text{ A}$ ) of encapsulated SiC thyristors with circular (solid lines) and square-shaped (dotted lines) anode, each with differently dimensioned amplifying gate (cf. legend).

# Acknowledgement

Financial support provided by the French DGA under the research program ASTRID, contract no. ANR-11-ASTR-0011, is gratefully acknowledged.

#### References

- [1] S. Ryu, D.J. Lichtenwalner, M. O'Loughlin, C. Capell, J. Richmond, E. van Brunt, C. Jonas, Y. et al., 15 kV n-GTOs in 4H-SiC, Materials Science Forum Vol. 963 (2019), p. 651.

- [2] M. Agamy, F. Tao, and A. Elasser, A high speed SiC thyristor gate driver for pulse power applications, in Proceedings of the IEEE Energy Conversion Congress and Exposition (Baltimore, MD, USA, 2019) p. 5694.

- [3] H. O'Brien, A. Ogunniyi, et al., High-Voltage Silicon Carbide Thyristors on N-Doped Epi for Pulsed Power, in Proceedings of the IEEE Int. Pulsed Power Conf. (Denver, CO, USA, 2021).

- [4] S. Scharnholz, L.V. Phung, D. Tournier, B. Vergne, R. Hassdorf, P. Brosselard, and D. Planson, Conception de thyristors SiC permettant l'étude de l'amplification interne de l'allumage, in Proceedings of the Symposium de Génie Electrique (Cachan, France, 2014).

- [5] B.J. Baliga, Fundamentals of Power Semiconductor Devices, Springer, New York, 2008, p. 675.