# On the Short Circuit Electro-Thermal Failure of 1.2 kV 4H-SiC MOSFETs with 3D Cell Layouts

Submitted: 2021-10-13

Revised: 2022-02-21

Online: 2022-05-31

Accepted: 2022-03-07

Nazareno Donato<sup>1,a\*</sup>, Kaloyan Naydenov<sup>1,b</sup>, Florin Udrea<sup>1,c</sup>, Andrei Mihaila<sup>2,d</sup>, Gianpaolo Romano<sup>2,e</sup>, Stephan Wirths<sup>2,f</sup> and Lars Knoll<sup>2,g</sup>

<sup>1</sup>Department of Engineering, University of Cambridge, Cambridge, UK.

<sup>2</sup>Hitachi ABB Power Grids, Semiconductors, Lenzburg, Switzerland.

and391@cam.ac.uk, bkn334@cam.ac.uk, cfu1000@cam.ac.uk, dandrei.mihaila@ch.abb.com, egianpaolo.romano@ch.abb.com, fstephan.wirths@ch.abb.com, glars.knoll@hitachi-powergrids.com

**Keywords:** SiC MOSFET; TCAD modelling; 3D cell geometry; short circuit robustness.

**Abstract.** In this manuscript, the short circuit (SC) capability of 1.2 kV vertical double diffused SiC MOSFET with different layout topologies is investigated. 3D finite element electro-thermal simulations have been carried out in order to assess the performance of five different cell topologies. It has been found that while the maximum drain current density observed during a SC event agrees well with the specific on-state resistance behaviour, the maximum temperature evolution in the unit cell follows the opposite trend. This behaviour can be explained by the relatively poor spreading of the carriers in the JFET region (of the atomic lattice layout (ALL)) at small cell pitches (CP)  $\sim$  8  $\mu$ m, which can lead to the formation of a filament with a high current density and heat generation.

#### Introduction

Initially manufactured for the 600 V range by Rohm in 2010 and immediately followed by the first commercial 1.2 kV 4H-SiC MOSFET from Cree, SiC MOSFETs are now commercially available in either discrete or module configurations mainly for automotive and traction applications. Regarding MOSFETs, manufacturers have 4H-SiC opted for different (symmetric/asymmetric trench, planar etc.), in order to tackle issues related to the low mobility at the Si-face, dielectric reliability, gate charge hysteresis, NBTI and PBTI, and bipolar degradation[1-2]. Compared to Si-counterparts, SiC MOSFETs allow for an increased power density and maximum junction temperature (Timax), while improving the efficiency and reducing the size of the power electronic system. While the maximum junction temperature itself does provide a useful indication of the device's resistance towards abnormal electrical events such as unclamped inductive switching (UIS) and short circuit (SC), fast thermal transients due to the high-power density are often what limits the reliability of the device, the metallization, and the packaging material[3]. In this context, advanced unit cell topology could be beneficial in suppressing the contribution related to the channel resistance and reducing the fast dT/dt. In Si, the unit cell layout is known to affect several static (specific on-state resistance (R<sub>ON</sub>S) and breakdown voltage BV) and dynamic (C<sub>GD</sub>/C<sub>GS</sub> ratio) electrical characteristics of the power MOSFET [4]. Nevertheless, to date, the impact of the cell layout on the short circuit (SC) performance has not been reported yet in the literature. Thus, this study presents a complete investigation on the thermal runaway failure mechanism for several SiC MOSFET layouts. This type of failure mechanism is obtained when the thermally generated carrier concentration exceeds the background doping concentration and the device reaches an intrinsic state with the formation of a low Ohmic current-path.

## Methodology

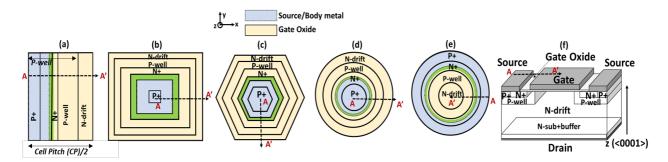

The different cells analysed are displayed in Fig. 1(a-e). Circular and ALL have been solved by means of cylindrical coordinates. Conversely, the array and Hex layouts have been simulated by using 3D unit cells that account for 1/8 and 1/12 of the total cell. Ideal Neumann conditions have been applied to the geometrical boundaries. A layer of positive fixed charges (1.75x10<sup>12</sup> cm<sup>-2</sup>) has been added at the SiC/SiO<sub>2</sub> interface. The drift (buffer) region's doping and thickness have been set to 10 µm (1  $\mu$ m) and  $1x10^{16}$  cm<sup>-3</sup> ( $5x10^{18}$  cm<sup>-3</sup>). The implanted profiles have been matched from a process-based simulation, both the p+/n+ regions are 1 µm long and the channel length is fixed at 300 nm for all the geometries. The threshold voltage is identical for all topologies analysed in this study.

Fig. 1. Top views of (a) stripe (b) array, (c) hex, (d) circular, (e) ALL, (f) cross-section of the stripe.

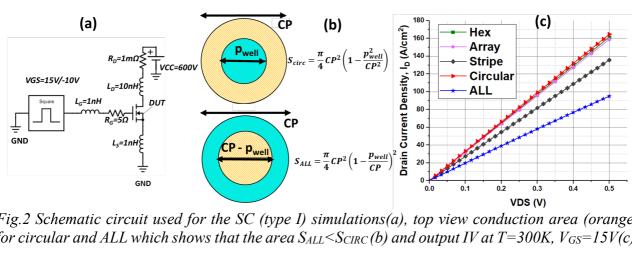

The SC capability of each structure is examined through single pulse short circuit (type I) mixedmode simulations, using the circuit in Fig. 2(a). A single thermal interface has been added at the drain contact with a specific thermal resistance of 0.3 cm<sup>2</sup> K/W. This situation reproduces well the typical heat transfer configuration in which the top area of the device is less thermally conductive compared to the substrate. Reflective heat boundary conditions have been assumed at the geometrical boundaries of the device. For the purpose of this work, thermo-mechanical effects, convection and radiation heat exchange, gate oxide failure or cell-to-cell unbalances have not been accounted for [5].

### **Results and Discussion**

Fig. 2 Schematic circuit used for the SC (type I) simulations(a), top view conduction area (orange) for circular and ALL which shows that the area  $S_{ALL} < S_{CIRC}(b)$  and output IV at T=300K,  $V_{GS}=15V(c)$ .

$$\frac{\partial (c_L T)}{\partial t} = \vec{\nabla} \cdot (\kappa \nabla T) - \vec{\nabla} \cdot (\vec{J}(\varphi_{F,n} + \Pi)) + \dot{Q}_{transient} + \hbar \omega G_{opt}$$

(1)

$$\dot{Q}_{transient} = (E_C + \frac{3}{2}k_BT)(R_{net} - \vec{\nabla} \cdot \vec{J}/q)$$

(2)

$$-\vec{\nabla} \cdot \left( \vec{J} (\varphi_{F,n} + \Pi) \right) = \frac{J^2}{\sigma} - T \vec{J} \cdot \nabla S_{Seebeck} - (\varphi_{F,n} + \Pi) \vec{\nabla} \cdot \vec{J}$$

(3)

In Fig.2(c), the simulated R<sub>ON</sub>S for SiC devices reproduces well the experimental and theoretical trends observed in [1] for Si-devices, with the circular MOSFET outperforming the other layouts in terms of R<sub>ON</sub>S. Similar ON-state performance (as well as SC performance in Fig.3(a) and breakdown voltage, not shown) can be observed for the array, hex, and circular layouts.

Note that the formation of the channel along the Si-face (x-y plane) allows for the variation of the channel mobility along the different crystal faces (which could affect the outcome of the comparison for trench-based MOSFETs) to be neglected. The structure's electrothermal response is described, using the classical thermodynamic model (Eq.1-3) [6-7].

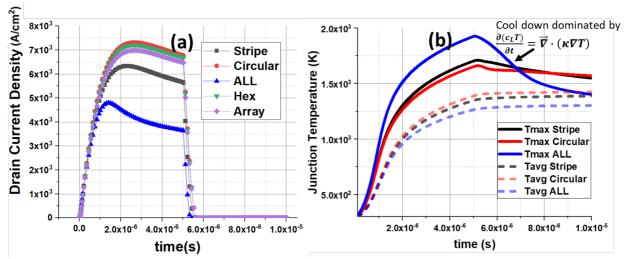

This expression is based on the continuity equation, which relates the rate of change of the internal energy of the system (composed of the lattice and the carriers) to the energy flux due to conduction via Fourier's law, Joule and Thomson heating (second term), optical generation, and an additional term, which accounts for the energy's dynamic variation with the carrier density. The Peltier coefficient  $\Pi$  here is computed assuming Thomson's second relation and Mott's formula for the Seebeck coefficient. The SC drain current density ( $J_D$ ) and the maximum and average lattice temperatures ( $T_{max}$ ,  $T_{avg}$ ) for a 5 $\mu$ s SC pulse ( $CP=8\mu$ m) are shown in Fig. 3 (a-b). It can be observed that  $T_{avg}$  follows the same trend (with the cell's topology) as  $J_D$ . This also agrees with the (expected) variation of  $R_{ON}$ S with the cell layout (shown in Fig. 2 (c)).

Conversely,  $T_{max}$  varies in the exactly opposite way. The increased local heat generation in the ALL cell can be explained with the stronger (local) Joule heating effect (where  $Q_{Joule} = J^2/\sigma$  as shown in Eq.3). Indeed, the ALL's smaller JFET area density (calculated in Fig. 2(b)) limits the spreading of the current and hence increases the (local) current density, effectively creating a current filament.

Fig. 3 SC waveforms of (a) the drain current density and (b)  $T_{avg}$  and  $T_{max}$  for a fixed CP=8  $\mu m$ .

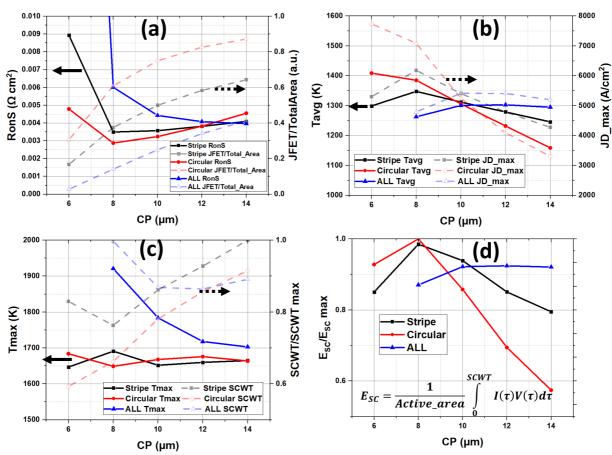

Fig.4. (a)RonS (T=300K) and JFET area/total cell area for different CP; (b)Average junction temperature(Tavg) at t=5  $\mu$ s and maximum SC drain current density(JD\_max); (c) Maximum junction temperature (Tmax) at t=5  $\mu$ s and normalized short circuit withstand time (SCWT) extracted at the value at which JD reaches again JD\_max due to current density increase related to the thermal runaway; (d) normalized short circuit critical energy density vs CP for different layouts.

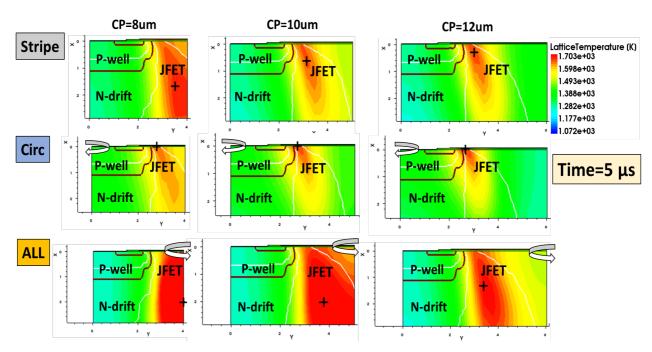

The cells' behaviour for different CPs is presented in Fig. 4 (a-d). Here Tavg correlates well with the peak short circuit current (J<sub>D max</sub>) and the critical SC energy (E<sub>sc</sub>). Indeed, the higher T<sub>avg</sub> of the circular reduces the SCWT due to premature thermal runaway. More interesting is the evolution of T<sub>max</sub> with CP, where a non-monotonic trend can be observed for the circular and stripe designs, but not for the ALL (Fig. 4 (c)). This differs from the variation of the JFET area density in Fig. 4 (a) and can be explained through examination of the temperature distribution in the top of the cell (Fig. 5). In the case of the ALL, the peak temperature point lies deep inside the JFET region (and farther from the channel than in the other designs) for all examined CP (Fig. 5). This is a consequence of the smaller conduction area in the JFET region. At larger CP, however, the JFET component of RonS reduces monotonically, which allows for improved current spreading (in the JFET region) and hence slowly shifts the point of the peak current density (and of Joule heating) to the interface. Conversely, while a similar trend can be seen in the stripe cell, the depth (relative to the surface) of the location of T<sub>max</sub> is smaller (due to the larger JFET area). In fact, for the circular, the point of T<sub>max</sub> remains next to the SiC/SiO<sub>2</sub> interface for all examined CP. Nevertheless, unlike in the ALL, the degree of current spreading in the circular and stripe designs saturates above 10µm CP, due to the newly added lateral resistance along the length of the accumulation layer. Thus, R<sub>ON</sub>S eventually starts to rise with CP (due to the inefficient area consumption). More importantly, this also leads to a saturation of the local Joule heating profile and thus of  $T_{max}$  (unlike in the ALL, where it falls continuously with CP).

Fig. 5. Lattice temperature profile at the top of the unit cell for the stripe, circular and ALL layouts at  $t=5 \mu s$ . The cross mark depicts the location of the peak lattice (junction) temperature point.

# **Conclusion**

In conclusion, this work has clearly demonstrated that there exists a strong correlation between the evolution of the maximum junction temperature (hotspot) and the cell layout, which is not only a function of the JFET area density but also of the current density profile and current spreading in the JFET/accumulation region. Moreover, the average local junction temperature, as well as the location of the hotspot, are both responsible for the device's thermal runaway failure mechanism.

#### References

- [1] Adan, Alberto O., et al. "The Current Status and Trends of 1,200-V Commercial Silicon-Carbide MOSFETs: Deep Physical Analysis of Power Transistors From a Designer's Perspective." IEEE Power Electronics Magazine 6.2 (2019): 36-47.

- [2] Agarwal et al.. "Impact of Cell Topology on Characteristics of 600V 4H-SiC Planar MOSFETs". IEEE Electron Device Letters, 40(5), 773-776.

- [3] Romano, Gianpaolo, et al. "A comprehensive study of short-circuit ruggedness of silicon carbide power MOSFETs." IEEE Journal of Emerging and Selected Topics in Power Electronics 4.3 (2016): 978-987.

- [4] Baliga, B. Jayant. Fundamentals of power semiconductor devices. Springer Science & Business Media, 2010.

- [5] Tsibizov, Alexander, et al. IEEE Transactions on Power Electronics 35.2 (2019): 1855-1865

- [6] Wachutka, G. K., "Rigorous Thermodynamic Treatment of Heat Generation and Conduction in Semiconductor Device Modeling." IEEE Trans. Comput-Aided Des. Integr. Circuits Syst., 9(11), 1141-1149, 1990. DOI: 10.1109/43.62751

- [7] M. Cutler and N. F. Mott, "Observation of Anderson Localization in an Electron Gas.", Physical Review, 181(3), 1336-1340, 1969.