Submitted: 2021-10-21 Revised: 2022-02-08 Accepted: 2022-03-07 © 2022 The Author(s). Published by Trans Tech Publications Ltd, Switzerland. Online: 2022-05-31

# A Scalable SPICE-Based Compact Model for 1.7 kV SiC MOSFETs

Alessandro Borghese<sup>1,a\*</sup>, Michele Riccio<sup>1,b</sup>, Luca Maresca<sup>1,c</sup>, Giovanni Breglio<sup>1,d</sup>. Slavo Kicin<sup>2,e</sup> and Andrea Irace<sup>1,f</sup>

<sup>1</sup>Department of Electrical Engineering and Information Technologies (DIETI), University of Naples Federico II, Naples, Italy

<sup>2</sup>Power Grids Research, ABB Power Grids Switzerland Ltd, Baden-Dättwil, Switzerland <sup>a</sup>alessandro.borghese@unina.it, <sup>b</sup>michele.riccio@unina.it, <sup>c</sup>luca.maresca@unina.it, dgiovanni.breglio@unina.it, eslavo.kicin@hitachienergy.com, fandrea.irace@unina.it

**Keywords:** compact modeling, silicon carbide (SiC) MOSFET, SPICE, power module.

Abstract. This paper presents a compact model implemented in SPICE environment for silicon carbide (SiC) MOSFET. The model is easily adjustable to devices belonging to different voltage and current ratings. A previous release of the model was tuned to match the performance of 1.2 kV and 3.3 kV SiC MOSFETs, while, in this contribution, an improved version of the compact model is calibrated for 1.7 kV devices. The agreement between the experimental and simulated data, achieved for both static and dynamic conditions, associated to the model simulation speed, emphasize its suitability as a tool for the simulation of converter containing wide arrangements of devices.

## Introduction

SiC MOSFETs have become a commercial reality and both discrete devices and power modules are being progressively adopted in several market applications [1]. Given their increasing usage, there is a higher demand for fast and reliable electrothermal compact models of SiC MOSFETs that can help circuit designers in predicting the performance of the final converter. Switching converters are complex electrical machines and a detailed simulation of their efficiency rests upon a precise description of the losses (static and dynamic) of the underlying transistors. Nonetheless, depending on the complexity of the MOSFET model, the simulation of complex converter topologies in SPICElike tools can be a computationally heavy task and a compromise between simulation speed and accuracy usually exists [2], [3]. Furthermore, commercial SiC MOSFETs are available in different classes of breakdown voltage (namely ranging from 650 V to 3.3 kV) and on-state resistance (namely ranging from 15 m $\Omega$  to 1  $\Omega$ ), which increases the need for a common and adjustable modeling platform.

In previous literature contributions, we presented a SPICE-based model for SiC MOSFETs [4] and validated its applicability to 1.2 kV [4] and 3.3 kV [5] commercial devices. To further demonstrate its ease of scalability to family of devices of different voltage ratings, here we calibrate an improved version of the model to fit the electrical behavior of 1.7 kV SiC MOSFETs.

## Methodology

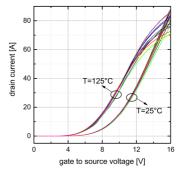

**Experimental Characterization.** The devices under tests (DUTs) are 1.7 kV/60 A-rated SiC MOSFETs. Since the device are provided as bare dies, they were mounted onto a suitable test substrate to enable their electrical characterization (Fig. 1). The isothermal static current-voltage characteristics (I<sub>D</sub> - V<sub>GS</sub> and I<sub>D</sub> - V<sub>DS</sub>) of 17 DUTs were measured by an in-house developed pulsed curve tracer both at 25 °C and at 125 °C. Some parameters determining the on-state current and their spread were evaluated, and the resulting values are reported in Table 1. The MOSFETs exhibit some spread in their current-conduction behavior. Nevertheless, the spread of the transfer characteristics is confined within 15% (Fig. 2). Therefore, the DUT selected as reference for calibrating the model is the one exhibiting the median transfer characteristic. However, the impact of the technological fluctuations on the uneven current sharing can be easily included as reported in [6].

Fig. 1. Example of 1.7 kV SiC MOSFET under test mounted on the test substrate.

Fig. 2. Isothermal transfer characteristics of the 17 SiC MOSFETs under test.

Table 1. Main parameters determining the current conduction and their spread measured at 25 °C.

| Parameter           | Threshold voltage: $V_{TH}[V]$ | Transconductance: $K_P \left[ A/V^2 \right]$ | Channel length modulation parameter: $\lambda [V^{-1}]$ |

|---------------------|--------------------------------|----------------------------------------------|---------------------------------------------------------|

| Mean value ± spread | $5.77 \pm 0.17$                | $0.84 \pm 0.06$                              | $0.03 \pm 0.004$                                        |

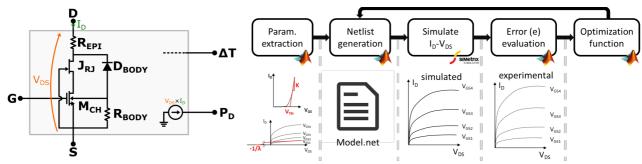

**Description of SiC MOSFET Model.** The compact electrothermal model described in this work is a variant of the one presented in [4]. A schematic representation of its equivalent circuit is reported in Fig. 3, which highlights the main components used to model the static current flow. These are implemented by conventional SPICE primitives, thus aiding convergence and widening the model compatibility. The modulation of charge in the channel region is modeled by a SPICE LEVEL 3 MOSFET (referred to as M<sub>CH</sub>). Following the approach suggested in [7], a standard JFET (J<sub>RJ</sub>) in series with M<sub>CH</sub> was used to describe the modulation of the current path due to the expansion of the space charge region in the JFET area. Such a phenomenon was previously represented in [4] through a voltage dependent resistor. The model is fully electrothermal and includes the temperature dependence of the most relevant physical parameters. Three capacitances determine the dynamic characteristics of the model. These are (i) the gate-to-source capacitance (C<sub>GS</sub>) which is constant and equal to the capacitance of the LEVEL 3 MOSFET M<sub>CH</sub>, (ii) the voltage dependent junction capacitance of the body diode (C<sub>J</sub>), and (iii) the non-linear gate-to-drain capacitance (C<sub>GD</sub>). The latter is modeled by an arctangent function through the relation reported in Eq. 1. This modeling choice ensures excellent simulation speed while keeping convergence issues at minimum, and, although it is reported not to be as accurate as other techniques [3], it will be shown that the simulations produce adequate prediction of the switching power losses.

$$C_{GD}(V_{GD}) = \left(C_{GD00} - C_{GDmin}\right) \left[1 + \frac{2}{\pi} \arctan\left(\frac{V_{GD}}{V_{GD}^*}\right)\right] + C_{GDmin} \tag{1}$$

The model parameters controlling the static electrical performances are calibrated through an automatic routine implemented through MATLAB and SIMetrix and outlined by the flowchart in Fig. 4. A subset of physical parameters, such as the threshold voltage ( $V_{TH}[V]$ ), the current factor ( $K[A/V^2]$ ), and the parameter accounting for the channel-modulation effect ( $\lambda[1/V]$ ), are directly extracted from the experiments ant their values are used as a starting guess of an iterative optimization procedure. The procedure exploits a minimization function provided in the MATLAB optimization toolbox which progressively reduces the gap between the experimental and the simulated data.

Fig. 3. Schematic representation of compact electrothermal model for SiC MOSFET. The capacitances are omitted for the sake of clarity.

Fig. 4. Flowchart of the automatic routine for the optimization the parameters and the calibration of the static curves.

#### Results

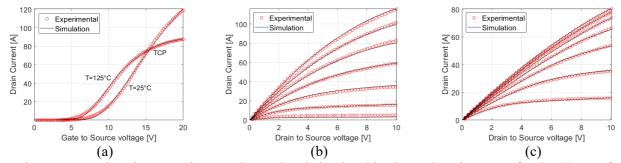

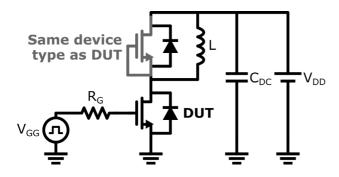

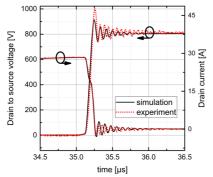

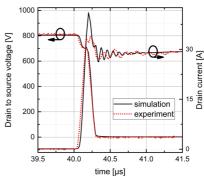

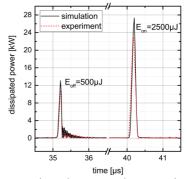

From the comparison reported in Fig. 5 (a) and (b), it can be seen that excellent agreement was achieved between the experimental data and the fitted model at 25 °C. As shown by the data at 125 °C of Fig. 5 (a) and (c), the static behavior at high temperature is also correctly reproduced. To characterize the dynamic performance of the DUT, a double pulse test (DPT) on an inductive load of 1 mH was conducted by placing in series two MOSFETs in a half-bridge configuration. The highside switch acts as a freewheeling diode since the channel conduction was inhibited by connecting the gate and source terminals together. A schematic of the DPT setup is provided in Fig. 6. The test was performed at 800 V - 28 A, with  $R_G = 11 \Omega$  for both 25 °C and 125 °C, and careful evaluation of circuit parasitic components was carried out as it is known that they strongly affect the shape of the waveforms during switching transients [8]. As witnessed by the waveforms of Figs. 7 and 8, the model is able to precisely capture the very fast turn-on ( $dV_{DS}/dt \approx 5.3 \text{ kV/\mu s}$ ,  $dI_D/dt \approx 275 \text{ A/\mu s}$ ) and turn-off  $(dV_{DS}/dt \approx 8.6 \text{ kV/}\mu\text{s}, dI_{D}/dt \approx 225 \text{ A/}\mu\text{s})$  switching transients, including the oscillations caused by the stray components. The accuracy of the of model is also substantiated by the comparison of Fig. 9, where the experimental and simulated waveforms of the power dissipated by the DUT are superimposed. It is worth noticing that the model not only provides a correct estimation of the switching energy, i.e., of the integral of the power dissipated during the commutations, but also of the instantaneous value of the power itself. This is of paramount relevance when it is important to take into account the time evolution of the thermal phenomena since a well-modeled power dissipation translates into an accurate time-dependent heat source [8].

Fig. 5. Comparison between the experimental and simulated isothermal static curves for the (a) transfer characteristics, (b) output characteristics at 25 °C and (c) 125 °C.

### **Summary**

In this paper, a SPICE-based compact model for SiC MOSFET has been presented and calibrated to the experimental data of 1.7 kV devices. The model brings several improvements to a previously published contribution and the results have shown that it can satisfactorily represent the subtleties of the static and dynamic electrical waveforms of 1.7 kV SiC MOSFETs. This type of devices constitutes an additional class of MOSFETs on which the model has been benchmarked, thus proving the ease of scalability of the model itself.

Fig. 6. Schematic of the double pulse test setup adopted for the characterization of the switching transients.

Fig. 8. Comparison between the experimental and simulated current and voltage waveforms obtained during a turn-off event on inductive load at 800 V and 28 A.

Fig. 7. Comparison between the experimental and simulated current and voltage waveforms obtained during a turn-on event on inductive load at 800 V and 28 A.

Fig. 9. Comparison between the experimental and simulated switching power dissipation obtained during a double pulse test at 800 V and 28 A.

## References

- [1] L. Spaziani and L. Lu, Silicon, "GaN and SiC: There's room for all: An application space overview of device considerations," in *Proc. IEEE ISPSD*, 2018, doi: 10.1109/ISPSD.2018.8393590.

- [2] B. W. Nelson *et al.*, "Computational Efficiency Analysis of SiC MOSFET Models in SPICE: Static Behavior," in *IEEE OJ-PEL*, vol. 1, pp. 499-512, 2020, doi: 10.1109/OJPEL.2020.3036034.

- [3] B. W. Nelson *et al.*, "Computational Efficiency Analysis of SiC MOSFET Models in SPICE: Dynamic Behavior," in *IEEE OJ-PEL*, vol. 2, pp. 106-123, 2021, doi: 10.1109/OJPEL.2021.3056075.

- [4] M. Riccio, *et al.*, "A Temperature-Dependent SPICE Model of SiC Power MOSFETs for Within and Out-of-SOA Simulations," in in *Proc. IEEE ISPSD*, vol. 33, no. 9, pp. 8020-8029, Sept. 2018, doi: 10.1109/TPEL.2017.2774764.

- [5] A. Borghese *et al.*, "An Experimentally Verified 3.3 kV SiC MOSFET Model Suitable for High-Current Modules Design," *2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, 2019, pp. 215-218, doi: 10.1109/ISPSD.2019.8757576

- [6] A. Borghese *et al.*, "Effect of Parameters Variability on the Performance of SiC MOSFET Modules," in *Proc. IEEE ESARS-ITEC*, 2018, doi: 10.1109/ESARS-ITEC.2018.8607593.

- [7] ON Semiconductor, "Physically Based, Scalable SPICE Modeling Methodologies for Modern Power Electronic Devices," TND6260/DRev. 2021, 2. Available online: https://www.onsemi.com/pub/Collateral/TND6260-D.PDF (accessed on 07 October 2021).

- [8] C. Scognamillo, *et al.*, "Compact Modeling of a 3.3 kV SiC MOSFET Power Module for Detailed Circuit-Level Electrothermal Simulations Including Parasitics," Energies, vol. 14, no. 15, p. 4683, Aug. 2021. Available: http://dx.doi.org/10.3390/en14154683