Submitted: 2022-08-30 Revised: 2022-11-18 Accepted: 2022-11-25 © 2023 The Author(s). Published by Trans Tech Publications Ltd, Switzerland. Online: 2023-05-26

# **Evaluation of Hysteresis Response in Achiral Edges of Graphene** Nanoribbons on Semi-Insulating SiC

Sobin Mathew<sup>1,a</sup>, Saadman Abedin<sup>1,b</sup>, Vladislav Kurtash<sup>1,c</sup>, Sergei P. Lebedev<sup>2,d</sup>, Alexander A. Lebedev<sup>2,e</sup>, Bernd Hähnlein<sup>2,f</sup>, Jaqueline Stauffenberg<sup>4,g</sup>. Heiko O. Jacob<sup>1,h</sup> and Jörg Pezoldt<sup>1,i\*</sup>

<sup>1</sup>FG Nanotechnologie, Institut für Mikro- und Nanoelektronik and Institut für Mikro- und Nanotechnologien MacroNano®, Technische Universität Ilmenau, Postfach 100565, 98684 Ilmenau, Germany

<sup>2</sup>loffe Institute, 26 Politekhnicheskaya, St. Petersburg, 194021 Russia <sup>3</sup>FG Technische Physik I, Institut für Physik, TU Ilmenau, Postfach 100565, 98684 Ilmenau, Germany

<sup>4</sup>FG Fertigungs- und Präzisionsmesstechnik, Institut für Prozessmess- und Sensortechnik, TU Ilmenau, PF 100565, 98684 Ilmenau, Germany

asobin.mathew@tu-ilmenau.de, bsaadman.abedin@tu-ilmenau.de, °vladislav.kurtash@tu-ilmenau.de, dlebedev.sergey@mail.ioffe.ru, eshura.lebe@mail.ioffe.ru, fbernd.haehnlein@tu-ilmenau.de, gjaqueline.stauffenberg@tu-ilmenau.de, hheiko.jacobs@tu-ilmenau.de, ijoerg.pezoldt@tu-ilmenau.de

Keywords: epitaxial graphene, graphene nanoribbons, field effect transistor, charge trapping, hysteresis.

**Abstract.** Hysteresis response of epitaxially grown graphene nanoribbons devices on semi-insulating 4H-SiC in the armchair and zigzag directions is evaluated and studied. The influence of the orientation of fabrication and dimensions of graphene nanoribbons on the hysteresis effect reveals the metallic and semiconducting nature graphene nanoribbons. The hysteresis response of armchair based graphene nanoribbon side gate and top gated devices implies the influence of gate field electric strength and the contribution of surface traps, adsorbents, and initial defects on graphene as the primary sources of hysteresis. Additionally, passivation with AlO<sub>x</sub> and top gate modulation decreased the hysteresis and improved the current-voltage characteristics.

#### Introduction

Graphene has been widely discussed and gained significant attention in recent decades owing to its unique fundamental low-dimensional physical properties and potential applications [1, 2]. Nonetheless, the existence of the Dirac point, directed to a zero bandgap semiconductor [2], limits its integration into advanced digital electronic applications. However, it has been predicted to exhibit band gaps if the large area of graphene is constrained into a quasi-one-dimensional structure in subnanometer dimensions, making graphene suitable for many field-effect transistor applications at room temperature [3]. Many researchers stem from this significant property of graphene and are motivated to work on small constrictions like graphene nanoribbons (GNRs). In past decades these systems have been investigated at various levels of aspects. According to the studies, the properties of these systems can be tuned to form semiconductors to spin-polarized half metals [4, 5]. Generally, graphene has five edge structures: zigzag, armchair, cove, gulf, and fjord [6]. In contrast to the zigzag-edged graphene structure, which typically exhibits spin-polarized edge states with energy levels close to Fermi level, most other graphene edges show semiconducting properties [4, 6, 7]. Moreover, several studies have tried to experimentally prove the semiconducting properties of GNRs with field-effect devices [8, 9]. Both theoretical and experimental models revealed that the bandgap tunability is dependable on the width of GNRs [2, 3, 9]. However, the GNRs possess rough edges and widths along their ribbon length, which can further alter the bandgap depending upon the edge configurations (thus upon the chirality and number of carbon atoms) and doping [10, 11].

Furthermore, the field-effect studies on GNR based FETs show a hysteresis behavior in the conductance, which varies with sweeping voltage and sweep rate in ambient conditions [12, 13]. However, the hysteretic current-voltage (I-V) characteristics are not beneficial for transistors and integrated circuits. In contrast, the conductance hysteresis in graphene-related two-dimensional materials devices has significant possibilities and excellent potential in nonvolatile memory-based devices. Hence, many researchers have investigated and proposed various mechanisms and factors involved in graphene's origin of hysteresis behavior. However, most of the critical sources of hysteresis are charge transfer or trapping effects, mainly due to absorbates, interface traps, and bulk dielectric traps [12, 14, 15]. Moreover, considering the possible applications, making a systematic study of the physical mechanisms involved in the hysteresis properties of GNRs is a prerequisite for further device development. Therefore, insight into these fundamental properties and functionalities of GNRs is essential for developing GNR-based memory devices. Consequently, this study proposes a systematic evaluation of the hysteresis response of graphene nanoribbon structures in epitaxial graphene on semi-insulating SiC. The hysteresis response of GNRs on the armchair and zigzag directions of epitaxial graphene and dependent factors like width, measurement conditions, etc., were evaluated and studied. Moreover, the hysteresis response of armchair based side and top gated GNR FET devices were evaluated.

## **Experimental**

Graphene has been prepared epitaxially with an orientation on-axis (0001) Si-face on semiinsulating 4H-SiC substrates at substrate temperatures between 1800 and 1900°C by thermal decomposition in an argon ambient [16-18]. The samples have a dimension of 10 x 11 mm<sup>2</sup>. Initially, the samples were cleaned and spin-coated at 4000 rpm with a high-resolution negative resist, hydrogen-silsesquioxane (HSQ) (XR-1541-4%) and immediately baked on a hot plate at 90°C for structuring and fabrication of GNRs. The final resist thickness was about 30 nm. The GNRs were fabricated on epitaxial graphene by electron beam lithography in Raith 150 equipment. For highresolution patterning and fabrication of nanoribbon structures on graphene, the electron beam lithography exposure was carried out at an acceleration voltage of 20 kV and an aperture of 7 µm. Subsequently, the exposed samples were developed with a two-step process in a solution of 3:1 (DI: TMAH) and 9:1(DI: TMAH) for 1 min at room temperature. Then the samples were etched in oxygen for 30 s using an inductively coupled plasma etching technique. The resist was removed by buffered oxide etching (BOE) for 1 min and rinsed in DI for another 1 min. The developed methodology allows the fabrication of GNRs down to sub 10 nm resolutions [8, 19]. The patterning of electrodes was defined by a positive tone electron beam resist PMMA (AR-P 617). The drain and source electrodes were metalized by an electron beam evaporation (Ti=10 nm/Au= 80 nm). In side-gate GNR-FET devices, both channel and side gates are made on graphene itself. For the top gate fabrication, initially a thin layer of Al (8 nm) is deposited using e-electron beam evaporation and oxidized thereafter. The top electrodes were metalized by an electron beam evaporation (Pd=10 nm/Au= 80 nm). The morphology and evaluation of critical dimensions and etching step heights of structured GNRs were measured using scanning electron microscopy (SEM) and atomic force microscopy (AFM) which uses active microcantilevers. The fabricated devices were characterized using SEM and measured using a Keithley 4200 system under a nitrogen environment at ambient conditions.

#### **Results and Discussions**

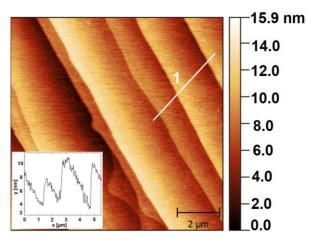

A non-contact AFM image of the surface morphology and profile obtained from pristine epitaxial graphene grown on Si-face of semi-insulating 4H-SiC is depicted in Fig. 1. As illustrated in Fig. 1, graphene is provided with wide micro-step structures. These micro steps like terraces are formed during the graphitization on the surface of SiC. These structures are spread along the edges of SiC due to the step bunching process and often cause inhomogeneity in graphene layer thickness [20, 21].

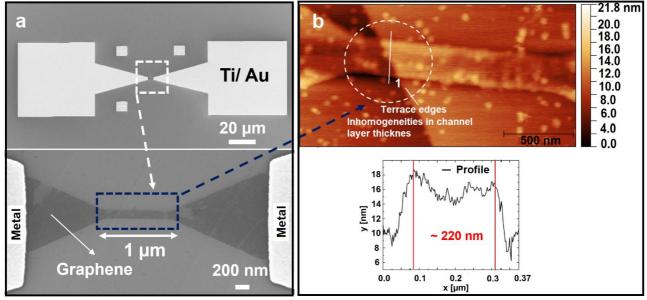

Terraces formed on the surface of graphene have an average width of 1 µm and a step height of 5 to 10 nm. Fig. 2a shows a typical SEM image of the fabricated lateral device. All fabricated lateral devices have a channel length of 1 µm. As shown in the SEM image (see Fig. 2a), Ti/Au contacts were deposited above the GNRs from a two-terminal lateral device. Fig. 2b shows the AFM image of the device's active area with the profile obtained from the channel region. Since the channel region covers the terrace edges, the GNRs formed in such parts of the sample surface has varied graphene thickness. These inhomogeneities in the graphene layer thickness in the terraces and step region further change the electronic transport properties and result in mobility and channel conductance alterations of the graphene channel [22].

Fig. 1. Surface topography AFM images of epitaxial graphene on semi-insulating 4H-SiC and its respective height profile.

Fig. 2. SEM and AFM images of fabricated epitaxial GNR lateral device on semi-insulating 4H-SiC: (a) Single device overview of the lateral device, (b) AFM image of the channel region and height profile obtained across (white line 1) the channel.

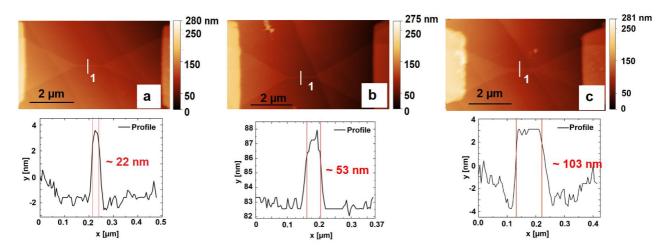

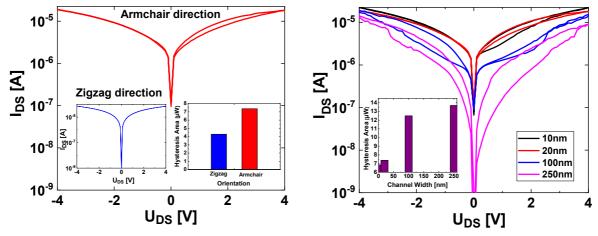

Fig. 3a, 3b and 3c illustrates the AFM images of lateral devices with varying GNR widths, and their height profile obtained across the channel. The values obtained for the AFM profile channel dimensions nearly match the designed values. The channel region has an average step height of 4 to 5 nm. The developed technology could fabricate GNR with varying widths ranging from 20 to 250 nm. The fabricated devices were measured at ambient conditions under nitrogen flux. Fig. 4 (a) shows the DC hysteresis response obtained from a 20 nm GNR lateral device in the armchair direction, and the insets show the hysteresis response in the zigzag direction.

Furthermore, the hysteresis factor, the difference of the areas underneath the upper and lower branches of the hysteresis curves, was used here to quantify hysteresis using the Eq. 1 as follows:

$$Hysteresis\ area,\ H=\int_{V_{min}}^{V_{max}}I_{d}(V_{d})dV_{d\,forward}-\int_{V_{min}}^{V_{max}}I_{d}(V_{d})dV_{d\,backward} \tag{1}$$

Fig. 3. AFM images of fabricated lateral devices with varying GNR widths. Lateral GNR devices with (a) 22, (b) 53 and (c) 103 nm constriction width and the profile obtained across (white line 1) of the channel region.

Fig. 4a illustrates the hysteresis obtained from both lateral devices on the armchair and zigzag directions. The drain to source voltage (UDS) was applied by the voltage sweep from 0 V to 4 V, then from 4 V to -4 V, and back to 0 V. It is noted that the GNR in the armchair direction shows more pronounced hysteresis response with symmetric behaviour in both sweeping directions. In contrast, no significant hysteresis response of GNR devices in the zigzag direction was observed. Also, the area obtained for lateral devices in the zigzag direction is less when compared to the armchair (See Fig. 4a insets). This dependence in the hysteresis response might arise from the semiconducting and metallic nature of the armchair and zigzag edges of graphene nanoribbons, respectively [4, 5, 9]. Moreover, the hysteresis might be either attributed to the charge trapping and de-trapping into the surface or interface traps of the GNR device or the charge transfer from the absorbents like water molecules [12, 15].

Fig. 4. (a) Hysteresis response of 20 nm GNR constriction in armchair direction (logarithmic scale) of epitaxial graphene, insets show the DC hysteresis response of GNR in zigzag direction (logarithmic scale) and hysteresis area obtained from lateral devices on both armchair and zigzag directions. (b) Hysteresis response of GNR in armchair direction with different strip widths, insets show corresponding hysteresis area obtained from the devices.

Furthermore, we have evaluated the hysteresis response dependence and the hysteresis factor on GNR strip width. Fig. 4b illustrates the dependence of the hysteresis response on the stripe width obtained from the GNRs in armchair direction for equal channel length. It is noted that with an increase in the strip width, we could observe a moderate increase of the hysteresis factor. This behaviour be attributed to an increase in the absolute value of traps with an increase in the surface

area of the channel [12, 15] when the trap density is assumed to be independent on the area. Moreover, due to the increase in the surface area, more additional terrace edges cover the channel region (See Fig. 2b), which further introduces more defect density in the channel [23]. These initial defect sites in the graphene channel promote the charge trapping process and may further influence the conductivity hysteresis of the GNR devices [23, 24].

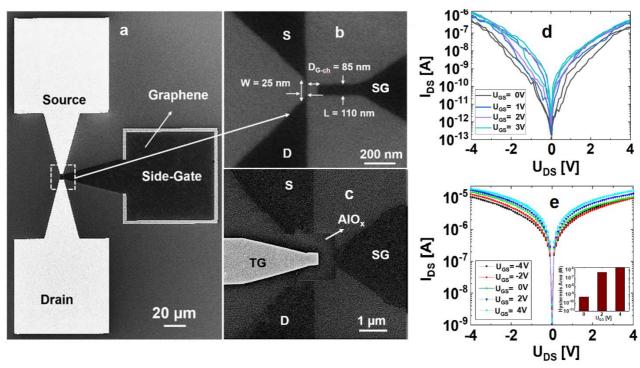

We further evaluated the hysteresis response of the GNR channel by modulating the carrier density using a side gate. Similar methods of side gate engineering of graphene channels for graphene field-effect devices have already been reported and studied [25, 26]. Therefore, side gates could be an alternative to the top-gating scheme in graphene field effect transistors (GFETs) to modulate the graphene channel using a lower number of lithographic steps. However, this device type often experiences high leakage current caused by the current flow through the dielectric/air interface [27]. Fig. 5a and 5b illustrate SEM images of the general structure of side-gated armchair based GNR-FET. In these devices, graphene is used for both channel and side-gate. To understand the hysteresis behavior in these devices, measured in direct sweep conditions, (Ups was varied from 0 V to 4 V, then from 4 V to -4 V and back to 0 V). The side gate voltage step was varied from 0 V up to 3 V with 1 V step.

Fig. 5. (a and b) SEM image of single device overview of armchair based side gate GNR-FET. (c) SEM image of top gated GNR-FET. (d and e) Double sweep logarithmic scale output curve of GNR-FET under side gate and top gate modulation. Insets shows the dependency of hysteresis area upon different side gate to source (U<sub>GS</sub>) voltage.

Typical output hysteresis response obtained from side gate GNR-FET is shown in Fig. 5d. The FET shows typical n-type behavior of graphene on SiC. In addition, it is noted that the U<sub>DS</sub> sweep in GNR-FETs exhibits an increase in the hysteresis factor with increasing positive gate voltage. A similar behavior in GFETs has already been studied [12, 15]. These hysteresis responses possibly originate from the charge injection into the channel and side gate graphene substrate interface [14, 15]. Therefore, with the substantial influence of the side-gate voltage sweep, the hysteresis is triggered by a redistribution of charges at the interface and further causes charge transfer or trapping. As a second source of the conductivity hysteresis adsorbates and processing residues may act. The effect of the side gate-source voltage sweeping range (U<sub>GS</sub>) and corresponding hysteresis area obtained from the GNR-FET is illustrated in Fig. 5e inset. Here, the U<sub>GS</sub> voltage varies from 0 V to 3 V. A small hysteresis response was observed for U<sub>GS</sub> at 0 V. However, a higher hysteresis response was observed when the U<sub>GS</sub> increased. This behavior infers that the trapping of charges has increased

during the increase of side gate electric field strength sweeps which further contribute to the wider hysteresis.

We further investigated the effect of top gate modulation by passivating graphene channel with a high -k dielectric layer like AlO<sub>x</sub>. The channel region is deposited with 20 nm of AlO<sub>x</sub>. Subsequently, the top gate electrodes were deposited. Fig. 5b illustrates a SEM image of the top gated GNR-FET with 20 nm AlO<sub>x</sub>. The devices were further measured with the side gate under ambient conditions. The U<sub>DS</sub> voltage varied from 0 V to 4 V, then from 4 V to -4 V and back to 0 V. After each direct sweep measurement, the top gate voltage U<sub>GS</sub> was increased by 2 V from -4 V to 4 V. Fig. 5e illustrates the hysteresis factor of the device under top gate modulation. It is noted that the current has been improved, and hysteresis response in the device was minimized with top gate modulation. This behavior further infers that deposition of a high-k dielectric material like AlO<sub>x</sub> in the active device area of the GNR-FET modifies and passivates the contribution of hysteresis promoting sources like water molecules and other adsorbents [14, 28]. Moreover, it desorbs molecules from the surface of the graphene channel and retards the chemical reaction reducing the H<sub>2</sub>O molecules at the interface of the channel [14, 29]. Another possible explanation for this behavior might be due to a limited supply of oxygen on the surface of the graphene channel, as it suppresses the surface reactions [28].

# **Summary**

In conclusion, we have fabricated and evaluated the hysteresis response of GNR devices in both armchair and zigzag directions of epitaxial graphene on semi-insulating 4H-SiC. The difference of the area underneath the upper and lower branches of the hysteresis curves was used to quantify hysteresis. In addition, the influence of the orientation of fabrication of GNR in both armchair and zig directions and its dimensions on the hysteresis effect was examined and studied. Minimal hysteresis response in devices oriented in zigzag direction, possibly due to the metallic nature of the GNRs with zigzag edges was found. Moreover, the significant increase in the hysteresis factor with increasing channel width was observed stemming from an increase in the absolute value of traps with an increased surface area. Furthermore, the increase in the gate electric field strength substantially increases the hysteresis factor of armchair oriented GNR-FET devices. Additionally, passivation of the active device area with  $AlO_x$  as a high-k dielectric material and top gate device operation could reduce the defects, resulting in a lower hysteresis factor and enhancing the devices' current.

### Acknowledgements

The authors acknowledge the financial support of this research by Carl Zeiss Foundation under contract P2018-01-002 and DAAD under grant 57435564.

#### References

- [1] K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, A. A. Firsov, Electric field effect in atomically thin carbon films, Science. 306 (2004) 666-669.

- [2] F. Schwierz, Graphene transistors, Nat. Nanotechnol. 5 (2010) 487-496.

- [3] X. Wang, Y. Ouyang, X. Li, H. Wang, J. Guo, H. Dai, Room-temperature all-semiconducting sub-10-nm graphene nanoribbon field-effect transistors, Phys. Rev. Lett. 100 (2008) 206803.

- [4] A. Kimouche, M. M. Ervasti, R. Drost, S. Halonen, A. Harju, P. M. Joensuu, J. Sainio, P. Liljeroth, Ultra-narrow metallic armchair graphene nanoribbons, Nat. Commun. 6 (2015) 10177.

- [5] Y.-W. Son, M. L. Cohen, S. G. Louie, Half-metallic graphene nanoribbons, Nature. 444 (2006) 347-349.

- [6] J. Liu, X. Feng, Synthetic Tailoring of graphene nanostructures with zigzag-edged topologies: Progress and perspectives, Angew. Chem. Int. Ed. 59 (2020) 23386-23401.

- [7] H. Wang, H. S. Wang, C. Ma, L. Chen, C. Jiang, C. Chen, X. Xie, A.-P. Li, X. Wang, Graphene nanoribbons for quantum electronics, Nat. Rev. Phys. 3 (2021) 791-802.

- [8] Z. Geng, B. Hähnlein, R. Granzner, M. Auge, A. A. Lebedev, V. Y. Davydov, M. Kittler, J. Pezoldt, F. Schwierz, Graphene nanoribbons for electronic devices, Ann. Phys. 529 (2017) 1700033.

- [9] Z. Chen, Y.-M. Lin, M. J. Rooks, P. Avouris, Graphene nano-ribbon electronics, Phys. E: Low-Dimens. Syst. Nanostructures. 40 (2007) 228-232.

- [10] M. Evaldsson, I. V. Zozoulenko, H. Xu, T. Heinzel, Edge-disorder-induced Anderson localization and conduction gap in graphene nanoribbons, Phys. Rev. B. 78 (2008) 161407.

- [11] F. Cervantes-Sodi, G. Csányi, S. Piscanec, A. C. Ferrari, Edge-functionalized and substitutionally doped graphene nanoribbons: Electronic and spin properties, Phys. Rev. B. 77 (2008) 165427.

- [12] A. Tries, N. Richter, Z. Chen, A. Narita, K. Mullen, H. I. Wang, M. Bonn, M. Klaui, Hysteresis in graphene nanoribbon field-effect devices, Phys. Chem. Phys. 22 (2020) 5667-5672.

- [13] Z. M. Liao, B. H. Han, Y. B. Zhou, D. P. Yu, Hysteresis reversion in graphene field-effect transistors, J. Chem. Phys. 133 (2010) 044703.

- [14] Y.-X. Lu, C.-T. Lin, M.-H. Tsai, K.-C. Lin, Review-Hysteresis in carbon nano-structure field effect transistor, Micromachines. 13 (2022) 509.

- [15] H. Wang, Y. Wu, C. Cong, J. Shang, T. Yu, Hysteresis of electronic transport in graphene transistors, ACS Nano. 4 (2010) 7221-7228.

- [16] I. Eliseyev, V. Y. Davydov, A. Smirnov, M. Nestoklon, P. Dementev, S. Lebedev, A. Lebedev, A. Zubov, S. Mathew, J. Pezoldt, Optical estimation of the carrier concentration and the value of strain in monolayer graphene grown on 4H-SiC, Semiconductors. 53 (2019)1904-1909.

- [17] R. Göckeritz, D. Schmidt, M. Beleites, G. Seifert, S. Krischok, M. Himmerlich, J. Pezoldt, High temperature graphene formation on capped and uncapped SiC, Mater. Sci. Forum. 679 (2011) 785-788.

- [18] B. Hähnlein, S. Lebedev, I. Eliseyev, A. Smirnov, V. Davydov, A. Zubov, A. Lebedev, J. Pezoldt, Investigation of epitaxial graphene via Raman spectroscopy: Origins of phonon mode asymmetries and line width deviations, Carbon. 170 (2020) 666-676.

- [19] S. Mathew, S. P. Lebedev, A. A. Lebedev, B. Hähnlein, J. Stauffenberg, K. Udas, H. O. Jacobs, E. Manske, J. Pezoldt, Nanoscale surface morphology modulation of graphene–i-SiC heterostructures, Mater. Today Proc. 53 (2022) 289-292.

- [20] J. Penuelas, A. Ouerghi, D. Lucot, C. David, J. Gierak, H. Estrade-Szwarckopf, C. Andreazza-Vignolle, Surface morphology and characterization of thin graphene films on SiC vicinal substrate, Phys. Rev. B. 79 (2009) 033408.

- [21] W. Norimatsu, M. Kusunoki, Formation process of graphene on SiC (0001), Phys. E: Low-Dimens. Syst. Nanostructures. 42 (4) (2010) 691-694.

- [22] H. Kuramochi, S. Odaka, K. Morita, S. Tanaka, H. Miyazaki, M. Lee, S.-L. Li, H. Hiura, K. Tsukagoshi, Role of atomic terraces and steps in the electron transport properties of epitaxial graphene grown on SiC, AIP Adv. 2 (2012) 012115.

- [23] J. Robinson, X. Weng, K. Trumbull, R. Cavalero, M. Wetherington, E. Frantz, M. LaBella, Z. Hughes, M. Fanton, D. Snyder, Nucleation of epitaxial graphene on SiC (0001), ACS Nano. 4 (2010) 153-158.

- [24] C. Cho, Y. Gon Lee, U. Jung, C. Goo Kang, S. Lim, H. Jun Hwang, H. Choi, B. Hun Lee, Correlation between the hysteresis and the initial defect density of graphene, Appl. Phys. Lett. 103 (2013) 083110.

- [25] B. Hähnlein, B. Händel, J. Pezoldt, H. Töpfer, R. Granzner, F. Schwierz, Side-gate graphene field-effect transistors with high transconductance, Appl. Phys. Lett. 101 (2012) 093504.

- [26] B. Hähnlein, B. Händel, F. Schwierz and J. Pezoldt, Properties of graphene side gate transistors, Mater. Sci. Forum. 740 (2013) 1028-103.

- [27] X. Li, X. Wu, M. Sprinkle, F. Ming, M. Ruan, Y. Hu, C. Berger, W. A. de Heer, Top-and side-gated epitaxial graphene field effect transistors, Phys. Status Solidi. 207 (2010) 286-290.

- [28] Y. G. Lee, C. G. Kang, C. Cho, Y. Kim, H. J. Hwang, B. H. Lee, Quantitative analysis of hysteretic reactions at the interface of graphene and SiO<sub>2</sub> using the short pulse I–V method, Carbon. 60 (2013) 453-460.

- [29] C. G. Kang, Y. G. Lee, S. K. Lee, E. Park, C. Cho, S. K. Lim, H. J. Hwang, B. H. Lee, Mechanism of the effects of low temperature Al<sub>2</sub>O<sub>3</sub> passivation on graphene field effect transistors, Carbon. 53 (2013) 182-187.