Revised: 2022-10-31 Accepted: 2022-11-25 © 2023 The Author(s). Published by Trans Tech Publications Ltd, Switzerland. Online: 2023-05-31

Submitted: 2022-09-02

# **Evolution of Interface State Density and Near Interface Oxide Traps** under Controlled Nitric Oxide Annealing in SiO<sub>2</sub>/SiC Lateral MOSFETs

P. Fiorenza<sup>1,a\*</sup>, M. Camalleri<sup>2,b</sup>, L. Scalia<sup>2,c</sup>, E. Zanetti<sup>2,d</sup>, M. Saggio<sup>2,e</sup>, F. Giannazzo<sup>1,f</sup>, F. Roccaforte<sup>1,g</sup>

<sup>1</sup>Consiglio Nazionale delle Ricerche – Istituto per la Microelettronica e Microsistemi (CNR-IMM), Strada Ottava 5, 95121 Catania, Italy

<sup>2</sup>STMicroelectronics, Stradale Primosole 50, 95121 Catania, Italy

apatrick.fiorenza@imm.cnr.it, bmarco.camalleri@st.com, claura.scalia@st.com, dedoardo.zanetti@st.com, emario.saggio@st.com, filippo.giannazzo@imm.cnr.it, gfabrizio.roccaforte@imm.cnr.it

Keywords: MOS interface; post oxide deposition nitridation; interface state density; field effect mobility; threshold voltage stability

**Abstract.** In this paper, the effect of different post oxide deposition nitridation processes in NO on n-channel lateral MOSFETs fabricated on implanted 4H-SiC were investigated. In particular, the electrical behavior of the MOSFETs was deeply investigated not only in terms of SiO<sub>2</sub>/SiC interface state density and field effect mobility, but also considering the threshold voltage stability effect. The aim of this work was to explore to which extent post oxide deposition annealing in NO is beneficial for the MOS interface behavior and when their detrimental effects start to become predominant on the device performances. Here, the separation of the trapping states at the interface – either close to the conduction and valence band edges – and the near interface oxide traps are reported for the different duration of the post oxide deposition annealing. In fact, cyclic gate bias stress was employed in order to analyze the behavior of the trapping states and to correlate them with the variation of the benefits in terms of the channel mobility (that saturates at about 80 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>), and on the threshold voltage instability effect. In particular, prolonged PDAs may induce an increase of the amount of trapping states close to the valence band edge and inside the insulator of about 10% and 50 %, respectively.

### Introduction

The conduction performances of 4H-SiC MOSFETs are strongly influenced by the processing of the SiO<sub>2</sub>/4H-SiC interface [1]. In particular, the on-resistance and the field effect channel mobility  $(\mu_{FE})$  [2,3] can be improved by post-oxidation- or post-deposition-annealing (PDAs) in nitric oxide (NO) [4]. However, while the mobility is improved, the introduction of nitrogen during PDA can generate trapping states at the SiO<sub>2</sub>/4H-SiC interface, which seems to introduce a detrimental impact on the threshold voltage (V<sub>th</sub>) stability [5,6]. In this context, it is mandatory to explore the evolution of the interface state density not only close to 4H-SiC conduction band (Dit), but also close to the valence band. Moreover, it is relevant also to monitor the near interface oxide traps (NIOTs) that might be generated under prolonged PDAs in NO. This approach will elucidate if any detrimental effect occurs under prolonged PDAs in NO.

#### **Experimental**

In this paper, different n-channel lateral MOSFETs were fabricated on 4°-off-axis n-type (0001) 4H- SiC epitaxial layers (1 × 10<sup>16</sup> cm<sup>-3</sup>) an aluminum (Al) implanted body region (N<sub>A</sub> ~  $10^{17}$ cm<sup>-3</sup>). The gate oxide was a 55 nm thick deposited SiO<sub>2</sub> layer. Different duration PDAs were performed in a horizontal furnace in a sub-atmospheric pressure regime at 1175 °C in NO [7] in order to investigate the electrical evolution of both Dit and NIOTs at the SiO<sub>2</sub>/4H-SiC system.

The MOSFETs were characterized acquiring the current voltage (I<sub>D</sub>-V<sub>G</sub>) transfer characteristics and capacitance–voltage (C-V) curves, in a CASCADE Microtech probe station equipped with a Keysight B1505A parameter analyzer.

#### **Results and Discussion**

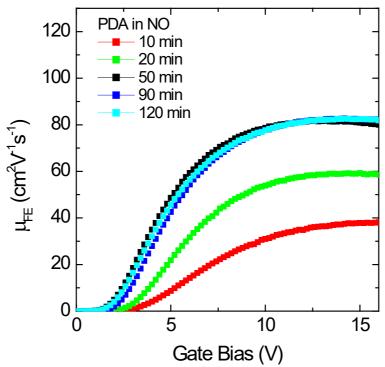

Fig. 1 shows the field effect mobility  $\mu_{FE}$  values measured on the MOSFETs subjected to PDAs in NO for 10, 20, 50, 90, and 120 min respectively. As can be noticed, the  $\mu_{FE}$  values increased with increasing the PDA duration, but after 50 min the  $\mu_{FE}$  values saturated (at about 80 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>). The peak mobility values are reported in Table I.

Fig.1: Field effect mobility values measured on 4H-SiC MOSFETs subjected to PDAs in NO of different duration.

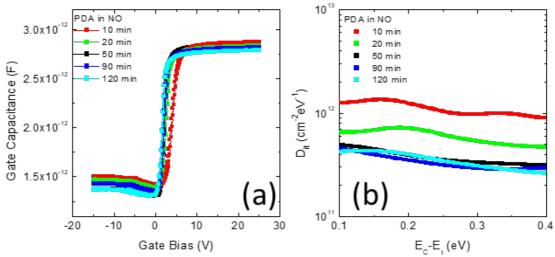

Fig.2a shows the C-V curves collected at 100 kHz from negative toward positive gate bias (V<sub>G</sub>) values and backwards (hysteresis not visible at a sweep rate of 0.1V/s). From the accumulation capacitance values measured in the positive V<sub>G</sub> range, no significant oxide thickness variation is observed for PDA with times longer than 20 min. Hence, in our experimental conditions, the NO annealing duration did not change the oxide thickness, thus indicating that only a limited substrate re-oxidation occurred (< 3 nm). However, as can be noticed in Fig.2a, the slope of the C-V curves increases with increasing the NO annealing duration. This behavior is confirmed by the D<sub>it</sub> profile – calculated by the Terman method that used the TCAD simulated curve as reference – shown in Fig. 2b, where the clear decrease of D<sub>it</sub> can be correlated to the NO annealing duration. Table I shows the D<sub>it</sub> data collected at 0.1 eV below the 4H-SiC conduction band, which decrease with increasing the NO annealing duration with a saturation at about  $4 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup>.

Fig.2: (a) C-V curves (with no Hysteresis) measured on the different MOSFETs subjected to different PDAs in NO. (b) D<sub>it</sub> values obtained on the different MOSFETs subjected to different PDAs in NO.

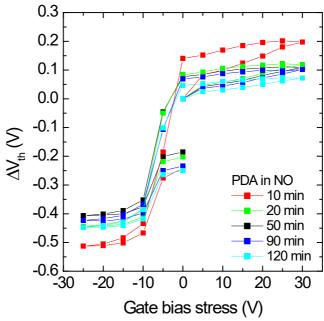

The eventual detrimental role of a prolonged NO annealing duration can be assessed by monitoring the V<sub>th</sub> stability (Fig.3). In fact, it has been observed that a prolonged exposure to oxidizing species (such as the NO) may increase the interfacial disorder correlated to the formation of substoichiometric oxide layer and/or the formation of carbon-related defects [7].

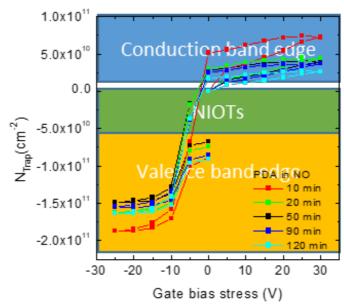

In our case, by applying the non-relaxing stressing method to study the MOSFET  $V_{th}$  stability described in Ref. [4], it was possible to separate the different trapping contributions, affecting the  $SiO_2/4H$ -SiC systems under investigation. The threshold voltage variation  $\Delta V_{th}$  (Fig.3) were converted into the amount of trapped charge ( $N_{Trap}$ ) at the conduction ( $E_C$ ) and valence ( $E_V$ ) band edges and in near interface oxide region (NIOTs) as shown in Fig.4. The relevant data reported in Fig.4 are also summarized in Table I.

Fig.3:  $\Delta V_{th}$  values obtained on the MOSFETs subjected to PDAs in NO of different duration.

Fig.4: N<sub>Trap</sub> values (calculated from data shown in Fig.3) obtained on the MOSFETs subjected to PDAs in NO of different duration.

| Table 1. Survey of the electrical data confected on the investigated MOSTETS. |                                                                    |                                                                        |                                                                        |                                                      |                                             |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------|

| Sample                                                                        | μ <sub>FE</sub> (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | D <sub>it</sub> (×10 <sup>11</sup> cm <sup>-2</sup> eV <sup>-1</sup> ) | N <sub>t</sub> at E <sub>C</sub> (×10 <sup>10</sup> cm <sup>-2</sup> ) | $N_t$ at $E_V$ (×10 <sup>11</sup> cm <sup>-2</sup> ) | NIOTs (×10 <sup>10</sup> cm <sup>-2</sup> ) |

| 10min NO                                                                      | 38.2                                                               | 12.48                                                                  | 7.22                                                                   | 1.88                                                 | 8.84                                        |

| 20min NO                                                                      | 59.2                                                               | 6.51                                                                   | 4.35                                                                   | 1.62                                                 | 7.40                                        |

| 50min NO                                                                      | 81.7                                                               | 4.21                                                                   | 3.98                                                                   | 1.49                                                 | 6.77                                        |

| 90min NO                                                                      | 82.7                                                               | 4.56                                                                   | 3.72                                                                   | 1.55                                                 | 8.55                                        |

| 120min NO                                                                     | 82.6                                                               | 4.21                                                                   | 2.63                                                                   | 1.64                                                 | 9.13                                        |

Table I: Survey of the electrical data collected on the investigated MOSFETs.

As can be noticed, the increase of the PDAs duration results an increase of the field effect mobility and a reduction of the  $D_{it}$ . However, the amount of traps close to the valence band edge has a non-monotonic behavior – first it decreases with increasing the PDAs duration (from 1.88 down to 1.49  $\times 10^{11}$  cm<sup>-2</sup>), then it increases again (up to  $1.64 \times 10^{11}$  cm<sup>-2</sup>). Similarly the NIOTs suffers a non-monotonic behavior by long PDAs duration (from  $8.88 \times 10^{10}$  cm<sup>-2</sup> down to  $6.77 \times 10^{10}$  cm<sup>-2</sup> then up to  $9.13 \times 10^{10}$  cm<sup>-2</sup>). By a cross-comparison of all the electrical data summarized in Table I, it is possible to conclude that prolonged NO PDAs may induce detrimental effects. In particular, despite the improved  $\mu_{FE}$  and  $D_{it}$  values, the amount of trapping states close to the valence band edge and inside the insulator are increased of about 10% and 50 %, respectively. Those increased trapping states increased the  $V_{th}$  instability for the prolonged NO PDAs devices.

## **Summary**

In this paper, n-channel lateral MOSFETs fabricated on implanted 4H-SiC were investigated after PDAs in NO of different duration, by means of cyclic gate bias stress in order to analyze the behavior of the trapping states at the edges of the conduction and valence band of the semiconductor and in the near-interface region of the insulator. Alongside the benefits in terms of the channel mobility (that saturates at about 80 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>), a detrimental effect of a prolonged PDAs was observed. In particular, prolonged PDAs may induce an increase of the amount of trapping states close to the valence band edge and inside the insulator of about 10% and 50 %, respectively. Hence, a fine control of the NO PDA is required to improve the MOSFET interfacial transport and mitigating the threshold voltage instability.

#### References

- [1] F. Roccaforte, P. Fiorenza, G. Greco, R. Lo Nigro, F. Giannazzo, F. Iucolano, M. Saggio, Microel. Eng. 187, 66 (2018)

- [2] M. Cabello, V. Soler, G. Rius, J. Montserrat, J. Rebollo, P. Godignon Mater. Sci. Semicon. Proc. 78, 22 (2018).

- [3] P. Fiorenza, F. Giannazzo, A. Frazzetto, F. Roccaforte, J. Appl. Phys. 112, 084501 (2012).

- [4] P. Fiorenza, F. Giannazzo, S. Cascino, M. Saggio, F. Roccaforte. Appl. Phys. Lett. 117, 103502 (2020)

- [5] H. Yano, N. Kanafuji, A. Osawa, T. Hatayama, T. Fuyuki, IEEE Trans. Electron Dev. 62, 324 (2015)

- [6] A.J. Lelis, R. Green, D.B. Habersat, M. El, IEEE Trans. Electron Dev. 62, 316 (2015)

- [7] P. Fiorenza, C. Bongiorno, F. Giannazzo, M. S. Alessandrino, A. Messina, M. Saggio, F. Roccaforte; Appl. Surf. Sci. 557 149752 (2021)