doi:10.4028/p-k93y93

© 2023 The Author(s). Published by Trans Tech Publications Ltd, Switzerland.

# Oxide and Interface Defect Analysis of Lateral 4H-SiC MOSFETs Through CV Characterization and TCAD Simulations

Submitted: 2022-09-02

Revised: 2022-11-28 Accepted: 2022-11-29

Online: 2023-05-31

A. Vasilev<sup>1,a\*</sup>, M. W. Feil<sup>2,5,b</sup>, C. Schleich<sup>1,c</sup>, B. Stampfer<sup>1,d</sup>, G. Rzepa<sup>4,e</sup>, G. Pobegen<sup>3,f</sup>, T. Grasser<sup>2,j</sup>, and M. Waltl<sup>1,h\*</sup>

<sup>1</sup>Christian Doppler Laboratory for Single Defect Spectroscopy at the Institute for Microelectronics, TU Wien, Austria

<sup>2</sup>Institute for Microelectronics, TU Wien, Austria

<sup>3</sup>KAI GmbH, Villach, Austria

<sup>4</sup>Global TCAD Solutions GmbH, Vienna, Austria

<sup>5</sup>Infineon Technologies AG, Neubiberg, Germany

<sup>a</sup>vasilev@iue.tuwien.ac.at, <sup>b</sup>Maximilian.Feil@infineon.com, <sup>c</sup>schleich@iue.tuwien.ac.at, <sup>d</sup>stampfer@iue.tuwien.ac.at, <sup>e</sup>g.rzepa@globaltcad.com, <sup>f</sup>gregor.pobegen@k-ai.at, <sup>j</sup>grasser@iue.tuwien.ac.at, <sup>h</sup>waltl@iue.tuwien.ac.at

**Keywords:** Hysteresis, 4H-SiC, TCAD Modeling, MOSFETs, Non-Radiative Multi-Phonon Model, Border Traps, Interface Traps

Abstract. We investigated oxide and interface defects of lateral 4H-SiC MOSFETs through capacitance-voltage (C-V) and conductance-voltage (G-V) characterization at various frequencies and temperatures. By employing consecutive up and down sweeps of the gate voltage at three different temperatures, we experimentally characterized the hysteresis width as the difference between up and down sweeps in the depletion to accumulation (d-a) and depletion to inversion (d-i) regions. We observed an increase in the hysteresis width with decreasing temperature. Although the hysteresis width is not affected by the small-signal frequency, at the same time, increasing the frequency leads to a strong stretch-out effect, especially in the d-i region. Our measurement results indicate that the hysteresis deformation of the C-V curves is dominated by three different trap types. First, interface acceptor-like defects located close to the conduction band can follow the small-signal frequency. Slower acceptor-like border traps with trap levels both close to the conduction band and in the middle of the band gap are however responsible for the increase of trapped negative charge with increasing gate voltage. Finally, we assume the presence of a fixed positive charge.

#### Introduction

4H-SiC MOSFETs are a promising technology for high power electronics [1]. However, silicon dioxide (SiO<sub>2</sub>) on a Si-face SiC surface still remains a major research topic due to the high defect density compared to the SiO<sub>2</sub>/Si interface [2–13]. This is of particular concern because electrically active border and interface defects can not only affect the reliability of the device itself but also the operation of the application circuit [14]. Understanding the origin and influence of these different types of defects will help to reduce the defect density and increase device reliability. In this context, technology computer aided design (TCAD) can be a powerful tool to analyze the data from characterization measurements. Recently, some researchers have evaluated the influence of the interface traps on capacitance-voltage (C-V) curves by using Shockley-Read-Hall (SRH) theory [15–19]. In [15], the trapping behavior of interface and near-interface traps was simulated for MOS capacitors by employing SRH, trap-assisted tunneling and Frenkel-Poole models. The authors implemented both deep and shallow oxide traps to describe the hysteresis and the flat-band voltage shift increase with temperature. Furthermore, Marescra *et al.* [17] have not only shown that fixed positive charge influences the C-V curve, they also investigated the impact of variations in the capture cross section on the hysteresis effect. It was demonstrated that traps close to the valence or conduction bands are fast, while those close

to the mid bandgap are slow. Despite all these efforts to improve the understanding of C-V measurements in SiC devices, a complete simulation of a lateral 4H-SiC MOSFET calibrated and validated with measurement data at different small-signal frequencies and temperatures has not been performed yet.

In this work, we present such a TCAD [20] model including Shockley-Read-Hall (SRH) theory and the non-radiative multi-phonon (NMP) theory [21] for the description of charge transfer reactions associated with defects at the interface and in the oxide, respectively. The resulting model has been calibrated with C-V curves from impedance measurements at different temperatures and frequencies.

## **Devices and Experiment**

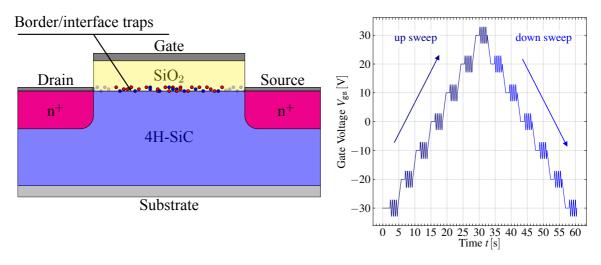

We used lateral 4H-SiC nMOSFETs with a  $n^+$  poly silicon gate. We assume an oxide thickness of  $68\,\mathrm{nm}$  and a gate length of  $7.5\,\mu\mathrm{m}$ , see Fig.1, left. This oxide layer was formed on the Si-face substrate by chemical vapor deposition. For C-V and conductance-voltage (G-V) curve measurements, the small-signal method was used. For equivalent circuit capacitance and conductance were connected in parallel mode. Both the sinusoidal small-signal for each bias step and the gate voltage up and down sweeps were implemented for investigating the trapping dynamics, see Fig. 1, right [17,24]. The gate voltage  $V_{gs}$  is swept up and down within the range of  $-30\,\mathrm{V}$  to  $30\,\mathrm{V}$  at a sweep rate of  $2.0\,\mathrm{V}\,\mathrm{s}^{-1}$ , see Fig. 1, right. The amplitude of the small-signal was  $50\,\mathrm{mV}$  with a frequency between  $4\,\mathrm{kHz}$  and  $1024\,\mathrm{kHz}$ . The time step for each gate bias was  $0.13\,\mathrm{s}$  and the delay between up and down sweep was  $12\,\mathrm{ms}$ . The hysteresis width was extracted for operating temperatures of  $300\,\mathrm{K}$ ,  $373\,\mathrm{K}$ , and  $448\,\mathrm{K}$ .

Fig. 1: Left: The used lateral 4H-SiC transistor. The possible defects leading to the distortion of the C-V curves are shown. Right: Schematic of the applied gate voltage during the impedance measurement. Both the small-signal and the gate voltage sweep are used in the transient analysis to investigate traps dynamics.

## **Measurement Results**

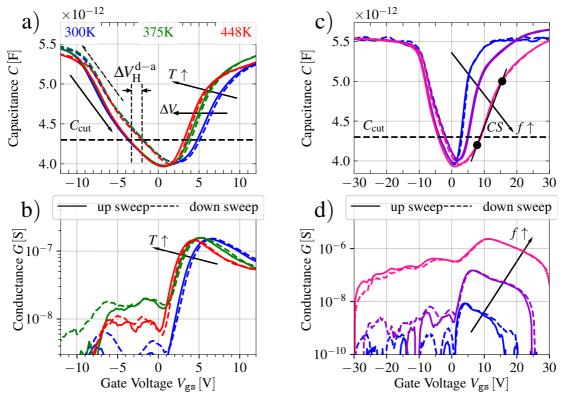

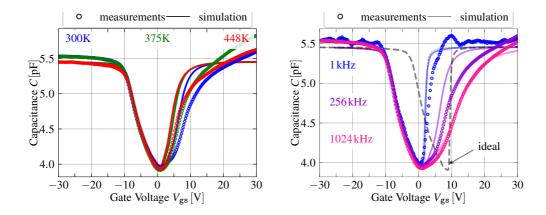

Fig. 2 shows C-V and G-V curves measured at various temperatures and frequencies. The measured impedance has been corrected for parasitic impedances [6]. The horizontal line indicates the reference capacitance ( $C_{\rm cut}=4.3\times10^{-12}\,{\rm F}$ ) at which we define the hysteresis widths  $\Delta V_{\rm H}^{\rm d-a}$  and  $\Delta V_{\rm H}^{\rm d-i}$  between the up and down sweeps respectively. One can see in Fig. 2a the C-V curves are shifted by  $\Delta V$  towards lower  $V_{\rm gs}$  with increasing temperatures. The peak of conductance shifts towards lower gate voltage by 3 V with increasing temperature, see Fig. 2b, and the hysteresis width in the depletion to accumulation region  $\Delta V_{\rm H}^{\rm d-a}$  is wider than in the depletion to inversion region  $\Delta V_{\rm H}^{\rm d-i}$ , whereby they slightly decrease with increasing temperature. We attribute this behavior to slow and border traps which are located within a few nanometers away from the SiC/SiO<sub>2</sub> interface [22, 23], see Fig.2, left. Fig.2c shows that the C-V curves are shifted towards higher  $V_{\rm gs}$  when the frequency

is increasing. A frequency-dependent peak in the conductance around 2–8 V indicates the presence of interface states, see Fig.2d. Two reference capacitances are used for extracting the capacitance swing  $(CS = \partial V_{\rm gs}/\partial C)$ .

Fig. 2: a) C-V characteristics and b) conductance of a lateral 4H-SiC MOSFET at  $64\,\mathrm{kHz}$  and  $300\,\mathrm{K}$ ,  $373\,\mathrm{K}$ , and  $448\,\mathrm{K}$ . c) C-V characteristics and d) conductance of a lateral 4H-SiC MOSFET at  $300\,\mathrm{K}$  and frequency  $4\,\mathrm{kHz}$ ,  $64\,\mathrm{kHz}$ , and  $1024\,\mathrm{kHz}$ . The horizontal line indicates the reference capacitance ( $C_\mathrm{cut} = 4.3 \times 10^{-12}\,\mathrm{F}$ ) at which we define the hysteresis widths  $\Delta V_\mathrm{H}^\mathrm{d-a}$  and  $\Delta V_\mathrm{H}^\mathrm{d-i}$  between the up and down sweeps respectively. Two reference capacitances are used for extracting the capacitance swing (CS).

#### The Modeling Framework

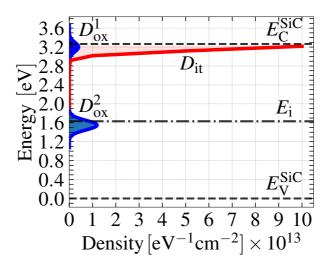

To explain the C-V curves at various frequencies from Fig.2a,c we used an exponential distribution of fast acceptor-like interface defects located close to the conduction band (see Fig. 3) [15–19]. Due to their small capture  $(\tau_c)$  and emission  $(\tau_e)$  time constants over a large bias range, charge trapping and detrapping can follow the small-signal modulation. The interface traps that capture electrons become electrically active and are directly integrated with the mobility degradation model. In a simplified way the effective mobility is proportional to  $\mu_{\rm C} \propto \mu_0 \, [(T/300\,{\rm K})^{\alpha}/(D_{\rm it}/10^{11}\,{\rm cm}^{-2})]$ , where  $\mu_{\rm C}$  is the Coulomb component of mobility model. By fitting the measured and simulated curves we extract these parameters, which can reproduce the measured C-V curves with high accuracy. In our work we used  $\mu_0 = 18 \,\mathrm{cm}^2 \,\mathrm{V}^{-1} \,\mathrm{s}^{-1}$ ,  $\alpha = -9.2$ , and  $D_{\mathrm{it}}(T)$  is the temperature-dependent interface charge density [20]. The capture cross section for electrons and holes was  $\sigma = 10^{-15} \, \mathrm{cm}^{-2}$  [20]. Our measurements show a negligible influence of donor-like traps which are located close to the valence band and which are hence not considered in the simulation, see Fig.2. Furthermore, we introduced a Gaussian distribution of slower acceptor-like border traps  $D_{ox}^2$  close to the SiO<sub>2</sub>/SiC interface, which turned out to be located around the middle of the 4H-SiC band gap. We further calculated the capture and emission times of the involved border traps by using the NMP model [21]. In this model, the asymmetry of barriers for the forward and backward processes leads to differences in charge capture and emission times. These barriers are determined by the relaxation energy  $S=4.0\pm0.1\,\mathrm{eV}$  and the parabolic curvature ratio  $R=2.0\pm0.1$ . The bias dependent asymmetry of capture and emission times influences the hysteresis width from the depletion to the accumulation region. Also, we assume a second Gaussian distribution of slow acceptor-like border traps  $D_{\rm ox}^1$  with a lower concentration which is energetically located close to the 4H-SiC conduction band. The relaxation energy of  $D_{\rm ox}^1$  is  $S=0.1\pm0.01$  eV, and the parabolic curvature ratio is  $R=1.0\pm0.01$ . These defects affect the hysteresis width of the depletion to the inversion region [25]. The high concentration of acceptor-like traps results in a severe positive voltage shift towards higher  $V_{\rm gs}$ . Hence, we introduced fixed positive traps  $N_{\rm it}^{\rm fix}$  to compensate for such a large  $\Delta V$  shift. The parameters for the models are summarized in Table 1. The effective gate voltage shift for the up and down sweeps was calculated by using Eq. 1.

$$V_{\text{eff}}(f, SR, T) = V_{\text{ideal}}(T) + \Delta V_{\text{it}}(f, T) + \Delta V_{\text{ox}}^{1}(SR, T) + \Delta V_{\text{ox}}^{2}(SR, T) + \Delta V_{\text{fix}}(T)$$

(1)

Where  $V_{\rm ideal}$  is the ideal C-V curve without any defects,  $\Delta V_{\rm it}$  is a shift caused by the interface traps,  $\Delta V_{\rm ox}^1$  is shift caused by slow traps which are located close to the conduction band and depending on sweep rate (SR) and temperature,  $\Delta V_{\rm ox}^2$  is shift caused by slow traps which are located close to mid gap and  $V_{\rm fix}$  is fixed positive traps.

Table 1: Parameters for Traps.

Fig. 3: The DOS for the  $D_{\rm it}$  (red),  $D_{\rm ox}^1$  and  $D_{\rm ox}^2$  (blue).

#### **Results and Discussions**

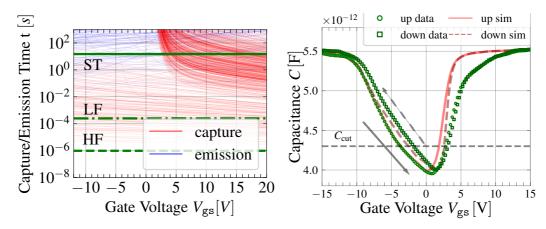

Based on our measurement results and the modeling framework we investigated the behavior of the C-V curves at various temperatures and frequencies. Fig.4, right shows the comparison of the hysteresis width between measured and simulated C-V at  $4\,\mathrm{kHz}$  and  $300\,\mathrm{K}$ . By increasing the gate voltage we scan the 4H-SiC band gap and see how traps with different energies influence the C-V curve.

Fig. 4: Left: Simulated capture (red) and emission (blue) times of  $D_{\rm ox}^2$ . The HF and LF lines refer to high and low frequency respectively, and ST is the sweep time. Right: Comparison of the hysteresis width with measured (green) and simulated C-V (red) at  $4\,\rm kHz$  and  $300\,\rm K$ .

Depending on their energy position relative to the Fermi level traps capture electrons and store them at different gate biases, thus two different hysteresis widths at the d-i and d-a regions occurred. In detail, the time evaluation of the slow acceptor-like traps  $D_{ox}^2$  indicates that by increasing the gate voltage, the emission times become longer than the capture times and partly even exceed the sweep time (ST), which means that some of the defects keep their charge state during the entire bias sweep, see at Fig. 4, left. Therefore, these slow defects appear to be responsible for the hysteresis width  $\Delta V_{\rm H}^{\rm d-a}$ . Nevertheless, an increasing temperature decreases the hysteresis width, and  $\Delta V_{\rm H}$  from depletion to accumulation (d-a) is 10 times higher than from depletion to inversion (d-i). However, in case the emission time remains higher than the ST, we do not observe a strong temperature dependence of  $\Delta V_{\rm H}^{\rm d-i}$ . This is because the down sweep time is enough to release electrons due to their fast time constants. Otherwise, at low temperature, during the up voltage sweep electrons are captured due to the emission time being larger than the capture time  $\tau_{\rm e} \geq \tau_{\rm c}$ , and traps become negatively charged. As a result,  $\Delta V$  is shifted towards positive gate voltages, see Fig. 2a. When the gate voltage sweeps down, electrons tend to be emitted back to the channel but due to the large emission time distribution, some of the traps keep their charge state. The high temperature reduces both capture and emission times, thus, most of the traps become neutralized, and both the  $\Delta V_{\rm H}^{\rm d-a}$  and the  $\Delta V_{\rm H}^{\rm d-i}$  are small, see Fig. 2a. In contrast to the slow border traps, the fast interface traps have  $\tau_{\rm c}$  ( $\tau_{\rm c}=10^{-10}$ – $10^{-13}\,{\rm s}$ ) even below  $1/f_{\rm HF}$  (high frequency, HF), see Fig. 4, left, thus they can follow the small-signal frequency.

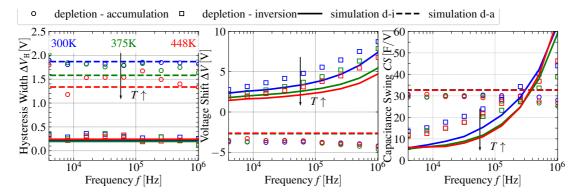

Fig. 5: Left: Measured and simulated C-V curves at  $256\,\mathrm{kHz}$  and  $T=300\,\mathrm{K}$ ,  $373\,\mathrm{K}$ , and  $448\,\mathrm{K}$ . Right: Measured and simulated C-V at  $300\,\mathrm{K}$  and frequencies of  $f=1\,\mathrm{kHz}$ ,  $256\,\mathrm{kHz}$ , and  $1024\,\mathrm{kHz}$ , compared to the ideal (defect-free) curve (black dashed lines).

Fig. 5 shows a comparison between measurements and simulation results. The difference in the capacitance values in the strong inversion regime at high frequencies indicates a residual parasitic impedance. The voltage shift  $\Delta V$  strongly depends on temperature and frequency, especially from depletion to the inversion region, see Fig. 5, left. With the increasing temperature, the capture and emission rates increase as well (or at the same time  $\tau_{\rm e} < \tau_{\rm c}$ ) which leads to defect neutralization and thus a decreasing voltage shift. The frequency dependence of C-V curve distortion indicates interface traps. Fig. 5, right shows that the fixed positive defects deviate the C-V measurement from ideal, and shift it towards lower gate voltages by 6 V at all frequencies ( $\Delta V_{\rm fix}$ ). At the same time, the shape of the ideal C-V curve is close to the measurement at low frequency and is not affected by sweep rates and higher frequencies. The fast interface traps  $D_{\rm it}$  can follow the small-signal frequency due to capture time being smaller than emission time.

Fig. 6: Left: The hysteresis width at measured (circles and squares) and simulated C-V (solid and dashed lines). Middle: The voltage shift at  $C_{\rm cut}$  at measured and simulated C-V. Right: The capacitance swing at  $C_{\rm cut}$  at measured and simulated C-V.

Therefore, a lot of interface traps are charged and we observed the distortion at C-V curves under high frequency, see Fig.5, right. In addition, Fig. 6 depicts the extracted measured and simulated dependencies of the hysteresis widths, voltage shifts, and capacitance swings. The strong frequency and temperature dependence from depletion to inversion confirms the presence of interface defects, see Fig. 6, middle, right. The hysteresis width in the depletion to inversion region is narrow due to low trap concentration  $D_{\text{ox}}^1$ .

#### **Summary**

In this work, we have presented a physical-based modeling approach to calculate the temperature activation of the hysteresis width and voltage shift of C-V curves of lateral 4H-SiC MOSFETs. We show that these behaviors are due to the charging and discharging kinetics of slow border traps in the oxide. The hysteresis widths of depletion to accumulation and from depletion to inversion region are caused by an asymmetry of the capture and emission times. These widths depend on temperature and sweep parameters but do not depend on the frequencies. In addition to slow border traps, the fast interface traps are responsible for the distortion of the C-V curves at various frequencies. Although the distribution of defect states is probably more complex than the used distribution in our simulation, our approach can explain the charge trapping dynamics and the general behavior of lateral 4H-SiC MOSFETs.

## Acknowledgement

The financial support by the Austrian Federal Ministry for Digital and Economic Affairs, the National Foundation for Research, Technology and Development and the Christian Doppler Research Association is gratefully acknowledged.

### References

- [1] B. J. Baliga, "Trends in Power Semiconductor Devices", *IEEE Transactions on Electron Devices*, Vol. 43, no. 10, p. 1717–1731 (1996)

- [2] R. Singh, "Reliability and performance limitations in SiC power devices", *Microelectronics Reliability*, Vol. 46, no. 5-6, p. 713–730 (2006)

- [3] C. Yang, Z. Gu, Z. Yin, F. Qin and D. Wang, "Interfacial traps and mobile ions induced flatband voltage instability in 4H-SiC MOS capacitors under bias temperature stress", *Journal of Physics D: Applied Physics*, Vol. 52, no. 40, p. 405103 (2019)

- [4] E. X. Zhang, C. X. Zhang, D. M. Fleetwood, R. D. Schrimpf, S. Dhar, S.-H. Ryu, X. Shen, and S. T. Pantelides, "Bias-Temperature Instabilities in 4H-SiC Metal-Oxide-Semiconductor Capacitors", *IEEE Transactions on Device and Materials Reliability*, Vol. 12, no. 2, p. 391-398 (2012)

- [5] Q. J. Sun, Y. M. Zhang, Q. W. Song, X. Y. Tang, Y. M. Zhang, C. Z. Li, and Y. M Zhang, "Near-interface oxide traps in 4H–SiC MOS structures fabricated with and without annealing in NO", *Chinese Physics B*, Vol. 26, no. 12, p. 127701 (2017)

- [6] H. Yoshioka, T. Nakamura, and T. Kimoto, "Accurate evaluation of interface state density in SiC metal-oxide-semiconductor structures using surface potential based on depletion capacitance", *Journal of Applied Physics*, Vol. 111, no. 1, p. 014502 (2012)

- [7] A. Chanthaphan, T. Hosoi, S. Mitani, Y. Nakano, T. Nakamura, T. Shimura, and H. Watanabe, "Investigation of unusual mobile ion effects in thermally grown SiO<sub>2</sub> on 4H-SiC(0001) at high temperatures", *Applied Physics Letters*, Vol. 100, p. 252103 (2012)

- [8] H. A. Moghadam, S. Dimitrijev, J. Han, and D. Haasmann, "Active defects in MOS devices on 4H-SiC: A critical review", *Microelectronics Reliability*, Vol. 60, p. 1-9 (2016)

- [9] R. Arora, J. Rozen, D. M. Fleetwood, K. F. Galloway, C. X. Zhang, J. Han, S. Dimitrijev, F. Kong, L. C. Feldman, S. T. Pantelides, and R. D. Schrimpf, "Charge Trapping Properties of 3C- and 4H-SiC MOS Capacitors With Nitrided Gate Oxides", *IEEE Transactions on Nuclear Science*, Vol. 56, no. 6, p. 3185-3191 (2009)

- [10] Y. Fujino, and K, Kita, "Estimation of near-interface oxide trap density at SiO<sub>2</sub>/SiC metal-oxide-semiconductor interfaces by transient capacitance measurements at various temperatures", *Journal of Applied Physics*, Vol. 120, no. 8, p. 085710 (2016)

- [11] X.-M. Chen, B.-B. Shi, X. Li, H.-Y. Fan, C.-Z. Li, X.-C. Deng, H.-H. Luo, Y.-D. Wu, and B. Zhang, "Characteristics and mechanisms of subthreshold voltage hysteresis in 4H-SiC MOS-FETs", *Chinese Physical Society and IOP Publishing*, Vol. 30, no. 4, p. 048504 (2021)

- [12] P. Fiorenza, F. Iucolano, M. Saggio, and F. Roccaforte, "Oxide Traps Probed by Transient Capacitance Measurements on Lateral SiO<sub>2</sub>/4H-SiC MOSFETs", *Materials Science Forum*, Vol. 924, p. 285-288 (2018)

- [13] G. Y. Chung, C. C. Tin, J. H. Won, J. R. Williams, K. McDonald, R. A. Weller, and L. C. Feldman, "Interface state densities near the conduction band edge in n-type 4H-and 6H-SiC", *IEEE Aerospace Conference*, Vol. 5, p. 409-413 (2000)

- [14] D. Peters, T. Aichinger, T. Basler, G. Rescher, K. Puschkarsky, H. Reisinger, "Investigation of threshold voltage stability of SiC MOSFETs", 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 40–43 (2018)

- [15] Y. J. He, X. Y. Tang, Y. F. Jia, C. Q. Zhou, and Y. M. Zhang, "Temperature-dependent effect of near-interface traps on SiC MOS capacitance", *Chinese Physics Letters*, Vol. 35, no. 10, p. 107301 (2018)

- [16] I. Matacena, L. Maresca, M. Riccio, A. Irace, G. Breglio, and S. Daliento, "SiC MOSFET C-V Curves Analysis with Floating Drain Configuration", *Materials Science Forum*, Vol. 1062, p. 663-668 (2022)

- [17] L. Maresca, I. Matacena, M. Riccio, A. Irace, G. Breglio, and S. Daliento, "Influence of the SiC/SiO<sub>2</sub> SiC MOSFET interface traps distribution on C–V measurements evaluated by TCAD simulations", *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Vol. 9, no. 2, p. 2171-2179 (2021)

- [18] Y. Cai, H. Xu, P. Sun, Z. Zhao and Z. Chen, "Influence of the Interface Traps Distribution on IV and CV Characteristics of SiC MOSFET Evaluated by TCAD Simulations", *IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia)*, p. 398-402 (2021)

- [19] L. Maresca, I. Matacena, M. Riccio, A. Irace, G. Breglio, and S. Daliento, "TCAD model calibration for the SiC/SiO<sub>2</sub> interface trap distribution of a planar SiC MOSFET", *IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia)*, p. 1-5 (2020)

- [20] https://www.globaltcad.com/. Accessed on: August 24 (2022)

- [21] T. Grasser, "Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities", *Microelectronics Reliability*, Vol. 52, no. 1, p. 39–70 (2012)

- [22] C. Schleich, J. Berens, G. Rzepa, G. Pobegen, G. Rescher, S. Tyaginov, T. Grasser, M. Waltl, "Physical Modeling of Bias Temperature Instabilities in SiC MOSFETs", *2019 IEEE International Electron Devices Meeting (IEDM)*, p. 20.5.1–20.5.4 (2019)

- [23] S. E. Tyaginov, M. Jech, G. Rzepa, A. Grill, A.-M. El-Sayed, G. Pobegen, A. Makarov, T. Grasser, "Border Trap Based Modeling of SiC Transistor Transfer Characteristics", 2018 International Integrated Reliability Workshop (IIRW), Oct. 2018, pp. 1–5 (2018)

- [24] K. Fukuda, J. Hattori, H. Asai, M. Shimizu, and T. Hashizume, "Simulation of GaN MOS capacitance with frequency dispersion and hysteresis", *International Conference on Simulation of Semiconductor Processes and Devices (SISPAD)*, p. 233-236 (2017)

- [25] N. Shiono and C. Hashimoto, "Threshold-Voltage Instability of n-Channel MOSFET's under Bias-Temperature Aging", *IEEE Transactions on Electron Devices*, Vol. 29, no. 3, p. 361-368 (1982)