# High Mobility Silicon Dioxide Layers on 4H-SiC Deposited by Means of Atomic Layer Deposition

Submitted: 2022-09-05

Revised: 2022-12-05

Online: 2023-05-31

Accepted: 2022-12-06

A.B. Renz<sup>1,a</sup>, Q. Cao<sup>1,b</sup>, O.J. Vavasour<sup>1,c</sup>, J. Gott<sup>2,d</sup>, P.M. Gammon<sup>1,e</sup>, T. Dai<sup>1,f</sup>, G.W.C. Baker<sup>1,g</sup>, P.A. Mawby<sup>1,h</sup> and V.A. Shah<sup>1,i</sup>

<sup>1</sup>School of Engineering, University of Warwick, Coventry, UK

<sup>2</sup>Warwick Manufacturing Group (WMG), University of Warwick, Coventry, UK

<sup>a</sup>Arne.Renz@warwick.ac.uk, <sup>b</sup>q.cao.2@warwick.ac.uk, <sup>c</sup>o.vavasour.1@warwick.ac.uk, <sup>d</sup>j.gott@warwick.ac.uk, <sup>e</sup>p.m.gammon@warwick.ac.uk, <sup>f</sup>T.Dai@warwick.ac.uk, <sup>g</sup>Guy.Baker@warwick.ac.uk, <sup>h</sup>P.A.Mawby@warwick.ac.uk, ivishal.shah@warwick.ac.uk

**Keywords:** 4H-SiC, silicon dioxide, SiO<sub>2</sub>/SiC interface, atomic layer deposition, channel mobility, lateral MOSFET, reliability, TDDB

**Abstract.** A study on the impact of different growth and deposition techniques on the reliability of silicon dioxide (SiO<sub>2</sub>) layers on silicon carbide (SiC) metal-oxide-semiconductor capacitors (MOSCAPs) is presented and compared to channel mobilities that were extracted from lateral metal-oxide-semiconductor field-effect transistors (LMOSFETs). Oxide layers were formed using atomic layer deposition (ALD), low pressure chemical vapour deposition (LPCVD) and direct thermal growth, including post-deposition anneals (PDAs) in nitrious oxide and forming gas (FG) for the ALD- and LPCVD-deposited oxides. Electrical characterisation results at elevated temperatures show that a PDA in FG leads to the highest average breakdown electric field of 10.08 MV/cm, outperforming all other device splits. Time-dependent dielectric breakdown (TDDB) results showed that the time to failure of 63% of the investigated samples at 9MV/cm in the FG-annealed samples was about 50% higher than in LPCVD-deposited oxides that had undergone an N<sub>2</sub>O PDA. Channel mobilities of the FG-treated samples averaged about three to four times higher than in other datasets, showing excellent peak field-effect mobilities of 60 cm<sup>2</sup>/V.s and 108 cm<sup>2</sup>/V.s at room temperature and 175°C, respectively.

#### Introduction

The successful implementation of silicon carbide into commercial power electronics conversion stages is in no small part due to its readily available native oxide, silicon dioxide (SiO<sub>2</sub>). This can be thermally grown with reasonable interface quality at temperatures between 1200°C-1400°C [1], making SiO<sub>2</sub> the ubiquitous gate oxide in any commercially available SiC metal-oxide-semiconductor field effect transistor (MOSFET).

However, interface defect densities are much more prevalent in SiC/SiO<sub>2</sub> systems than in their Si/SiO<sub>2</sub> metal-oxide-semiconductor (MOS) counterparts [2], and most of these defects originate from the thermal oxidation process, which ends up forming carbon-rich interfaces containing carbon clusters, hydrogen (H) and oxygen (O) vacancies. These defects enhance scattering, increase leakage currents and hence reduce channel mobilities in MOSFETs. This is a major technological issue, leading to specific on-resistances (Ron,sp) that are much higher than their theoretical limits, hampering the further uptake of SiC MOS technology.

Unlike with thermal oxidation, deposition techniques such as atomic layer deposition (ALD) or low-pressure chemical vapour deposition (LPCVD) offer a lower deposition temperature, excellent thickness control and suitability for conformal deposition of gate oxides in trench power device structures. They also do not consume any of the SiC material, meaning that the interface is less likely to be carbon-rich after deposition [3]. However, the electrical properties of as-deposited SiO<sub>2</sub> layers are poor [3, 4], and, after their deposition on SiC, a post-deposition anneal (PDA) typically follows in a nitrogen-containing ambient, such as nitric (NO) or nitrous oxide (N<sub>2</sub>O) at temperatures above 1,100°C [5]. In this work, we present the improvement brought about by deploying ALD-deposited

SiO2 layers which were post-deposition annealed in forming gas (FG) and N<sub>2</sub>O ambient. This is analysed by observing time-dependent dielectric breakdown (TDDB), capacitance-voltage (C-V), current-voltage (I-V) and channel mobility results.

## **Experimental**

Devices were fabricated on 10 µm thick, intentionally nitrogen-doped (4 x 10<sup>15</sup> cm<sup>-3</sup>) epilayers on a highly nitrogen-doped SiC substrate. Lateral MOSFET samples underwent a conventional implantation schedule for the p-base and n+-source and drain implant, both carried out at 500°C, with the post-implantation anneal carried out at 1,700°C for 45 minutes in Ar (5 slm).

Once the samples had undergone an initial RCA1/HF(10%)/RCA2/HF(10%) clean procedure, a 1  $\mu$ m thick field oxide was deposited on the samples through LPCVD, details of which are outlined below. The process window was opened by means of photolithography and the deposited oxide was thinned to approximately 30 nm in the gate area through reactive ion etching (RIE). The final 30 nm were removed using a wet etch in diluted 10% buffered oxide etch (BOE). The gate oxides were then deposited or grown using one of the following oxidation routines:

- 1. **ALD** deposition of SiO<sub>2</sub> using bis(diethylamino)silane (BDEAS) and an oxygen plasma at 200°C (750 cycles) or

- 2. **ALD** deposition of SiO2 using bis(diethylamino)silane (BDEAS) and an oxygen plasma at 200°C (750 cycles) plus a **PDA in FG** ambient (5 slm, 5%H<sub>2</sub>) at 1,100°C for 1 h.

- 3. **LPCVD** using tetraethyl orthosilicate (TEOS) as a Si precursor.

- 4. Direct thermal growth at 1300°C for 5 hrs in diluted N<sub>2</sub>O (4 slm Ar: 1 slm N2O) ambient.

Since samples that had undergone routines 1 and 3 usually show a poor as-deposited oxide quality, a post-deposition anneal was performed on these samples in an oxidation furnace in N<sub>2</sub>O ambient at 1300°C for 2 hrs. All N<sub>2</sub>O treated samples (1,3 and 4) an oxide thickness of approx. 60 nm, with the FG-treated sample showing a lower thickness of approx. 35 nm. This process has shown to result in excellent SiO<sub>2</sub>/SiC interfaces and was reported previously by the authors [3]. The oxide growth/deposition of all samples was then followed by the contact formation to finalise the device structures.

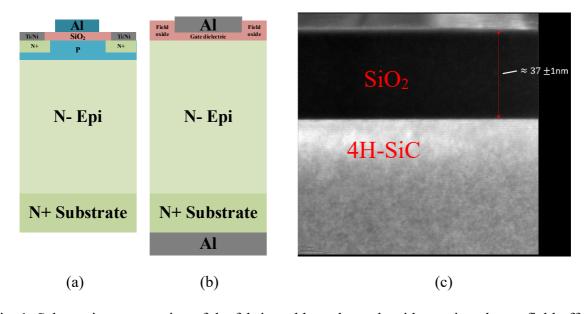

Fig. 1: Schematic cross section of the fabricated lateral metal-oxide-semiconductor field-effect transistor (LMOSFET) (a) and MOSCAP (b) as well as a cross-sectional TEM image to verify the oxide thickness of a ALD FG-annealed SiO<sub>2</sub> MOSCAP (c).

For MOSCAPs, 500 nm thick aluminium (Al) top- and bottomside contacts were e-beam evaporated.

LMOSFET structures used a 30 nm Ti/ 100 nm Ni e-beam evaporation followed by a RTA at 1,000°C for 2 minutes in Ar (5 slm ambient) to form source and drain contacts. This was then followed by a 500 nm Al gate contact deposition. A cross-section of the fabricated MOSCAP and LMOSFETs can be seen in Fig. 1 (a) and (b), respectively. To verify the oxide thickness, cross-sectional transmission electron microscopy (TEM) scans were carried out, that can be seen in Fig. 1 (c).

Room temperature vertical C-V measurements were performed on at least 20 MOSCAPs using an Agilent E4980A LCR meter to extract flatband voltage, hysteresis and frequency dispersion values, which are not going to be separately reported here. The results of these measurements can be found in [6]. Furthermore, vertical I-V as well as constant-voltage TDDB measurements were performed at 175°C using a Semiprobe semi-automatic probe station with a Keysight B1505A parameter analyser. Lateral MOSFET measurements were done at the same semi-automatic probe station rig at room temperature.

#### Results

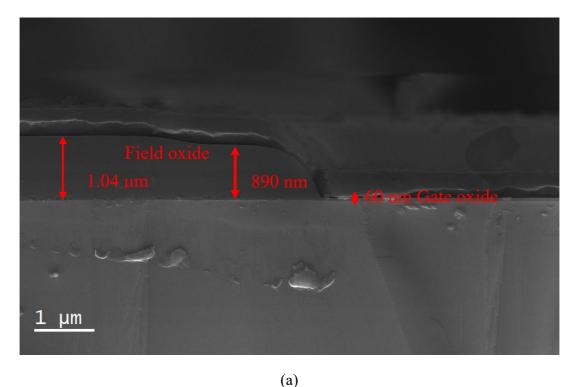

An overview of the constant voltage TDDB as well as average breakdown fields of the investigated vertical device structures (Fig. 2 (a)) at 175°C can be found in Table 1 below.

Table 1: Breakdown electric field, fail time as well as breakdown charge 9.6, 9, 8.5 and 8 MV/cm. For this analysis, at least 50 each devices were measured at  $175^{\circ}$ C. Device area was  $7.86 \times 10^{-5}$  cm<sup>2</sup>.

| Sample                                             | BV Field<br>(MV/cm) | 8 MV/cm<br>T <sub>fail,63%</sub> (s) | 8.5 MV/cm<br>T <sub>fail,63%</sub> (s) | 9 MV/cm<br>T <sub>fail,63%</sub> (s) | 9.6 MV/cm<br>T <sub>fail,63%</sub> (s) |

|----------------------------------------------------|---------------------|--------------------------------------|----------------------------------------|--------------------------------------|----------------------------------------|

| ALD Asdep. SiO <sub>2</sub>                        | $8.58 \pm 0.87$     | -                                    | -                                      | -                                    | -                                      |

| ALD<br>SiO <sub>2</sub> plus<br>FG-anneal          | $10.08 \pm 0.57$    | -                                    | -                                      | 5,623                                | 1,202                                  |

| ALD SiO <sub>2</sub><br>plus N <sub>2</sub> O      | $9.84 \pm 0.60$     | 11,220                               | 13,183                                 | 4,786                                | 120                                    |

| LPCVD<br>SiO <sub>2</sub> plus<br>N <sub>2</sub> O | $8.81 \pm 0.14$     | 7,413                                | 8,511                                  | 3,715                                | 65                                     |

| Direct<br>thermal<br>growth                        | $9.50 \pm 1.11$     | 5,012                                | 3,981                                  | 3,020                                | 75                                     |

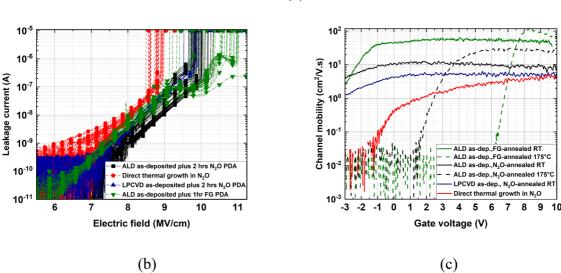

All investigated samples achieve average breakdown fields around 10 MV/cm at 175°C, which demonstrates the excellent oxide quality across the entire dataset, as can be observed in Fig. 2 (a). Here, the FG-treated samples achieve the highest electric breakdown field across the entire dataset,

Fig. 2: Schematic cross section of the fabricated vertical MOSCAP structure (a) using scanning electron microscopy (SEM). The I-V measurements of the investigated samples at 175°C (b) as well as extracted channel mobilities from LMOSFET structures at room temperature and 175°C (c).

once again proving the excellent suitability of this treatment compared to conventional thermal oxidation treatments, which has previously been established to be related to the creation of an oxygen-rich environment near the SiO<sub>2</sub>/SiC interface after ALD deposition of SiO<sub>2</sub>, in which Si complexes are then broken down into Si dangling bonds by the FG treatment, creating dangling bonds that can then be passivated better [3].

In fact, both ALD oxides that were investigated in this study showed the most promising TDDB performance across the entire dataset, too. Both FG-treated and N<sub>2</sub>O-annealed ALD-deposited SiO<sub>2</sub> layers outperform the other two oxides consistently, averaging 5623 s and 4786 s 63% fail time at 9 MV/cm, respectively. For the FG-treatment, this is the equivalent of a 50% improvement when compared to LPCVD-deposited samples. This trend is also true at lower stress levels.

For further analysis of the conduction mechanisms within the oxide layers, the LMOSFET structures were then investigated at room temperature and 175°C, too. Channel lengths were varied

from 150 µm to 15 µm, with representative channel mobility curves being depicted in Fig. 2 (c). The previously established improvement brought about in the ALD-deposited layers can be confirmed in this dataset,too, with the FG-treated LMOSFET structures showing peak field effective mobilities of 65 cm²/V.s and 108 cm²/V.s at room temperature and 175°C, respectively. This is an improvement of at least 300-400 percent, compared to all other oxidised device splits, where samples averaged between 10-20 cm²/V.s, confirming reports about channel mobilities in similarly oxidised structures [7, 8]. The huge improvement brought about by the low-temperature deposition seems to be coming at the expense of an increase in threshold voltage instability at elevated temperatures for the FG-treated samples, an effect which will require further investigation.

### **Summary**

Improvements to ALD as-deposited SiO<sub>2</sub> layers, in terms of breakdown electric field (10.08 MV/cm), TDDB performance (highest t<sub>fail,63%</sub> at all investigated electric fields) and channel mobility (60 cm<sub>2</sub>/V.s and 108 cm<sub>2</sub>/V.s at room temperature and 175°C, respectively) have been achieved by carrying out a post-deposition anneal in FG-ambient at 1100°C for 1 hour. Even when carrying out a PDA in N<sub>2</sub>O ambient, reasonable improvements could be achieved when compared to samples which utilized oxides that had been formed in direct oxide growth.

## References

- [1] A. O'Neill, O. Vavasour, S. Russell, F. Arith, J. Urresti, and P.M. Gammon, "Dielectrics in Silicon Carbide Devices: Technology and Application," in *Advancing Silicon Carbide Electronics Technology II: Core Technologies of Silicon Carbide Device Processing*, vol. 69, p. 63, 2020.

- [2] T. Kimoto and J.A. Cooper, Fundamentals of silicon carbide technology: growth, characterization, devices and applications. John Wiley & Sons, 2014.

- [3] A.B. Renz, O.J. Vavasour, P.M. Gammon, T. Dai, M.Antoniou, and V.A. Shah, "The improvement of atomic layer deposited SiO<sub>2</sub>/4H-SiC interfaces via a high temperature forming gas anneal,"in *Materials Science in Semiconductor Processing*, vol. 122, p. 105527.

- [4] A.B. Renz, O.J. Vavasour, P.M. Gammon, T. Dai, M. Antoniou, and V.A. Shah, "Development of high-quality gate oxide on 4H-SiC using atomic layer deposition," in *Materials Science Forum*, 2020, vol. 1004: Trans Tech Publ, pp. 547-553.

- [5] P. Fiorenza, F. Giannazzo, and F. Roccaforte, "Characterization of SiO<sub>2</sub>/4H-SiC interfaces in 4H-SiC MOSFETs: A review," in *Energies*, vol. 12, no. 12, p. 2310, 2019.

- [6] A. B.Renz, O.J. Vavasour, P.M. Gammon, F. Li, T. Dai, G.W.C. Baker, J. Gott, and V.A. Shah, "(Invited, Digital Presentation) Improved Reliability of 4H-SiC Metal-Oxide-Semiconductor Devices Utilising Atomic Layer Deposited Layers with Enhanced Interface Quality," in *ECS Transactions*, vol. 108, no. 2, p. 43, 2022.

- [7] F. Li, Y.K. Sharma, M.R. Jennings, A. Perez-Tomas, V.A. Shah, and P.A. Mawby, "Improved channel mobility by oxide nitridation for n-channel MOSFET on 3C-SiC (100)/Si," in *Materials Science Forum*, 2016, vol. 858: Trans Tech Publ, pp. 667-670.

- [8] H. Rong, Y.K. Sharma, T. Dai, F. Li, and P.A. Mawby, "High temperature nitridation of 4H-SiC MOSFETs," in *Materials Science Forum*, 2016, vol. 858: Trans Tech Publ, pp. 623-626.