www.10.4020/p-3w3808 © 2023 The Author(s). Published by Trans Tech Publications Ltd, Switzerland.

# **Outlook for Dielectric/SiC Interfaces for Future Generation MOSFETs**

Daniel J. Lichtenwalner<sup>1,a\*</sup>, Sei-Hyung Ryu<sup>1,b</sup>, Brett Hull<sup>1,c</sup>, Scott Allen<sup>1,d</sup>, and John W. Palmour<sup>1,e</sup>

Submitted: 2022-08-26

Accepted: 2022-11-11

Online: 2023-05-31

<sup>1</sup>Wolfspeed, 4600 Silicon Drive, Durham, NC 27703, USA

<sup>a</sup>daniel.lichtenwalner@wolfspeed.com, <sup>b</sup>sei-hyung.ryu@wolfspeed.com, <sup>c</sup>brett.hull@wolfspeed.com, <sup>d</sup>scott.allen@wolfspeed.com, <sup>e</sup>john.palmour@wolfspeed.com

**Keywords:** metal-oxide-semiconductor, interface, channel mobility, dielectrics.

**Abstract.** Silicon carbide (SiC) metal-oxide semiconductor (MOS) power devices such as metal-oxide semiconductor field-effect transistors (MOSFETs) require a stable and low defect-density interface, and a high-quality dielectric, for good device performance and reliability. Notably, the interface and dielectric properties determine the threshold voltage stability, the field-effect channel mobility, and the device lifetime as limited by dielectric breakdown in both the forward on-state and reverse blocking conditions. Here we discuss the present state of SiC MOS processing and properties and point to directions for future development. Important items to address are: 1) interface passivation approaches; 2) dielectrics; 3) device design; and 4) in-depth measurements of the interface quality and reliability.

### Introduction

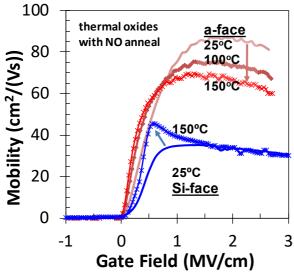

The present state-of-the-art MOS interface for SiC power devices consists of thermally grown SiO<sub>2</sub> with a nitric oxide (NO) post-anneal on Si-face (0001) 4H-SiC (tilted off-axis ~4° in the [11-20] direction). This provides a stable nitrogen passivation layer [1] and good dielectric reliability [2], but with a remaining high density of interface traps ( $D_{IT}$ ) near the conduction band, about two orders of magnitude higher than for Si MOS devices. Thus, the channel current is lower than the material limits [3, 4], and the threshold stability, while usable, has room for improvement. Although the channel mobility on a trench MOSFET device (a-face {11-20} or m-face {1-100}) is typically higher than that of the Si-face [5, 6] indicative of lower traps levels as shown in Fig. 1, room for improvement remains with respect to a-face or m-face interfaces due to the remaining traps contributing to threshold shift and hysteresis [6, 7]. Informative reviews of SiO<sub>2</sub>/SiC MOS interface issues are found in Lui et al. [8] and Kimoto and Watanabe [3].

Improvements to the interface to lower trap levels and get closer to an ideal interface would bring improvements to the overall device performance; some of these are listed in table I. Note that higher mobility typically is tied to lower interface trap levels (density (D<sub>IT</sub> traps/(eV\*cm²)) or total number (N<sub>IT</sub>, traps/cm²)); although mobility could be enhanced by other things as well, such as reduced interface roughness or reduced number of near-interface (oxide) traps (NIT or NIOT). Regardless, any performance benefit must come without a penalty in reliability or drift; this is the main challenge for competing processes which aim to replace the NO passivation approach. A list of relevant reliability issues to consider are listed in Table II.

**Table I.** List of performance benefits that a higher mobility or lower defect density would enable.

| Improvement                            | Enabled by:                                                                       |

|----------------------------------------|-----------------------------------------------------------------------------------|

| Lower on-resistance R <sub>on,sp</sub> | High mobility                                                                     |

| Lower $R_{on,sp}$ and improved $V_T$   | Lower near-interface oxide traps (NIT or NIOT), or                                |

| stability                              | interface trap reduction (N <sub>IT</sub> /D <sub>IT</sub> )                      |

| Improved Gate reliability              | Relaxed gate field enabled by high mobility                                       |

| Minimized short channel effects        | Longer channel can be utilized with higher mobility                               |

| Longer short circuit withstand time    | Channel saturation due to low N <sub>IT</sub> /D <sub>IT</sub> and longer channel |

| Reliability Issue                    | Concern:                                                     |

|--------------------------------------|--------------------------------------------------------------|

| Gate leakage (leading to device      | -Interface elements inter-diffusing with dielectric          |

| degradation)                         | -crystalline microstructure, defects/traps, and smaller band |

|                                      | offsets                                                      |

| Gate dielectric breakdown in the on- | -Interface elements or gate electrode inter-diffusion with   |

| state                                | dielectric                                                   |

|                                      | -Smaller band offsets, more Fowler-Nordhiem tunneling        |

|                                      | -Breakdown field of alternative dielectrics (lower than that |

|                                      | of SiO <sub>2</sub> )                                        |

| Threshold instability                | Fixed dielectric charge, near-interface charge, interface    |

|                                      | bonding stability between dielectric and SiC                 |

| Gate integrity in blocking mode      | Carrier injection and field effects on dielectric integrity, |

|                                      | especially if barrier heights are lower                      |

**Table II.** List of reliability issues linked to the MOS dielectric and interface passivation, also considering alternative high-k gate dielectric materials.

Whatever the solution for improved interface and channel properties, it will require finding the right materials and processing approaches which will allow them to be integrated into the gate processing module; for example, it may require a 'gate-last' approach such as done with high-k on Si solutions. Some solutions may be effective for the polar Si-face (0001) or C-face (000-1) channels, and others may be effective for the non-polar faces such as the a-face {11-20} or m-face {1-100} family of planes. Thus device design plays a role here that cannot be ignored.

The issue of SiC MOS channel and interface properties has been somewhat obscured by the way channel mobility has been reported. To give a clear indication of the channel current capability, the most straightforward approach is to report the field-effect mobility ( $\mu$ FE) [9],

$$\mu_{FE} = \left(\frac{L}{W}\right) * \left(\frac{1}{C_{ox} * V_D}\right) * \left(\frac{dI_D}{dV_G}\right) \tag{1}$$

where L and W are the channel length and width,  $V_D$  is the drain bias, Cox is the oxide capacitance per unit area, and  $dI_G/dV_G$  is the transconductance ( $g_m$ ). Although this is the clearest way to present the channel electrical properties, this does not help reveal the mobility limiting mechanisms. Presently, it is understood [9, 10] that a low field-effect mobility is due to either: 1) reduced free charge in the channel due to trapped charge (which will lower the  $\mu_{FE}$  value); or 2) due to the typical mobility-limiting factors of phonon scattering ( $\mu_{PH}$ ), coulomb scattering ( $\mu_C$ ), or surface roughness ( $\mu_{SR}$ ). These can be expressed using Matthiesson's rule:

$$\frac{1}{\mu} = \frac{1}{\mu_B} + \frac{1}{\mu_{PH}} + \frac{1}{\mu_C} + \frac{1}{\mu_{SR}} \tag{2}$$

where  $\mu_B$  is the bulk mobility and  $\mu$  is the overall electron inversion-layer mobility. To understand the electrical properties of the channel most completely, measurements to separate out the various mobility limiting effects would ideally be performed, as in a number of reports [4, 10-13].

### **Interface Passivation**

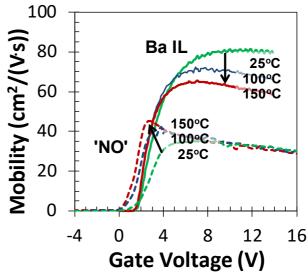

Alternative passivation approaches remain a potential way to improve channel mobility. It has been shown that for planar channel MOSFETs on Si-face, alternate interface passivation approaches with elements such as P [14], Ba or Sr [15, 16], or La [17] can increase the channel mobility. Shown in Fig. 2 are results for Ba passivation and a deposited SiO<sub>2</sub>, compared to a standard thermal oxide and NO anneal [15]. It was observed by high-low C-V that the density of interface traps (D<sub>IT</sub>) was reduced by the Ba passivation, and the temperature dependence of the  $\mu_{FE}$  showed minimal coulomb scattering effects. A recent report has shown that the free carrier density is increased with this Ba

Fig. 1. Mobility comparison of ~5E15 Al-doped Si-face and 1E16 doped a-face planar SiC MOSFETs with a thermal oxide and NO passivation [6].

**Fig. 2.** Mobility comparison of ~5E15 Al-doped Siface planar SiC MOSFETs with either NO or Ba passivation [15].

passivation process [18], which agrees with the previous findings of lower D<sub>IT</sub> levels. However, the gate oxide and threshold reliability have been shown to worsen if these are used with a SiO<sub>2</sub> dielectric. However, these approaches have proven that an improved MOS channel performance on Si-face 4H-SiC is possible.

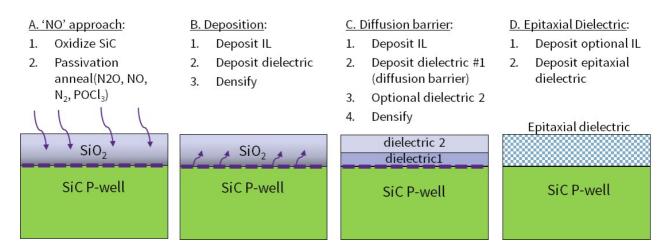

Future work to improve these approaches requires methods to ensure that these elements do not diffuse into the gate dielectric. Potential solutions consist of: 1) better methods of forming/depositing the passivation layer; or 2) using an alternative dielectric layer which serves as a diffusion barrier to that element. In the ideal case, the alternative higher-k dielectric would have a chemical compatibility with SiC such that an additional interface passivation would not be needed. Various approaches are shown schematically in Fig. 3. Approaches (a) (standard NO and POCl<sub>3</sub> [14] approaches) and (b) (for Ba, Sr [15,16] and La [17]) have been demonstrated; but an approach such as (c) with a dielectric diffusion barrier to the IL may be needed to allow new approaches to have good reliability. In Fig. 3(c), the first dielectric is a diffusion barrier to the IL element; the 2<sup>nd</sup> optional dielectric is needed if the properties of the first layer are not sufficient for reliability. As shown in Fig. 3(d), an epitaxial dielectric could be utilized (with or without an interface passivation layer) that would provide a low defect level, lattice-matched interface.

In addition, attempts to improve the present gate stack of SiO<sub>2</sub> with a N passivation (variations of process (a)) are also being actively investigated. The use a hydrogen anneal to etch/treat the surface before depositing SiO<sub>2</sub> and annealing in NO has shown real promise [19] on Si-face SiC, doubling the channel mobility compared to the standard thermal oxide plus NO anneal process. This needs to be studied in detail to confirm that gate quality and threshold stability is not compromised. Additional processes such as very high temperature N<sub>2</sub> anneals to reduce D<sub>IT</sub> levels and reduce V<sub>T</sub> hysteresis [19, 20] also may be promising directions to continue to study.

Finally, interface structure and properties can be elucidated using modeling approaches such as Monte-Carlo methods [11] or atomistic modeling approaches [21, 22]. Modeling results can often help direct or bring a more complete understanding to ongoing research efforts, and ultimately experimental and modeling results would show agreement.

**Fig. 3.** MOS processing approaches for interface passivation application. Approach (a) is the standard approach; (b) has been used for Ba, Sr [15,16] and La [17]; (c) or (d) may ultimately be needed to achieve new interface properties. The H<sub>2</sub> anneal approach [19] is a variant of (a).

#### **Dielectrics**

Transitioning away from SiO<sub>2</sub> to alternative dielectrics is another potential solution for achieving improved channel properties. As learned by the Silicon device community, high-k dielectric materials selection must take into account thermodynamic stability between semiconductor and dielectric [15], and electrical properties such as dielectric constant [23, 24], band offsets [25, 26], dielectric breakdown strength [27], and related materials properties; these relate not only to performance but to reliability concerns as well. Dielectrics on SiC need a bandgap much wider than is acceptable on Si, due to the wider bandgap of SiC compared to Si. Besides the materials properties listed, the alternative dielectric should satisfy these main conditions: 1) form an interface with low trap densities (or be a diffusion barrier for passivation elements); 2) have appropriate band offsets to minimize Fowler-Nordheim tunneling; 3) remain amorphous or not have high defect density (within grains or at grain boundaries); 4) be stable under the processing conditions required for MOSFET fabrication; and 5) display low failure rates relating to time-dependent dielectric breakdown (TDDB) and threshold instability.

Ideally, for SiC with a bandgap Eg ~3.25eV, an appropriate MOS dielectric would have an Eg >7eV (example materials listed in [23, 24]) with aligned band offsets to block current flow under positive and negative gate or drain bias. Materials which have been investigated as dielectrics on SiC include Al<sub>2</sub>O<sub>3</sub> [28], HfAlO [26], HfAlON [29]; related silicates and lanthanides also deserve investigation [30].

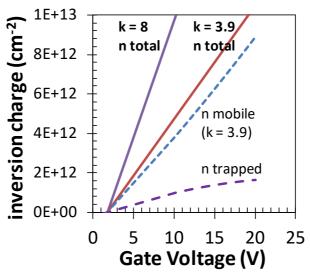

The main advantages offered by high-k dielectrics, presuming an equivalent or superior interface with SiC, are that: A) the high-k dielectric provides a higher channel charge (scaled by the dielectric constant ratio  $k_{\text{high-k}}/k_{\text{SiO2}}$ ) for the same gate thickness and bias (as shown in Fig. 4); and B) in high-drain bias blocking mode the field on the high-k dielectric will be lower than the SiO<sub>2</sub> field would be, as the dielectric field (E<sub>ox</sub> or E<sub>diel</sub>) equals the semiconductor field (E<sub>SiC</sub>) multiplied by the ratio of the dielectric constants of SiC and the dielectric ( $k_{\text{SiC}}/k_{\text{diel}}$ ) [31],

$$E_{diel} = \left(\frac{K_{SiC}}{K_{diel}}\right) \times E_{SiC} . \tag{3}$$

Thus a higher k value indicates a lower dielectric field in drain blocking mode operation. These potential benefits are recognized [3, 31], and are being pursued by some groups [32].

The use of an alternative dielectric may require a gate electrode other than Si that is more chemically compatible; TiN is one choice used with high-k Hf-based dielectrics on Si. This opens the possibility for work function selections that may prove beneficial for threshold voltage control.

**Fig. 4.** Graph showing: 1) how trapped charge due to interface states will lead to a lower mobile charge density in the channel than theoretically predicted (thus lowering the field-effect mobility); and 2) a dielectric with a dielectric constant 2X that of SiO<sub>2</sub> will double the channel inversion charge for the same gate bias, ~doubling the output device current if no other interface effects are present.

# **Device Design**

Device designs must also be optimized to take advantage of the improvements offered by a higher channel conduction, and the better channel saturation that could be achieved by decreasing the interface traps and carrier scattering sources. A device with higher channel mobility allows for design-related changes that can enable the improvements listed in Table I. Some improvements to reliability and stability and robustness can be realized for a MOSFET with a given R<sub>DS,on</sub> and blocking voltage, if the channel mobility were increased. Modifying existing devices by scaling the layout is one approach; another is to design entirely new devices which increase the channel area [33, 34], or use fully-depleted fin channels [35]. Existing device structures will clearly benefit from a high channel mobility; although radical device designs such as fully-depleted fin devices [35] could provide a solution to interface trap effects by design alone, eliminating the need for complex MOS materials and processing. In addition, changes to the doping profile of the channel can provide some benefits, such as counter-doping (summarized in [8]). Still, efforts to minimize channel defects and increase channel mobility will be generally useful for all MOS devices.

Physical modeling approaches such as TCAD can help drive device design to the optimal space; provided the models are properly informed by interface and dielectric measurements that allow the MOS properties to be fully calibrated in the model.

# **Interface Characterization: Performance and Reliability**

Comprehensive MOS characterization approaches are needed to fully understand the present state of interface trap density and related issues (fixed traps, near interface oxide traps, surface roughness, etc.). A recent review [36] discusses many important SiC defect characterization techniques and describes the energy levels of the defects probed by each technique. SiC MOS device interfaces are difficult to fully characterize due to issues related to the wide bandgap semiconductor, and the challenges of measuring very shallow and very deep traps, needed to characterize the entire bandgap. More complete and comprehensive measurements will enable a better understanding of why alternative approaches improve or degrade channel performance.

Commonly used measurements of note for characterizing MOS interface properties include high-low C-V capacitor measurements, which can probe relatively close to the band edges [36, 37], and lateral MOSFET charge pumping [36, 38] which probe traps within the mid-gap regions. Hall measurements of the channel from gated MOS Hall structures are very valuable for separating out

the various channel electrical parameters (carrier concentration, Hall mobility), and is an important characterization to perform [4, 10]. Ultimately, measurement results from tests such as these must be correlated to the channel mobility measured from MOSFET test structures [39]. It is important to use the temperature dependence of these parameters to fully characterize the effects of any given interface passivation.

Other more specialized techniques such as scanning probe microscopy [40], deep-level transient spectroscopy (DLTS) and magnetic resonance related techniques [36, 41] can help provide additional information for a more complete understanding of the MOS region.

Finally, gate dielectric reliability must be carefully studied before a new dielectric or interface process is accepted. Rigorous testing is required to qualify any MOSFET gate processing, as discussed in recent publications [42]. Threshold voltage stability is another key MOS reliability metric [43] which must be proven out for new MOS materials and processing. Finally, threshold instability under gate switching conditions also must be examined, as recent research has demonstrated this to be an important consideration under certain device operation conditions [44, 45].

# **Summary**

Attempts to improve SiC MOSFET channel performance need to continue for improved device performance to be realized. Previous and present research on SiC MOSFETs show that improvements are possible that would result in higher channel mobility and decreased threshold instability. Improved interface passivation, or new gate dielectrics, need to be fully characterized to ensure that performance benefits do not come at the cost of device reliability. Device design changes may also need to be considered to fully realize all potential benefits of higher channel mobility and/or the use of alternative dielectrics.

# References

- [1] G.Y. Chung, C.C. Tin, J.R. Williams, K. McDonald, R.K. Chanana, R.A. Weller, S.T. Pantelides, L.C. Feldman, O.W. Holland, M.K. Das, J.W. Palmour, IEEE Electron Dev. Lett. 22 (2001) 176-178.

- [2] D.J. Lichtenwalner, S. Sabri, E. van Brunt, B. Hull, S.-H. Ryu, P. Steinmann, A. Romero, S. Ganguly, D.A. Gajewski, S. Allen, and J.W. Palmour, 2020 IEEE International Integrated Reliability Workshop (IIRW), pp. 1-6 (2020).

- [3] T. Kimoto and H. Watanabe, Appl. Phys. Express 13, 120101 (2020).

- [4] M. Noguchi, T. Watanabe, H. Watanabe, K. Kita, and N. Miura, IEEE Trans. Electron Dev. 68(12), pp. 6321-29 (2021).

- [5] H. Yano, T. Hirao, T. Kimoto, H. Matsunami, K. Asano, and Y. Sugawara, IEEE Trans. Electron Dev. 20(12, pp. 611-13 (1999).

- [6] D.J. Lichtenwalner, L. Cheng, S. Allen, J.W. Palmour, A. Lelis and C. Scozzie, MRS Online Proceedings Library 1693, 25–30 (2014).

- [7] T. Nakanuma, A. Suzuki1, Y. Iwakata, T. Kobayashi, M. Sometani, M. Okamoto, T. Hosoi, T. Shimura, and H. Watanabe, IEEE Inter. Reliab. Phys. Symp. 3B.2-1 (2022).

- [8] G. Liu, B.R. Tuttle, and S. Dhar, Appl. Phys. Rev. 2, 021307 (2015).

- [9] T. Kimoto, J.A. Cooper, "Fundamentals of Silicon Carbide Technology," IEEE Press, John Wiley and Sons, Singapore (2014).

- [10] S. Dhar, S. Haney, L. Cheng, S.-H. Ryu, A. K. Agarwal, L. C. Yu, and K. P. Cheung, J. Appl. Phys. 108, 054509 (2010).

- [11] G. Pennington and N. Goldsman, J. Appl. Phys. 106, 063701 (2009).

- [12] H. Naik, T.P. Chow, Mat. Sci. Forum Vols. 679-680, pp 633-636 (2011).

- [13] H. Takeda, M. Sometani, T. Hosoi, T. Shimura, H. Yano and H. Watanabe, Mat. Sci. Forum Vol. 1004, pp. 620–26 (2020).

- [14] D. Okamoto, H. Yano, T. Hatayama, and T. Fuyuki, Appl. Phys. Lett. 96, 203508 (2010).

- [15] D.J. Lichtenwalner, L. Cheng, S. Dhar, A. Agarwal, and J.W. Palmour, Appl. Phys. Lett. 105, 182107 (2014).

- [16] D.J. Lichtenwalner et al., Mat. Sci. Forum Vol. 897, pp 163-166 (2017).

- [17] Xiangyu Yang, Bongmook Lee, and Veena Misra, Vol. 66(1), 539 (2019).

- [18] S. Sekine, M. Okada, T. Kumazawa, M. Sometani, H. Hirai, N. Serizawa, R. Hasunuma, M. Okamoto, and S. Harada, Jpn. J. Appl. Phys. 60, SBBD08 (2021).

- [19] K. Tachiki, M. Kaneko, and T. Kimoto, Applied Physics Express 14, 031001 (2021).

- [20] T. Kobayashi, T. Okuda1, K. Tachiki, K. Ito, Y. Matsushita, and T. Kimoto, Applied Physics Express 13, 091003 (2020).

- [21] Z. Zhang, Z. Wang, Y. Guo, and J. Robertson, Appl. Phys. Lett. 118, 031601 (2021).

- [22] Y. Xu, X. Zhu, H. D. Lee, C. Xu, S. M. Shubeita, A. C. Ahyi, Y. Sharma, J. R. Williams, W. Lu, S. Ceesay, B. R. Tuttle, A. Wan, S. T. Pantelides, T. Gustafsson, E. L. Garfunkel, and L. C. Feldman, J. Appl. Phys. 115, 033502 (2014).

- [23] D.G. Schlom and J. H. Haeni, MRS Bulletin 27, 198 (2002).

- [24] G.D. Wilk, R.M. Wallace, and J.M. Anthony, J. Appl. Phys. 89, 5243 (2001).

- [25] J. Robertson, B. Falabretti, Materials Science and Engineering B 135, pp. 267–71 (2006).

- [26] R. Suri, C.J. Kirkpatrick, D.J. Lichtenwalner, and V. Misra, Appl. Phys. Lett. 96, 042903 (2010).

- [27] J. McPherson, J-Y. Kim, A. Shanware, and H. Mogul, Appl. Phys. Lett. 82, 2121 (2003).

- [28] D.J. Lichtenwalner, V. Misra, S. Dhar, S.-H. Ryu, and A. Agarwal, Appl. Phys. Lett. 95, 152113 (2009).

- [29] T. Hosoi, S. Azumo, Y. Kashiwagi, S. Hosaka, K. Yamamoto, M. Aketa, H. Asahara, T. Nakamura, T. Kimoto, T. Shimura, H. Watanabe, Proc. 29<sup>th</sup> ISPSD, pp. 247-250 (2017).

- [30] D.J. Lichtenwalner, (2013). Chap. 9 in: Kar, S. (eds) High Permittivity Gate Dielectric Materials. Springer Series in Advanced Microelectronics, vol 43. Springer, Berlin, Heidelberg.

- [31] S. Sridevan, P.K. McLarty and B.J. Baliga, Proc. 9<sup>th</sup> ISPSD pp. 153-156, (1997).

- [32] G. Romano, A. Mihaila and L. Knoll, PCIM Asia, pp. 183-187 (2021).

- [33] Y. Nanen, H. Yoshioka, M. Noborio, J. Suda, and T. Kimoto, IEEE Trans. Electron Dev., 56(11), pp. 2632–2637, (2009),

- [34] R.P. Ramamurthy, N. Islam, M. Sampath, D.T. Morisette, and J.A. Cooper, IEEE Trans. Electron Dev. 42(10), pp. 90-93 (2021).

- [35] F. Udrea, K. Naydenov, H. Kang, T. Kimoto, T. Kato, E. Kagoshima, T. Nishiwaki, H. Fujiwara, Proc. 33<sup>rd</sup> ISPSD, pp. 75-78 (2021).

- [36] M.E. Bathen, C.T.-K. Lew, J. Woerle, C. Dorfer, U. Grossner, S. Castelletto, and B. C. Johnson, J. Appl. Phys. 131, 140903 (2022).

- [37] H. Yoshioka, T. Nakamura, and T. Kimoto, J. Appl. Phys. 112, 024520 (2012).

- [38] A. Salinaro, G. Pobegen, T. Aichinger, B. Zippelius, D. Peters, P. Friedrichs, and L. Frey, IEEE Trans. Electron Dev. 62, (2015).

- [39] H. Yoshioka, J. Senzaki, A. Shimozato, Y. Tanaka, and H. Okumura, Appl. Phys. Lett. 104, 083516 (2014).

- [40] L.K. Swanson, P. Fiorenza, F. Giannazzo, A. Frazzetto, and F. Roccaforte, Appl. Phys. Lett. 101, 193501 (2012).

- [41] M. Anders, P. Lenahan, and A. Lelis, J. Appl. Phys. 122, 234503 (2017).

- [42] T. Aichinger, and M. Schmidt, 2020 IEEE International Reliability Physics Symposium (IRPS), pp. 1-6 (2020).

- [43] D.B. Habersat, A.J. Lelis and R. Green, 2020 IEEE International Reliability Physics Symposium (IRPS), pp. 1-4 (2020).

- [44] X. Zhong, H. Jiang, L. Tang, X. Qi, P. Jiang, and L. Ran, IEEE Trans. Electron Dev. 69(6), 3328 (2022).

- [45] P. Salmen, M.W. Feil, K. Waschneck, H. Reisinger, G. Rescher, I. Voss, M. Sievers, T. Aichinger, Microelectronics Reliability 135, 114575 (2022).