# Small-Signal Impedance and Split C-V Characterization of High-к SiC Power MOSFETs

Submitted: 2022-09-04

Revised: 2022-12-06

Online: 2023-06-05

Accepted: 2022-12-07

Salvatore Race<sup>1,a\*</sup>, Ivana Kovacevic-Badstuebner<sup>,1,b</sup>, Roger Stark<sup>1,2,c</sup>, Alexandar Tsibizov<sup>1,d</sup>, Manuel Belanche<sup>1,e</sup>, Yulieth Arango<sup>3,f</sup>, Gianpaolo Romano<sup>3,g</sup>, Lars Knoll<sup>3,h</sup>, and Ulrike Grossner<sup>1,i</sup>

<sup>1</sup>Advanced Power Semiconductor Laboratory, ETH Zurich, Physikstrasse 3, 8092 Zürich, Switzerland

<sup>2</sup>SiwssSEM Technologies AG, Dammweg 23, 5600 Lenzburg, Switzerland <sup>3</sup>Hitachi Energy, 5600 Lenzburg, Switzerland

<sup>a</sup>race@aps.ee.ethz.ch, <sup>b</sup>kovacevic@aps.ee.ethz.ch, <sup>c</sup>stark@aps.ee.ethz.ch, <sup>d</sup>a.g.tsibizov@gmail.com, <sup>e</sup>belanche@aps.ee.ethz.ch, <sup>f</sup>yulieth.arango@hitachienergy.com, <sup>g</sup>gianpaolo.romano@hitachienergy.com, <sup>h</sup>lars.knoll@hitachienergy.com, <sup>i</sup>ulrike.grossner@ethz.ch

**Keywords:** SiC MOSFETs, High-κ Dielectric, C-V Characterization, Channel-Drift Resistances, Gate Impedance

**Abstract** In this work, the improvement of SiC power MOSFET performance achieved using high- $\kappa$  gate-dielectrics instead of the standard SiO<sub>2</sub> is investigated by means of advanced gate-impedance characterization. The benefit of using high- $\kappa$  gate-dielectrics with high dielectric constant is demonstrated by comparing SiC MOSFETs with pure high- $\kappa$ , a stack of SiO<sub>2</sub>/high- $\kappa$ , as well as pure SiO<sub>2</sub>. Namely, the fabricated high- $\kappa$  SiC MOSFETs show a superior performance to SiC MOSFETs with SiO<sub>2</sub>/SiC interface with respect to channel resistance and interface quality. The proposed characterization approach is non-destructive and applicable to packaged power devices.

# Introduction

In comparison to Si device technology, threshold voltage instability due to traps at the SiO $_2$ -SiC interface has turned out to be a characteristic feature of SiC power MOSFETs [1]. It has been recently shown that high- $\kappa$  gate dielectrics replacing native SiO $_2$  represent a promising solution for improving the performance of vertical SiC power MOSFETs with respect to threshold voltage hysteresis and threshold voltage shift under gate stress [2]. An improved interface quality furthermore enables achieving lower specific on-state resistance [3]. In this paper split C-V and small-signal impedance characterization of pure high- $\kappa$ , SiO $_2$ /high- $\kappa$  and pure SiO $_2$  SiC power MOSFETs are compared, in order to analyze the impact of gate-dielectrics on the device performance.

### **Analyzed Gate-Dielectrics SiC Power MOSFET Samples**

Planar-gate 1.2 kV SiC power MOSFET samples with high-κ- (K1, K1b, K2, K2b) and high-κ/SiO<sub>2</sub> dielectrics (S1, S2) from Hitachi Energy, and three Wolfspeed 1.2 kV SiC power MOSFETs with SiO<sub>2</sub> dielectric both from Gen 2 and the improved Gen 3 technology (M1, M2, M2b) are selected for the analysis, see Table 1. The K1, K1b and S1 samples have the same chip and cell layouts, *i.e.* same active area, termination region, pitch-size and gate layout, they differ only for the gate-dielectric stack. The same applies for the K2, K2b and S2 samples. All samples have comparable on-state resistances however different pitch sizes. A direct comparison of the fabricated high-κ to SiO<sub>2</sub> reference samples and the selected commercial SiC power MOSFETs with respect to voltage-/frequency-dependent gate impedance is shown in the following.

| Name | Туре                                              | $R_{\mathrm{ds,ON}}\left[m\Omega\right]\left(@V_{\mathrm{gs}}=15V\right)$ | pitch size $[\mu m]$ |

|------|---------------------------------------------------|---------------------------------------------------------------------------|----------------------|

| K1   | high-κ (Hitachi Energy)                           | 21                                                                        | 10.5                 |

| K1b  | high-κ (Hitachi Energy)                           | 25                                                                        | 10.5                 |

| K2   | high-κ (Hitachi Energy)                           | 24                                                                        | 14.5                 |

| K2b  | high-κ (Hitachi Energy)                           | 26                                                                        | 14.5                 |

| S1   | high-κ/SiO <sub>2</sub> (Hitachi Energy)          | 33                                                                        | 10.5                 |

| S2   | high-κ/SiO <sub>2</sub> (Hitachi Energy)          | 38                                                                        | 14.5                 |

| M1   | SiO <sub>2</sub> (Wolfspeed, 2 <sup>nd</sup> Gen) | 33                                                                        | 9.1                  |

| M2   | SiO <sub>2</sub> (Wolfspeed, 3 <sup>rd</sup> Gen) | 20                                                                        | 6.1                  |

| M2b  | SiO <sub>2</sub> (Wolfspeed, 3 <sup>rd</sup> Gen) | 27                                                                        | 6.1                  |

Table 1: Planar gate 1.2 kV SiC Power MOSFET samples used for analysis.

# **Small-Signal Impedance Characterization**

Small-signal impedance measurements are performed to extract datasheet device characteristics such as internal gate resistance and capacitance-voltage behavior. Split C-V characterization on the other hand is typically used to measure the reverse power MOSFET capacitance,  $C_{\rm rss}$ . In this paper, the gate impedance is measured to evaluate the internal gate resistance as function of frequency and gate bias, while split C-V measurements at different frequencies are performed to evaluate the gate-drain  $C_{\rm dg}$  and gate-source  $C_{\rm sg}$  capacitances, separately. Furthermore, the channel  $R_{\rm ch}$  and drift resistance  $R_{\rm drift}$  (=  $R_{\rm jfet}$  +  $R_{\rm epi}$  +  $R_{\rm sub}$ ) components of the total on-state resistance are extracted based on the split  $C_{\rm dg}$  and  $C_{\rm sg}$  measurements as described in [4]. All measurements are performed using a Keysight E4990A impedance analyzer for the SiC power MOSFET samples specified in Table 1.

### Split C-V gate characterization: Results

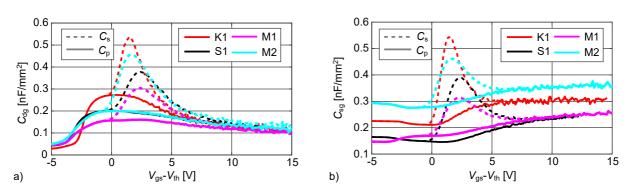

From the split C-V measurements,  $C_{\rm dg}$  and  $C_{\rm sg}$  components can be either extracted using a series  $(C_{\rm s}-R_{\rm s})$  or parallel  $(C_{\rm p}||G_{\rm p})$  equivalent model, where the peaks observed in the series  $C_{\rm sg,s}$  and  $C_{\rm dg,s}$  can be correlated to the transconductance  $g_{\rm m}$  extracted from the transfer-characteristic  $I_{\rm d}$ - $V_{\rm gs}$  as described in [4]. The  $C_{\rm sg}$  and  $C_{\rm dg}$  of K1, S1, M1 and M2 measured at  $f=30\,{\rm kHz}$  are shown in Fig. 1. Comparing  $C_{\rm dg,s}$  and  $C_{\rm sg,s}$  of K1, S1, M1, and M2 SiC power MOSFETs, higher peaks within  $C_{\rm sg,s}$  and  $C_{\rm dg,s}$  of K1 point out to higher transconductance for high- $\kappa$ -than for high- $\kappa$ -SiO<sub>2</sub> and pure SiO<sub>2</sub>-interface. Furthermore, an improvement of SiC power MOSFET technology from Wolfspeed from Gen2 to Gen3 with respect to  $g_{\rm m}$  can be clearly observed by comparing M1 and M2.

Fig. 1: Measured a)  $C_{dg}$  and b) $C_{sg}$  of SiC power MOSFET samples K1, S1, M1 and M2. The results are normalized by device active area and shifted by treshold voltage  $V_{th}$ .

## **Extraction of on-state resistance components: Results**

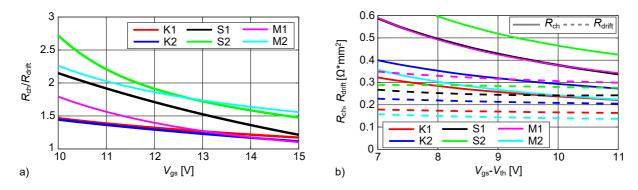

Since the parallel capacitances  $C_{\rm sg,p}$  and  $C_{\rm dg,p}$  carry only the information about MOSFET capacitances and not about  $g_{\rm m}$ ,  $C_{\rm sg,p}$  and  $C_{\rm dg,p}$  are used to evaluate the  $R_{\rm ch}/R_{\rm drift}$  ratio as shown in Fig. 2a). The total drain-to-source on-state resistance  $R_{\rm ds,ON}$  is evaluated from  $I_{\rm d}$ - $V_{\rm gs}$  measurements at  $V_{\rm ds}=50\,{\rm mV}$ , thus allowing the evaluation of individual components  $R_{\rm drift}$  and  $R_{\rm ch}$  as function of  $V_{\rm gs}$ . The  $R_{\rm drift}$  and  $R_{\rm ch}$  results normalized by device active area are shown in Fig. 2b). First, a dependence of  $R_{\rm ch}$  and  $R_{\rm drift}$  on the pitch size can be extracted from Fig. 2b) by comparing K1 and K2 SiC power MOSFETs. Second, the proposed characterization method clearly points to reduced  $R_{\rm ch}$  and  $R_{\rm drift}$  of SiC power MOSFETs K1 and K2 with pure high- $\kappa$  gate-interface than in the case of S1 and S2 with high- $\kappa$ /SiO<sub>2</sub>-stack. Another interesting observation is that  $R_{\rm ch}$  of K1 and M2 are comparable despite a smaller pitch of M2 that can be explained by (1) increased  $C_{\rm ox}$ , i.e. higher transconductance of the MOSFET  $g_{\rm m}$ , and (2) an improved channel mobility due to higher interface quality.

Fig. 2: Extracted a)  $R_{ch}/R_{drift}$  ratio and b)  $R_{drift}$  and  $R_{ch}$  components normalized by device active area and shifted by  $V_{th}$  of SiC power MOSFET samples K1, K2, S1, S2, M1 and M2.

# Internal Gate Resistance $R_{gg}$ Characterization

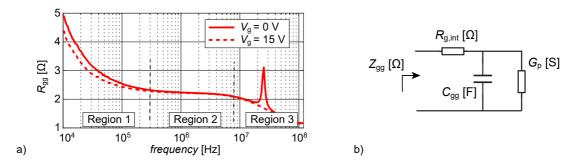

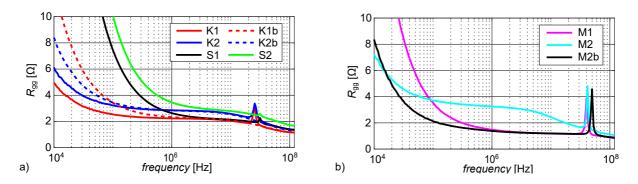

Internal gate resistance  $R_{\rm gg}$  is extracted as the real part of the measured gate impedance  $Z_{\rm gg}$ . The measured  $R_{\rm gg}$  of K1 at the gate-source voltage  $V_{\rm gs} = 0 \, \text{V}$  and 15 V is presented in Fig. 3a). Typically, in datasheets only  $R_{gg}$  at f = 1 MHz and  $V_{gs} = 0$  V is provided. However,  $R_{gg}$  is  $V_{gs}$ - and f-dependent and three regions as highlighted in Fig. 3a) can be distinguished: 1) very high  $R_{gg}$  at low frequency decreasing with f, 2)  $R_{gg}$  approximately constant in the mid-frequency range below few MHz, and 3) the high-frequency range above 10 MHz with  $R_{\rm gg}$  decreasing. Region 1 can be related to dielectric-SiC interface traps; Region 2 to the resistance of the polysilicon gate and metal-gate runner, and Region 3 represents the distributed behavior of the polysilicon gate layout that becomes dominant at fast switching transients [5]. The equivalent model shown in Fig. 3b) can be used to describe this behavior, where  $C_{\rm gg}$  represents the input gate-capacitance,  $R_{\rm g,int}$  stands for the resistance of the polysilicon gate and  $G_p$  models the dielectric "leakage". With smaller  $G_p$  and higher  $C_{gg}$ , Region 2 of  $R_{gg}(f)$ is extended in the lower frequency range, while higher  $G_p$  and smaller  $C_{gg}$  shorten Region 2. Since  $G_p$  can be high for SiC power MOSFETs because of the high defect density at the SiC-dielectric interface,  $R_{gg}$  at 1 MHz can often include the effect of traps and hence,  $R_{gg,1MHz}$  can be misleading for evaluating the actual internal gate resistance. The measured  $R_{gg}(f)$  at  $V_{gg} = 0$  V of SiC power MOSFET with high- $\kappa$  and high- $\kappa$ /SiO<sub>2</sub>-stack K1, K1b, K2, K2b, S1 and S2 are shown in Fig. 4a), while  $R_{gg}(f)$ of commercial SiC power MOSFETs M1, M2, and M2b are presented in Fig. 4b). In the frequency region between  $\approx 20$  MHz-100 MHz,  $R_{\rm gg}$  of K1, K1b and S1 SiC power MOSFETs overlap, c.f. Fig. 4a), which corresponds to Region 2 marked in Fig. 3. Namely, as K1, K1b and S1 are only different with respect to dielectric-semiconductor interface, the measurements confirm that  $R_{\rm gg}$  in Region 2 is determined only by the polysilicon and metal resistance of the gate layout. On the other hand, it can be seen that the quality of the dielectric-semiconductor interface affects Region 1 of  $R_{gg}$ , i.e. a

Fig. 3: Frequency dependent internal gate impedance  $Z_{gg}(f)$ : a) real part of  $Z_{gg}$ ,  $R_{gg}(f)$  for K1 at  $V_{gs} = 0$  V and 15 V, b) an equivalent lumped model of  $Z_{gg}$ .

Fig. 4: Measured  $R_{gg}(f)$  at  $V_{gs} = 0$  V: a) K1, K1b, K2, K2b, S1 and S2, b) M1, M2, and M2b.

higher interface quality leads to a smaller  $G_{\rm p}$  in the model shown in Fig.3b), however this effect can not be fully distinguished from the  $C_{\rm gg}$  variation between samples due to different dielectrics. K1 with an improved high- $\kappa$  dielectric in comparison to K1b, obtained with a better deposition approach, has the smaller  $G_{\rm p}$  than both K1b and S1, which can be related to reduced dielectric and interface-traps. Similarly, K2 has the smaller  $G_{\rm p}$  than K2b and S2 SiC power MOSFETs. Furthermore, it can be seen that pitch size also affects the equivalent lumped  $R_{\rm gg}$  in Region 2. The measurements in Fig. 4b) suggest that  $G_{\rm p,M2}$  and  $G_{\rm p,M2b}$  are smaller than  $G_{\rm p,M1}$ , i.e. Region 2 is shifted towards lower frequencies, however gate design parameters affecting  $C_{\rm gg}$  also have an influence on Region 1. The clear distinction between these two concurring effects impacting Region 1 is under further investigation.

# $R_{\rm gg}$ as function of gate-source Voltage $V_{\rm gs}$

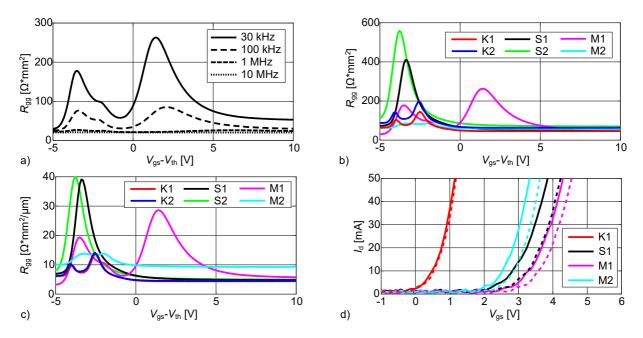

In the next step,  $R_{\rm gg}$  was characterized as function of gate-source voltage  $V_{\rm gs}$ .  $R_{\rm gg,MI}(V_{\rm gs}-V_{\rm th})$  normalized by the device active area (mm²) is shown in Fig. 5a) for  $f=30\,\rm kHz$ ,  $100\,\rm kHz$ ,  $1\,\rm MHz$  and  $10\,\rm MHz$ . Sweeping  $V_{\rm gs}$  is expected to reveal the impact of traps at different energy levels in the bandgap on the  $R_{\rm gg}$ . At high frequencies, i.e. 10 MHz, the traps are ineffective and the  $R_{\rm gg}$  is independent from  $V_{\rm gs}$  and only determined by the gate-layout as discussed for Fig. 3a).  $R_{\rm gg}(V_{\rm gs}-V_{\rm th})$  normalized by the device active area (mm²) of K1, K2, S1, S2, M1, and M2 are presented in Fig. 5b) and Fig. 5c), without and with scaling with the pitch size, respectively. The lower peaks amplitude of the high- $\kappa$  samples and M2 further support the conclusion of higher interface quality of these samples and/or higher  $C_{\rm gg}$ . Interestingly, M1 shows a peak in the positive  $V_{\rm gs}-V_{\rm th}$  range suggesting the presence of different interface traps closer to the conduction band, which have been removed in the latest Wolfspeed device generation. The scaling by the pitch size is necessary to make more meaningful comparison of different devices, namely in Fig. 5c) the peak amplitude for the same technology are equalized independently on the cell pitch: K1-K2 and S1-S2. The  $V_{\rm th}$  hysteresis of K1, S1, M1 and M2 is shown in Fig. 5d). M2 presents a significant  $V_{\rm th}$  hysteresis despite the smaller  $R_{\rm gg}(V_{\rm gs})$  peak shown in Fig. 5c) and the small  $C_{\rm ox}$  of SiO<sub>2</sub>, that can lead to the conclusion that the defects affecting  $R_{\rm gg}(V_{\rm gs})$  differ from the

defects impacting the  $V_{th}$ -hysteresis [6]. It should be noted that pure high-κ dielectric shows negligible hysteresis in comparison to SiO<sub>2</sub>/high-κ and pure SiO<sub>2</sub> samples.

Fig. 5: Measured  $R_{\rm gg}(V_{\rm gs}-V_{\rm th})$  normalized by the device active area (mm²) of a) M1 at different frequencies, b) K1, K2, S1, S2, M1, and M2 at  $f=30\,\rm kHz$ , c) K1, K2, S1, S2, M1, and M2 at  $f=30\,\rm kHz$  scaled with pitch size; d) the measured  $I_{\rm d}$ - $V_{\rm gs}$  hysteresis (@ $V_{\rm ds}=50\,\rm mV$ ,  $V_{\rm gs}=[-5V,15V]$ ) of K1, S1, M1 and M2, upward (solid) and downward (dashed) sweep.

### **Summary**

This work reveals the benefit of high-κ gate dielectrics for SiC power MOSFETs and also demonstrates that the standard small-signal impedance measurements can be extended for more precise information on device performance and application-relevant characteristics. The presented gate impedance characterization can be adopted as non-destructive investigation approach to analyze the device quality with special focus on the SiC/gate-dielectric interface for packaged semiconductor devices.

### References

- [1] K. Puschkarsky et al.: IEEE Transactions on Electron Devices Vol. 66, (2019) pp. 4604-4616

- [2] S. Wirths et al.: 32nd Int. Symp. on Power Semic. Dev. and ICs (ISPSD), 2020.

- [3] S. Wirths et al.: 31st Int. Symp. on Power Semic. Dev. and ICs (ISPSD), 2019.

- [4] R. Stark et al.: IEEE Transactions on Power Electronics Vol. 37 No. 9 (2022) pp. 10572–10584

- [5] S. Race et al.: 34th Int. Symp. on Power Semic. Dev. and ICs (ISPSD), 2022.

- [6] P. Fiorenza et al.: IEEE International Reliability Physics Symposium (IRPS), 2022, pp. 3B.3-1-3B.3-5