© 2023 The Author(s). Published by Trans Tech Publications Ltd, Switzerland.

# Lifetime Projection of Bipolar Operation of SiC DMOSFET

Submitted: 2022-09-05

Accepted: 2022-11-11

Online: 2023-06-05

Christian Schleich<sup>1,2,a\*</sup>, Maximilian W. Feil<sup>3,b</sup>, Dominic Waldhör<sup>2,c</sup>, Aleksandr Vasilev<sup>1,2,d</sup>, Tibor Grasser<sup>2,e</sup> and Michael Waltl<sup>1,2,f</sup>

<sup>1</sup>Christian Doppler Laboratory for Single Defect Spectroscopy at the

<sup>2</sup>Institute for Microelectronics, TU Wien, Austria

<sup>3</sup>Infineon Technologies AG, Neubiberg, Germany

<sup>a</sup>schleich@iue.tuwien.ac.at, <sup>b</sup>Maximilian.Feil@infineon.com, <sup>c</sup>waldhoer@iue.tuwien.ac.at, <sup>d</sup>vasilev@iue.tuwien.ac.at, <sup>e</sup>grasser@iue.tuwien.ac.at, <sup>f</sup>waltl@iue.tuwien.ac.at

Keywords: Charge Trapping, Non-Radiative Multi-Phonon Model, Bias Temperature Instabilities

**Abstract.** We show the superior threshold voltage  $V_{\rm th}$  and on resistance  $R_{\rm on}$  stability of a SiC DMOS technology at bipolar gate-drive operation. Therefore, the defect parameters of a two-state non-radiative multi-phonon model to capture the charge trapping kinetics of oxide and interface defects is calibrated within our simulation framework Comphy by data extracted from measure-stress-measure (MSM) sequences. An extrapolation of the device degradation at operating conditions renders bias temperature instabilities (BTI) a minor threat to on-state loss increase.

## Introduction

A widely-known characteristic of planar SiC DMOSFET power switches is their bipolar gate driving operation with a small negative off-state gate bias  $V_G$  [1]. By employing physical modeling, we show that it reduces the long-term shift of both the threshold voltage  $\Delta V_{th}$  and the on-state resistance  $\Delta R_{on}$ .

These parameter drifts, commonly described under the term bias temperature instabilities (BTI), originate mainly from perturbations of the channel electrostatics due to accumulation of charge trapped at defects near the channel/oxide interface. A detailed understanding of the charge trapping kinetics and its temperature and  $V_{\rm G}$  dependence is vital for predicting the impact of BTI, i.e. device stability, at time-scales and operating conditions not easily accessible by experiments. Therefore, we employ a two-state non-radiative multi-phonon (NMP) model [2] as implemented in our simulation environment Comphy [3]. This framework relies on physical material and defect parameters and hence captures the charge trapping dynamics in considerable detail, while also allowing to extrapolate the  $V_{\rm th}$  degradation of SiC MOSFETs to end-of-lifetime for arbitrary operating conditions [4, 5]. Here, we investigate the charge trapping dynamics leading to the superior stability at bipolar  $V_{\rm G}$  operation which results in minor static on-state loss enhancement, even after as long as 10 years.

### **Simulation**

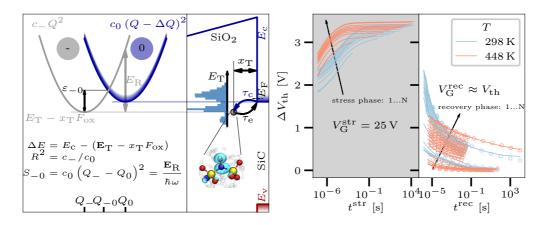

Within our model, the two defect charge states are treated as classical one-dimensional harmonic oscillators as depicted in Figure 1. The capture  $\tau_{\rm c}$  ( $V_{\rm G},T$ ) and emission  $\tau_{\rm e}$  ( $V_{\rm G},T$ ) time constants are then determined by activation energy barriers given by the intersection point of the potential energy curves (PECs). A large data set measured on a commercially available DMOSFET [6] consisting of long-term DC and short-term AC MSM sequences is used to extract defect parameters by employing an efficient, effective single defect decomposition (ESiD) algorithm [7]. Together with a regularization scheme it yields defect parameters ( $E_{\rm T}, E_{\rm R}$ ), c.f. Figure 1, and densities ( $N_{\rm T}$ ) that are within physical bounds as defined by ab-initio computations for likely defect candidates. Details about the used material parameters and calibration of device electrostatics are provided in [5].

Fig. 1: PECs of a defect for its "0" and "-" state are shown together with the extracted  $E_{\rm T}$  distribution. The energy barriers  $\varepsilon_{\rm 0-/-0}$  determine  $\tau_{\rm c/e}$  (left). MSM data (circles) is interpolated by the Comphy simulation (lines) using the ESiD method for optimized defect parameter extraction (right).

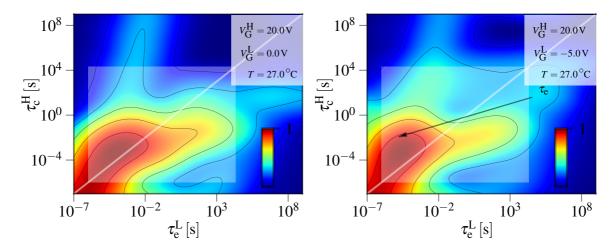

Figure 1 shows the resulting long-term DC  $\Delta V_{\rm th}$  data for standard operating conditions and accelerated  $V_{\rm G}$  and T stress conditions. Defect properties have been extracted for defect bands accounting for interface/near-interface traps (NITs) and border traps [5]. The former exhibit fast and symmetrical  $\tau_{\rm c}$  and  $\tau_{\rm e}$ , that are responsible for the majority of fast degrading and recovering  $\Delta V_{\rm th}$ . The  $(\tau_{\rm e}, \tau_{\rm c})$  distributions for unipolar operation are presented in a capture emission time (CET) map [8] in Figure 2, showing a strong asymmetry of  $\tau_{\rm c}$  and  $\tau_{\rm e}$ , which leads to hysteresis in the transfer characteristics  $(I_{\rm D}(V_{\rm G}))$  [9]. By applying a negative off-state bias  $V_{\rm G}^{\rm L}$ , the  $\tau_{\rm c}$  and  $\tau_{\rm e}$  distribution is shifted towards faster  $\tau_{\rm e}$ , as can be seen in Figure 2.

Fig. 2: A CET map at unipolar gate bias operation shows a wide distribution of  $\tau_c(V_G^H)$  and  $\tau_e(V_G^L)$  (left). The experimental time window is highlighted (white). The CET map with bipolar  $V_G$  shows a shift towards faster  $\tau_e$  of the electron traps which is the responsible mechanism for the reduced overall degradation (right).

#### Results

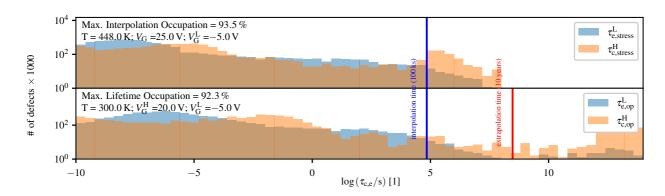

In Figure 3 the fraction of defects with  $\tau_c$  within the experimental window at the applied stress conditions is shown to be larger than the fraction of defects that can be charged after up to 10 years at operating  $(V_G, T)$ , which justifies the extrapolation up to this period. The computed parameter extrapolation employing an analytical expression for defect occupation for AC gate signals [3] shows the improved stability for bipolar  $V_G$  compared to unipolar AC operation. The  $\Delta R_{\rm on}$  shown in Figure 4 as a function of the overdrive voltage  $V_{\rm ov} = V_{\rm G} - V_{\rm th,0}$  has been derived from an initially measured  $I_{\rm D}(V_{\rm G})$

Fig. 3: A histogramm of  $\tau_{\rm c}$  ( $V_{\rm G}^{\rm H}$ ) and  $\tau_{\rm e}$  ( $V_{\rm G}^{\rm L}$ ) at stress conditions (**top**) shows a larger occupation of defects after the interpolation time, compared to a 10 year extrapolation at operation ( $V_{\rm G}, T$ ) (**bottom**) (compare  $\tau_{\rm c}$ ). Therefore, the acceleration due to stress (increased ( $V_{\rm G}, T$ )) justifies the extrapolation at operation conditions.

curve with a minor dependence on the sweep time, start and end bias, and method of the measurement, e.g. pulsed or continuous, as discussed in [10]. However, for  $\Delta R_{\text{on}}$ , this difference is negligible

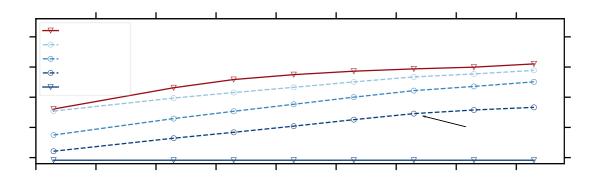

Fig. 4:  $\Delta V_{\rm th}$  and  $\Delta R_{\rm on}$  show about 30 % reduced static on-state losses after 10 years of bipolar AC operation, compared to the unipolar AC mode at a duty cycle of d=0.5. The readout gate bias  $V_{\rm G}^{\rm read}$  and time-delay  $t^{\rm read}$  after stress to calculate  $V_{\rm th}$  and  $R_{\rm on}$  are selected to comply with fast experimental drain current extraction.

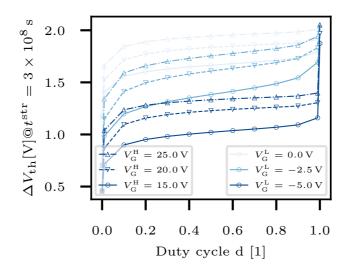

at the recommended  $V_G$  (given in [6]). Note that, even after 10 years, the  $\Delta R_{\rm on}$  leads to less than 30 % on-state loss increase, at  $\Delta V_{\rm th} > 1$  V. Finally, the duty cycle dependence of  $\Delta V_{\rm th}$  given in Figure 5 shows good stability over the whole range, except for the DC operation points, exhibiting only minor differences for modified conversion gate drive voltage pulse widths compared to Figure 4.

#### Summary

In summary, our calibrated simulations predict an on-state loss reduction of about 30 % at bipolar  $V_{\rm G}$  operation compared to using unipolar  $V_{\rm G}$  gate-drive signals. These results render BTI induced degradation under the recommended operation conditions a minor power conversion efficiency threat.

Fig. 5: Duty cycle dependence of  $\Delta V_{\rm th}$  is shown for the same readout parameters as in Figure 4, with stable  $\Delta V_{\rm th}$  over d, and lowest degradation for  $V_{\rm G}^{\rm L}=-5~{\rm V}$ .

# Acknowledgment

The financial support by the Austrian Federal Ministry of Labour and Economy, the National Foundation for Research, Technology and Development and the Christian Doppler Research Association is gratefully acknowledged.

#### References

- [1] J. Rice and J. Mookken: SiC MOSFET Gate Drive Design Considerations in IEEE IWIPP (2015)

- [2] T. Grasser: Stochastic charge trapping in oxides: From Random Telegraph Noise to Bias Temperature Instabilities in Microelectronics Reliability Vol. 52 (2012), p. 39-70, doi:10.1016/j.microrel.2011.09.002

- [3] G. Rzepa, J. Franco, B. O Sullivan, A. Subirats, M. Simicic, G. Hellings, P. Weckx, M. Jech, T. Knobloch, M. Waltl, P.J. Roussel, D. Linten, B. Kaczer and T. Grasser: *Comphy A Compact-Physics Framework for Unified Modeling of BTI* in Microelectronics Reliability Vol. 85 (2018), p. 49-65, doi:10.1016/j.microrel.2018.04.002

- [4] C. Schleich, J. Berens, G. Rzepa, G. Pobegen, G. Rescher, S. Tyaginov, T. Grasser and M. Waltl: *Physical Modeling of Bias Temperature Instabilities in SiC MOSFETs* in IEEE IEDM (2019), doi:10.1109/IEDM19573.2019.8993446

- [5] C. Schleich, D. Waldhoer, K. Waschneck, M. W. Feil, H. Reisinger, T. Grasser and M. Waltl: Physical Modeling of Charge Trapping in 4H-SiC DMOSFET Technologies in IEEE Transactions on Electron Devices Vol. 68 (2021), p. 4016-4021, doi:10.1109/TED.2021.3092295

- [6] Cree Inc., Silicon Carbide Power MOSFET C2M TM MOSFET Technology Datasheet, C2M0280120D (2015)

- [7] D. Waldhoer, C. Schleich, J. Michl, B. Stampfer, K. Tselios, E. G. Ioannidis, H. Enichlmair, M. Waltl and T. Grasser: *Toward Automated Defect Extraction From Bias Temperature Instability Measurements* in IEEE Transactions on Electron Devices Vol. 68 (2021), p. 4057-4063, doi:10.1109/TED.2021.3091966

- [8] K. Puschkarsky, T. Grasser, T. Aichinger, W. Gustin and H. Reisinger: *Understanding and modeling transient threshold voltage instabilities in SiC MOSFETs* in IEEE IRPS (2018), doi:10.1109/IRPS.2018.8353560

- [9] A. Vasilev, M. Jech, A. Grill, G. Rzepa, C. Schleich, A. Makarov, G. Pobegen, T. Grasser, M. Waltl and S. Tyaginov: *Modeling the Hysteresis of Current-Voltage Characteristics in 4H-SiC Transistors* in IEEE IIRW (2020)

- [10] M. Feil, A. Huerner, K. Puschkarsky, C. Schleich, T. Aichinger, W. Gustin, H. Reisinger and T. Grasser: *The Impact of Interfacial Charge Trapping on the Reproducibility of Measurements of Silicon Carbide MOSFET Device Parameters* in Crystals vol. 10 (2020), doi:10.3390/cryst10121143