# **Bias-Induced Instability of 4H-SiC CMOS**

Submitted: 2022-08-23

Revised: 2022-10-17

Online: 2023-06-06

Accepted: 2022-11-25

Yu-Xin Wen<sup>1,a\*</sup>, Bing-Yue Tsui<sup>1,b</sup>

<sup>1</sup>Institute of Electronics, National Yang Ming Chiao Tung University, Hsinchu, Taiwan, R.O.C. <sup>a</sup>wennew.ee08@nycu.edu.tw, <sup>b</sup>bytsui@nycu.edu.tw

Keywords: Silicon carbide (SiC), Bias temperature instability (BTI), Post-oxidation annealing (POA).

**Abstract.** 4H-SiC complementary metal-oxide-semiconductor (CMOS) devices for control circuit applications have been reported extensively, however, the electrical stability, even with interface optimization processes, degrades significantly after bias stress. In this paper, we performed both positive and negative bias stress on planar SiC NMOSFETs and PMOSFETs fabricated with pure (non-diluted) and N<sub>2</sub>-diluted NO post-oxidation annealing (POA) processes. The test results indicate the existence of positive hole traps might be the culprit that leads to electrical characteristics instability during operation and pure NO annealing is effective to reduce the instability.

#### Introduction

Silicon carbide (SiC), with the nature of wide bandgap, relative lower dielectric constant, and high thermal conductivity, has the potential to fabricate power devices operating at high power, high frequency and high temperature environment [1]. For high-frequency operation of the power system, the control circuit for the SiC power switch should be fabricated with SiC devices as well to reduce system volume size and parasitic power loss. Monolithic integration of both high-power device and control circuit is an effective way to reduce the volume of the power system and the power loss due to parasitic components between power device and control circuit. Several SiC CMOS circuits have been reported in literatures [2-6]. Recently, integration of both vertical power MOSFET and CMOS gate buffer on a single SiC chip has been reported [7, 8]. Though with normal switching operation controlled by low-voltage SiC CMOS devices, the reliability of the CMOS devices has not been disclosed.

Despite the promising material properties, SiC MOSFETs still suffer from low channel mobility and reliability concern due to high interface state density and carbon related defects which only exist in the SiO<sub>2</sub>/SiC interface [9-11]. Previous studies reported the electrical stability of SiC-MOSFETs degrade greater and faster while recover back faster than observed in Si-MOSFETs [12, 13]. This phenomenon might due to defects with fast emission/slow capture time constant existed at the interface of the SiC trench MOSFETs. Recently, comprehensive reliability test on 4H-SiC N/PMOSFET under bias stress test had been conducted [14]. The results from negative bias on PMOSFET and positive bias on NMOSFET shows improved stability with thermal and ultrathin CVD oxide and diluted N<sub>2</sub>O POA process. However, the large threshold voltage shift after bias stress suggests that the passivation of interface traps might be insufficient and the microscopic mechanism of the electrical characteristics drift still remains unknown. To clarify the mechanism behind and further improve the interface quality we performed bias stress on two gate oxides with different POA conditions.

## **Experimental Conditions**

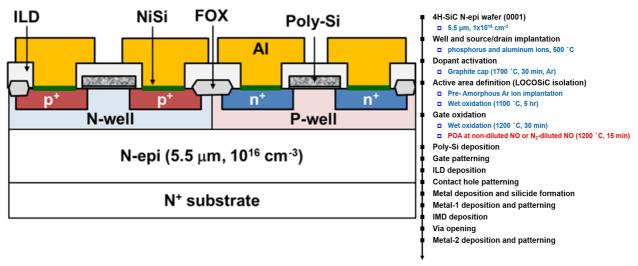

Fig. 1 (a) shows the schematic structure of the CMOS process. N- and P-channel MOSFETs were fabricated on n-type 4° off-axis (0001) 4H-SiC epi-wafers with epitaxial layer doping concentration and thickness of  $1 \times 10^{16}$  cm<sup>-3</sup> and 5.5  $\mu$ m respectively. Well and source/drain regions were then formed with Al and P ion implantations at 500 °C, followed by a dopant activation annealing at 1700 °C for 30 min with carbon cap in Ar ambient. For device isolation, we employed LOCOSiC isolation structure through Ar ion implantation and a wet oxidation at 1100 °C for 5 hr [15, 16]. The gate oxide was grown by wet oxidation at 1200 °C for 30 min followed by two kinds of POA process:

pure (non-diluted) NO annealing or N<sub>2</sub>-diluted NO annealing at 1200 °C for 15 min. The gate oxide thickness is about 20 nm from ellipsometer measurement. The main process flow is shown in Fig. 1 (b).

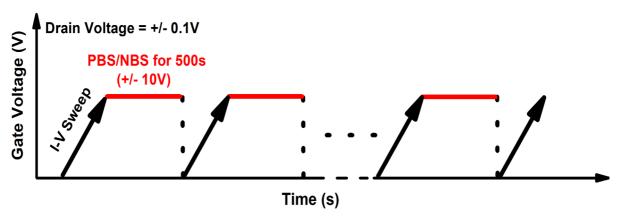

Conventional measure-stress-measure (MSM) test sequence is shown in Fig. 2. The test started with a pre-stress bias step before the first measurement to alleviate the effect from intrinsic defect. Then I-V sweep measurement and bias stress were the two steps that repeated.

#### **Results and Discussion**

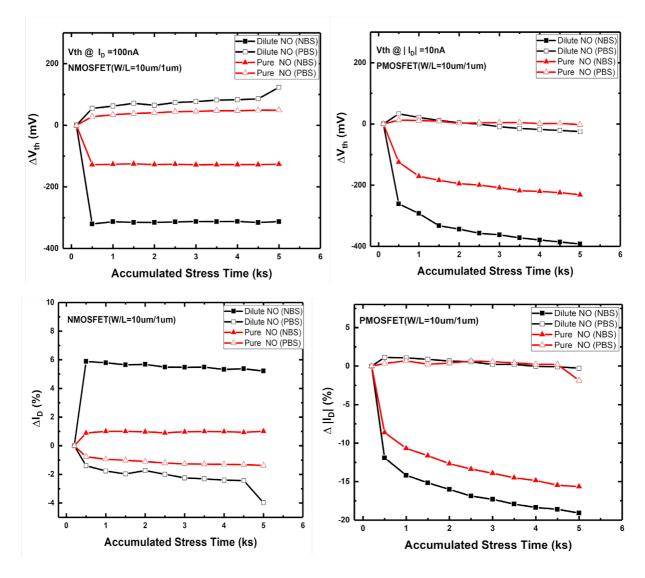

After the test sequence, the threshold voltage shift ( $\Delta V_{th}$ ) and drain current degradation ( $\Delta I_D$ ) are extracted and shown in Fig. 3. The  $\Delta V_{th}$  as well as  $\Delta I_D$  are minor for devices with pure NO annealing process. Adequate amount of NO annealing was suggested to be effective in passivating carbon interstitials which act as hole traps [10, 17]. Still, under -10 V stress condition (NBS) both POA conditions exhibit significant negative  $\Delta V_{th}$  and the  $\Delta I_D$  increases for NMOSFET while decreases for PMOSFET. In contrary, there is no significant  $\Delta V_{th}$  and  $\Delta I_D$  under positive bias stress (PBS) condition. The negative  $\Delta V_{th}$  indicates the existence of positive trap charges created during the stress period and the stress-induced trapping hardly emission after 500 s of stress. Under NBS, there are large number of holes accumulated at the SiO<sub>2</sub>/SiC interface, part of them tunneled through the barrier of the interface and were trapped in SiO<sub>2</sub> and thus leading to negative  $\Delta V_{th}$  and  $\Delta I_{D}$  for PMOSFET. Based on the above phenomena, the electrical characteristics drift might be caused by hole traps in SiO<sub>2</sub>, which were lower in the pure NO-annealed sample and started to saturate after NBS for 500 s. Since holes are harder to tunnel into SiO<sub>2</sub> than electrons but the results show minor drift under PBS, which indicates that a large number of hole traps existing in gate oxide. The estimated hole trap densities (D<sub>HT</sub>) are  $1.36 \times 10^{11}$  and  $4.22 \times 10^{11}$  cm<sup>-2</sup> for pure NO and diluted NO annealed samples, respectively, from the result of  $\Delta V_{th}$ .

Fig. 1. (a) Schematic cross-sectional structure of the N/PMOSFET. (b) Main process flow and POA split conditions of the N/PMOSFETs in this work.

Fig. 2. Conventional measure-stress-measure (MSM) test sequence to study the bias instability. I-V sweep from 0 to  $\pm$ 10 V for N/PMOSFETs for measurement. Positive or negative bias stress of  $\pm$ 10 V for 500 s per cycle on the gate for stressing.

Fig. 3. Threshold voltage shift ( $\Delta V_{th}$ ) and drain current degradation ( $\Delta I_D$ ) of 1- $\mu$ m-long SiC N/PMOSFETs under positive bias stress (open symbol) or negative bias stress (filled symbol) with N<sub>2</sub>-diluted NO annealing sample (black squares), pure-NO annealing sample (red triangles).

### Summary

According to the above results, hole trap might be the most possible defect that leads to electrical characteristics instability during operation. Furthermore, pure NO annealing is effective to reduce the instability. Clearly, there is still room for further optimization that passivate more amount of the defect, but thermal budget of the NO annealing process is crucial to balance the defect passivation and creation.

## Acknowledgement

This work was supported by the Ministry of Science and Technology, Taiwan, R. O. C. under the contract No. MOST 110-2218-E-A49-008.

#### References

- [1] X. She, A. Q. Huang, Ó. Lucía and B. Ozpineci, "Review of Silicon Carbide Power Devices and Their Applications," in IEEE Transactions on Industrial Electronics, vol. 64, no. 10, pp. 8193-8205, Oct. 2017.

- [2] K. Sheng, Y. Zhang, M. Su, J. H. Zhao, X. Li, P. Alexandrov, L. Fursin, "Demonstration of the first SiC power integrated circuit," Solid State Electronics, vol. 52, no. 10, pp. 1636-1646, Oct. 2008.

- [3] M. Alexandru, V. Banu, X. Jorda, J. Montserrat, M. Vellvehi, D. Tournier, J. Millan, and P. Godignon, "SiC Integrated Circuits Control Electronics for High Temperature Operation," IEEE Trans. on Industrial Electronics, vol. 62, no. 5, pp. 3182-3191, May. 2015.

- [4] A. Rahman et al., "High-Temperature SiC CMOS Comparator and Op Amp for Protection Circuits in Voltage Regulators and Switch-Mode Converters," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 4, no. 3, pp. 935-945, Sept. 2016.

- [5] M. Albrecht, T. Erlbacher, A. J. Bauer, and L. Frey, "Improving 5V Digital 4H-SiC CMOS ICs for Operating at 400°C Using PMOS Channel Implantation," Materials Science Forum, vol. 963, pp. 827-831, July. 2019.

- [6] J. Y. Jiang, J. C. Hung, K. M. Lo, C. F. Huang, K. Y. Lee, and B. Y. Tsui, "Demonstration of CMOS Integration with High-Voltage Double-Implanted MOS in 4H-SiC," IEEE Electron Device Lett., vol. 42, no. 1, pp. 78-81, Jan. 2021.

- [7] M. Okamoto, A. Yao, H. Sato and S. Harada, "First demonstration of a monolithic SiC power IC integrating a vertical MOSFET with a CMOS gate buffer", Proc. 33rd Int. Symp. Power Semiconductor Devices ICs (ISPSD), pp. 71-74, May 2021.

- [8] B. Y. Tsui, C. L. Hung, T. K. Tsai, Y. C. Tsui, T. W. Wang, Y. X. Wen, C. P. Shih, J. C. Wang, L. J. Lin, C. H. Wang, K. W. Chu, and P. H. Chen, "First Integration of 10 V CMOS Logic Circuit, 20 V Gate Driver, and 600 V VDMOSFET on a 4H-SiC Single Chip," in Proc. of the 34th IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp.321-324, 2022.

- [9] C. J. Cochrane, P. M. Lenahan and A. J. Lelis, "An electrically detected magnetic resonance study of performance limiting defects in SiC metal oxide semiconductor field effect transistors", J. Appl. Phys., vol. 109, no. 1, 2011.

- [10] D. P. Ettisserry, N. Goldsman, A. Akturk and A. J. Lelis, "Structure, bonding, and passivation of single carbon-related oxide hole traps near 4H-SiC/SiO2 interfaces", J. Appl. Phys., vol. 116, pp. 174502, Nov. 2014.

- [11] T. Kobayashi and Y. Matsushita, "Structure and energetics of carbon defects in SiC (0001)/SiO 2 systems at realistic temperatures: Defects in SiC SiO 2 and at their interface ", J. Appl. Phys, vol. 126, pp. 145302, 2019.

- [12] K. Puschkarsky, H. Reisinger, T. Aichinger, W. Gustin and T. Grasser, "Understanding BTI in SiC MOSFETs and Its Impact on Circuit Operation," in IEEE Transactions on Device and Materials Reliability, vol. 18, no. 2, pp. 144-153, June 2018.

- [13] T. Aichinger, G. Rescher and G. Pobegen, "Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs", Microelectron. Rel., vol. 80, pp. 68-78, Jan. 2018.

- [14] XE. K. Ashik et al., "Bias Temperature Instability on SiC n- and p-MOSFETs for High Temperature CMOS Applications," 2022 IEEE International Reliability Physics Symposium (IRPS), 2022, pp. 3B.4-1-3B.4-8.

- [15] Y.-H. Tseng, C.-Y. Lin and B.-Y. Tsui, "Characterization of LOCOS Field Oxide on 4H-SiC Formed by Ar Preamorphization Ion Implantation," in IEEE Electron Device Letters, vol. 38, no. 6, pp. 798-801, June 2017.

- [16] B. -Y. Tsui, T. -K. Tsai, Y. -T. Lu, J. -H. Lin, C. -L. Hung and Y. -X. Wen, "A Study on the Isolation Ability of LOCal Oxidation of SiC (LOCOSiC) for 4H-SiC CMOS Process," in IEEE Transactions on Electron Devices, vol. 68, no. 12, pp. 6644-6647, Dec. 2021,

- [17] B. -Y. Tsui, Y.-T Huang, T.-L. Wu, C.-H. Chien, "Time-dependent dielectric breakdown of gate oxide on 4H-SiC with different oxidation processes," in IEEE Microelectronics Reliability, vol. 123, 114186, Aug. 2021.