© 2025 The Author(s). Published by Trans Tech Publications Ltd, Switzerland.

# Thick Semi-Insulating 4H-SiC Layer Exfoliation for Non-Epitaxial Engineered Substrates

Submitted: 2024-09-19

Accepted: 2025-04-08

Online: 2025-09-04

Hitesh Jayaprakash<sup>1,2,3,a\*</sup>, Constantin Csato<sup>1,b</sup>, Robert Koch<sup>2,c</sup>, Florian Krippendorf<sup>1,d</sup>, Michael Rueb<sup>1,2,e</sup>

<sup>1</sup>mi2-factory GmbH, Moritz-von-Rohr Str. 1a, 07745 Jena, Germany

<sup>2</sup>Ernst-Abbe-Hochschule Jena, Carl-Zeiss-Promenade 2, 07745 Jena, Germany

<sup>3</sup>Friedrich-Alexander-Universität, Cauerstr. 6, 91058 Erlangen, Germany

<sup>a</sup>hitesh.jayaprakash@eah-jena.de, <sup>b</sup>constantin.csato@mi2-factory.com,

<sup>c</sup>Robert.Koch@eah-jena.de, <sup>d</sup>florian.krippendorf@mi2-factory.com,

<sup>e</sup>michael.rueb@mi2-factory.com

**Keywords:** Semi-Insulating 4H-SiC, Layer transfer, Ion slicing, Engineered substrates

Abstract. The growing demand for 4H-SiC substrates in power device fabrication has encouraged the development of engineered substrates to reduce costs and facilitate wafer re-usability for effective material utilization. This work presents a novel approach for manufacturing SiC power devices is to exfoliate the required drift layer thickness from ultra-high-quality Semi Insulating (SI) 4H-SiC material, bond it to a conductive SiC substrate and thus obtain the non-epitaxial engineered substrate. Energy-filtered Ion Implantation (EFII) technology enables custom doping profiles, precise control of doping concentration, and potentially robust material properties compared to as-grown epitaxial layers in the bonded layer. Key steps to exfoliate a 4µm thick SiC layer from semi-insulating substrates and bond it to low-cost, highly conductive mono-crystalline SiC are demonstrated. This paper mainly focuses on the physical characterization of demonstrated samples.

## Introduction

To meet the growing demand for 4H-SiC as a next-generation wide band-gap semiconductor and accelerate power device production, novel substrates are needed to reduce production time and manufacturing costs without compromising device characteristics. Currently, epi-ready substrates [1, 2] rely on traditional epitaxial growth methods to grow the voltage-sustaining layer, a crucial step in the fabrication of power devices [3]. SiC-epitaxy is a complex process and requires regular maintenance to achieve uniform doping profiles and material quality in mass production. An alternate solution is to use the novel non-epitaxial engineered substrates introduced in our previous work [4] to fabricate SiC power devices without the need for epitaxy using on-axis SI 4H-SiC. There are several advantages of having the voltage sustaining layer oriented on-axis, <0001>. 1. Trench MOSFETs do not need the 4° tilted trench etch to maximise the channel mobility on c-plane {0001} [5, 6]. 2. There exist a possible choice of Si-face or C-face for application specific power device. 3. There is also a possibility to achieve Hu profile [7] for achieving minimum ohmic-resistance and highest breakdown voltage. These profiles can be tailor made by utilizing the choice of doping technology described further.

The proposed non-epitaxial engineered substrate could be a promising alternative to current epiready substrates if the donor material, doping technology and wafer bonding methods are carefully selected. First, vanadium-free, high-quality semi-insulating (SI) 4H-SiC is chosen as the donor material for the voltage-sustaining layer to avoid unwanted trap levels in the band structure. This material has been used in power devices for JFET operations [8]. Second, Energy Filtered Ion Implantation (EFII) is used to implant box profiles in this layer [9, 10], replacing conventional drift zone doping done via epitaxy. For layer exfoliation of donor wafers, ion slicing with proton implantation [11, 12] is the suitable method among many methods [13–18], as it allows precise control of layer thickness and achieves surface roughness close to a few nanometers after exfoliation. Lastly, wafer bonding needs to provide a seamless bond with minimal electrical resistance, using a

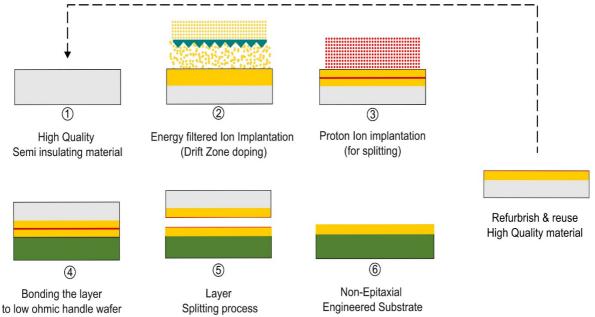

low-temperature process to preserve the proton concentration for exfoliation. Oxide-free hydrophobic direct bonding [19] with surface activation at room temperature must be chosen over more common hydrophilic bonding [20]. The process flow is illustrated in the Fig. 1

**Fig. 1.** Illustration of the novel non-epitaxial engineered substrate technology for 4H-SiC power device fabrication. This high quality donor wafer can be used multiple times.

Previous attempts to exfoliate and bond thick SiC layers have failed. This paper details the necessary process steps required to obtain non-epitaxial engineered substrates demonstrated on a chip scale of 20x20mm area. The physical effects of proton implantation on the SiC chips like surface bow, surface roughness, exfoliated layer thickness and bond interface investigations are done. This approach eliminates the need for epitaxy in conventional SiC power device fabrication and is scalable to 200mm SiC technology.

## **Experimental Approach**

Two 6-inch, commercially available on-axis (SI) 4H-SiC wafers were chosen from our previous study [4], these wafers had the lowest density of BPD per volume and the surface roughness of <0.5nm RMS on Si-face was critical for bonding applications. A wafer was implanted with a 5E15cm-3 box profile on the Si-face up to a depth of 8.35µm with Nitrogen using EFII technology and activation annealed at 1700°C for 30 minutes. The implanted wafer served as a doped SI material for the study and the other as an undoped SI material. These samples were prepared to demonstrate that the exfoliation process is suitable for both types of material. Furthermore, wafers were cut into 20x20mm chips to study the critical proton dose requirement and suitable heat treatment parameters to exfoliate the layer from the surface of the chip using ion slicing technique.

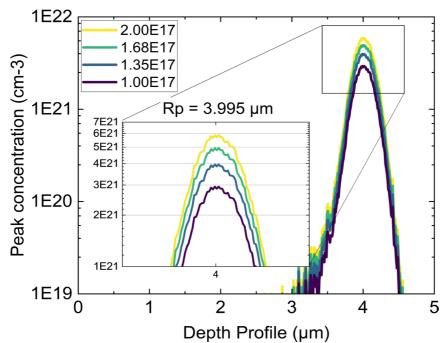

For this study, proton energy of 500 KeV was used which has a projected range of 4µm, that implies 4µm thick layers can be exfoliated from the chip. Based on previous work, to exfoliate the thin layer in the SiC [21–26] at lower proton energies, peak concentration was estimated to be in the range of 3E21-6E21 cm-3 for successful layer exfoliation. GEANT4 simulations were performed to obtain the corresponding maximum concentration for proton implants in the range of 1E17-2E17 cm-2 dose as shown in Fig. 2. The chips were then categorized according to material type, labeled and implanted with proton dose as per the Table. 1.

All these chips were implanted with 500 KeV proton with maximum available tilt angle of 7° at the implanter to avoid channelling on the Si-face. After proton implants, one set of chips were subjected to blister tests to find the optimum exfoliation parameters for heat treatment while the other set were chosen for layer transfer with bonding experiments. Tube furnace with Ar ambient was utilized for both blister tests and bonding tests. The heat treatment parameters, including the critical temperature,

**Table 1.** 500 KeV proton implantation doses and corresponding peak concentrations obtained using GEANT4 simulation in 4H-SiC substrates.

|       | Implanted Dose       | Effective Peak Concentration |

|-------|----------------------|------------------------------|

| Label | $[\mathrm{cm}^{-2}]$ | [cm <sup>-3</sup> ]          |

| S     | 1.00E17              | 3E21                         |

| M     | 1.35E17              | 4E21                         |

| L     | 1.68E17              | 5E21                         |

| U     | 2.00E17              | 6E21                         |

**Fig. 2.** GEANT4 simulation of ion stopping and range to obtain effective peak concentration for implant doses of proton at 500 KeV energy into 4H-SiC material.

optimal hold times and ramp rate to promote Ostwald ripening process was studied [22]. These tests are critical to find the parameters that promote blister formation, which is crucial for the exfoliation process.

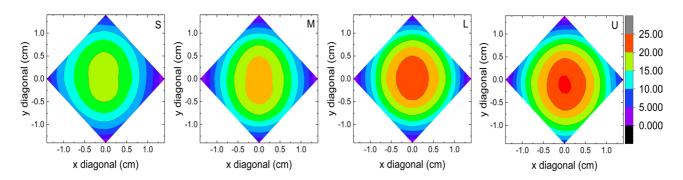

**Blister test:** Chips selected for blister tests underwent heat treatment at two different hold temperatures at 836°C (T1) and 872°C (T2) with the maximum possible ramp (6°K/min) temperature of the used furnace. T1 was chosen as the minimum activation temperature for blister formation from the arrhenius plot from previous work [25] and higher temperature T2 to enable higher activation rates for blistering. A duration of 30 and 60 minute as hold time at T1 and T2 was tested individually to obtain adequate time for ripening process. The physical aspects of the chip after high proton dose implants were

**Fig. 3**. The physical effect of high dose proton implantation on 20x20mm chips, where bow of 25μm is observed on the highest dose of 2E17 cm-2. Note the measurement points are on the diagonals and the surface is interpolated contour plot from interferrometric measurements.

studied. Convex bow is observed on the implanted chip surface as illustrated in Fig. 3. Similar convex wafer surface can be expected on 6-inch full wafers too with higher magnitude in accordance with previous studies [27]. The blister test results, layer thickness and surface roughness measurement are discussed in the results section.

**Bonding experiments:** The successful process parameters obtained from the blister tests were used for the bonding experiments. Four bond chip pairs as described in Table. 2 were stuck to a 6-inch Si wafer for handling purpose with kapton tape. The bond equipment MWB-06/08-AX [28] was used for room temperature bonding under ultra high vacuum with in-situ Surface Activation Bonding (SAB) using Ar in Fast Atomic Beam (FAB) gun [29, 30]. An attempt to bond exfoliated SiC to Si chip was also done with Silicon Sputtered Bonding (SSB). Further, bonded layer thickness, surface roughness and cross-section of bond interface with FIB were studied and compared with the blister test results.

#### **Results and Discussion**

Blister tests: With regards to the proton dose requirement for both doped and undoped material, a dose of 1.68E17 cm-2 is suitable for exfoliating 4µm thick layers efficiently. Treating the chips at 836°C which is 3°C higher than the minimum theoretical activation temperature [25], can be used to compensate temperature tolerance errors in the furnaces. Blisters were noticeable for 30 minutes hold time. 60 minutes hold time at T1 did not have any notable difference. Temperature T2 or longer hold times could improve bond strength and diffuse residual hydrogen at the bond interface as noted from earlier studies [31]. The N-doped SI SiC layer showed less curling than undoped SI, indicating lower internal stress compared to bulk substrates. This may be due to the 1700°C activation anneal after N implantation with EFII. The test results are summarized in Fig. 4.

|                   | 836°C 30 minutes  |                 | 836°C 60 minutes  |                 | 872°C 30 minutes  |                 | Result /                             |

|-------------------|-------------------|-----------------|-------------------|-----------------|-------------------|-----------------|--------------------------------------|

| H+ Dose<br>(cm-2) | Undoped<br>SI-SiC | Doped<br>SI-SiC | Undoped<br>SI-SiC | Doped<br>SI-SiC | Undoped<br>SI-SiC | Doped<br>SI-SiC | Description                          |

| U<br>2.00E17      | THETH             |                 |                   | A Japan         | 3                 |                 | OK /<br>Explosive<br>blisters        |

| L<br>1.68E17      | LL3B0             |                 | 08843             | 41917           | LH3B0             |                 | OK /<br>Efficient<br>Blistering      |

| M<br>1.35E17      | ML3B0             |                 | MLGEQ             | ML681           | ORCHA             | MHSB1           | OK /<br>Uniform<br>small<br>blisters |

| S<br>1.00E17      | SL380             | SL3B1           | 038JS             | SL681           | SH3B0             | SH381           | Fail /<br>No blisters<br>seen        |

**Fig. 4.** Results of blister test at different blister parameters like proton dose, heat treatment temperature and ripening time on undoped SI 4H-SiC and doped SI 4H-SiC chips. The minimum dose requirement for a thick 4μm layer blistering is 1.35E17 cm-2. Darker layers are exfoliated SiC and lighter regions are bare substrate underneath.(some dark regions in S row are reflection on the chips)

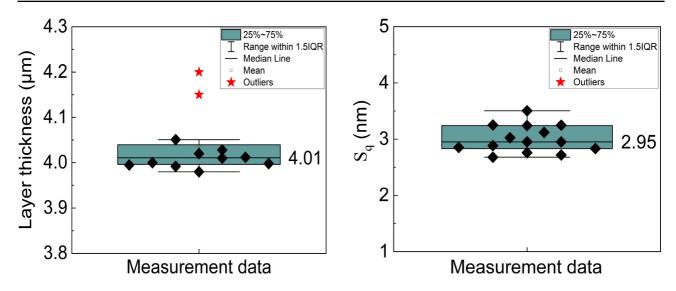

Fig. 5 shows consistent results for exfoliated SiC layer thickness and surface roughness across multiple samples. However, some samples did not exfoliate uniformly throughout the chip area, likely due to the channeling effect during proton implantation, causing lower peak concentration at the projected range. A 7° tilt is insufficient to avoid channeling in on-axis SiC. An optimal anti-channeling angle for on-axis [0001] in 4H-SiC must be used during proton implantation to ensure uniform exfoliation [32, 33].

Fig. 5. The blister test measurements promises repeatability of the ion slicing process. *left* shows the median layer thickness of 4.01  $\mu$ m obtained corresponding to the simulated 4  $\mu$ m, for 500KeV proton implants in SiC. *right* shows the area surface roughness (Sq) of a 80x80  $\mu$ m area is also consistent at a median of 2.95 nm.

**Table 2.** The bond pairs involved, undoped and nitrogen-doped SI 4H-SiC (exfoliation layer) from the donor chips, bonded to N-type SiC and Si as acceptor chip. Bonding results, immediately after bonding and post-exfoliation at 836°C for 60 minutes, are tabulated.

| Bond | Donor chip     | Proton | Acceptor   | FAB type | Pressure | Result (as | Result     |

|------|----------------|--------|------------|----------|----------|------------|------------|

| Pair | material       | dose   | Chip       |          | welding  | bonded)    | (after     |

|      |                |        | _          |          | _        | ·          | splitting) |

| 1    | Undoped SI SiC | M      | N-type SiC | SAB      |          | Failed     | -NA-       |

| 2    | Undoped SI SiC | L      | N-type SiC | SAB      | 10 MPa   | Success    | Success    |

| 3    | Doped SI SiC   | L      | N-type SiC | SAB      |          | Success    | Success    |

| 4    | Doped SI SiC   | L      | N-Type Si  | SAB      |          | Success    | Failed     |

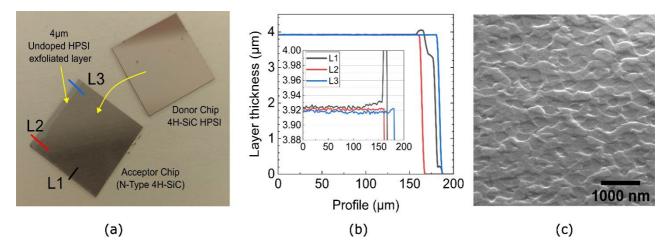

**Bonding experiments:** The bonding experiments results are summarized in the Table. 2 and bond pair 2 image is illustrated in Fig.6a. Due to kapton particle contamination during surface activation step, bond pair 1 failed. Whilst other chips with surface activation bonding were successful. Even the SiC and Si chips were bonded. But during the heating procedure to exfoliate the layers, SiC-Si bond failed due to CTE mismatch. The bond pair 2 and 3 were successful and the exfoliated layer showed robust bond strength even at 872°C for 30 minutes. The layer thickness of 3.92μm was measured with interferrometer as shown in the profile plots of Fig. 6b. The surface roughness (Sq) of the exfoliated surface were measured to be ~3 nm and surface morphology from SEM image is shown in Fig. 6c. Further, plasma assisted polishing [34, 35] provides smooth surface for power device fabrication.

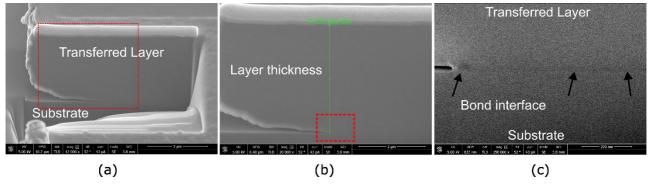

The FIB cross-section measurements on bond pair 3 shown in Fig. 7 also reveals 4µm layer bonded seamlessly to the N-type SiC substrate with interface thickness of <20 nm pre-reactivation anneal. This is a necessary step after bonding to re-activate the dopants after proton implants [36]. The measured value in FIB cross-section Fig. 7b is slightly higher than the interferrometric measurements due to measurement artifact in the tool. These thickness measurements on bonded layers are in accordance with the layer thickness measured after blistering tests. The reduction of 80nm is expected due to the surface cleaning process and the surface activation step before bonding the chips. These results also reveal that the critical peak concentration of hydrogen in 4H-SiC needs to be >3E21 cm-3 for blistering and >4E21 cm-3 for optimum exfoliation of layers. Due to furnace malfunction during 1700°C reactivation annealing, bonded SiC chips were completely oxidized and destroyed. Hence,

bond characterization of the bond interface after high temperature anneal was not performed. Our future work includes scaled up demonstration of this technology on a full 6-inch wafer with further electrical characteristics of the novel non-epitaxial substrates.

**Fig. 6.** (a) A 20x20 mm chip was successfully bonded and exfoliated from a donor SI 4H-SiC onto an N-type 4H-SiC substrate. (b) Profile plots of L1, L2, and L3 show a uniform 3.92 μm layer thickness across the chip surface. (c) SEM image of the 5x5 μm exfoliated area reveals a rough surface topology, requiring polishing.

**Fig. 7.** FIB cross-section images results indicating the seamless bond interface after exfoliating the layer. Regions marked in red are zoomed in successive images. (a) at the edge of the bonded layer. (b) measured layer thickness. (c) Seamless bond interface (enhanced contrast for visibility)

### **Summary**

For the first time, exfoliating a thick 4μm semi insulating 4H-SiC layer and successfully bonding it to a SiC substrate is demonstrated over an area of 20x20mm. This study showcases that for 4μm thick layer exfoliation, peak proton concentration >4E21 cm-3 must be reached at 500 KeV energy followed by the heat treatment greater than 836°C for 30 minutes to sufficiently exfoliate thick layers. Bonding SiC-SiC material is also made possible by using in-situ surface activation bonding at ultra high vacuum under room temperature. However, particle contamination plays an important role in bonding step, hence least particle contamination must be maintained for void free bonding. This technology offers optimal accesibility for exfoliating non-epitaxial layers of thickness upto 15μm for power device fabrication corresponding to the voltage class of 2 KV.

#### Acknowledgement

All ion implantations were conducted at the Ion Beam Center of Helmholtz-Zentrum Dresden-Rossendorf (HZDR), standard dopant activation annealing was performed at Fraunhofer-Institut für Integrierte Systeme und Bauelementetechnologie (IISB), Erlangen and bonding tests were performed in cooperation with Nidec Machine Tool with MWB-06/08-AX (WR017) machine. Thanks to Oliver Rüger for preparing the cross-sections and SEM images at Institut für Festkörperphysik Jena.

#### References

- [1] Wolfspeed. *N-Type SiC Substrates*. https://www.wolfspeed.com/products/materials/ n-type-sic-substrates/. Accessed: 2024-09-02. 2024.

- [2] Soitec. SmartSiC<sup>TM</sup> for Automotive Applications. https://www.soitec.com/en/products/ auto-smartsic. Accessed: 2024-09-02. 2024.

- [3] Séverin Rouchier et al. "150 mm SiC Engineered Substrates for High-Voltage Power Devices". In: *Materials Science Forum* 1062 (2022), pp. 131–135.

- [4] Hitesh Jayaprakash et al. "Study on Estimation of Device Yield in Non-Epitaxial 4H-SiC Material Relating to Defect Densities Influencing Bipolar Degradation with XRT-Measurements". In: *Solid State Phenomena* 344 (2023), pp. 53–57.

- [5] Ralf Siemieniec et al. "A SiC Trench MOSFET concept offering improved channel mobility and high reliability". In: 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe). 2017, P.1–P.13.

- [6] Dethard Peters et al. "Performance and ruggedness of 1200V SiC Trench MOSFET". In: 2017 29th International Symposium on Power Semiconductor Devices and IC's (ISPSD). IEEE, 2017, pp. 239–242. ISBN: 978-4-88686-094-1.

- [7] Chenming Hu. "Optimum doping profile for minimum ohmic resistance and high-breakdown voltage". In: *IEEE Transactions on Electron Devices* 26 (1979), pp. 243–244. URL: https://api.semanticscholar.org/CorpusID:36831640.

- [8] M. Kaneko and T. Kimoto. "High-Temperature Operation of n- and p-Channel JFETs Fabricated by Ion Implantation Into a High-Purity Semi-Insulating SiC Substrate". In: *IEEE Electron Device Letters* 39.5 (2018), pp. 723–726.

- [9] Constantin Csato et al. "Energy filter for tailoring depth profiles in semiconductor doping application". In: Nuclear Instruments and Methods in Physics Research Section B: Beam Interactions with Materials and Atoms 365 (2015), pp. 182–186.

- [10] Roland Rupp et al. "Alternative Highly Homogenous Drift Layer Doping for 650 V SiC Devices". In: *Materials Science Forum* 858 (2016), pp. 531–534.

- [11] L. Di Cioccio et al. "Silicon carbide on insulator formation by the Smart-Cut® process". In: *Materials Science and Engineering: B* 46.1 (1997), pp. 349–356.

- [12] M. Levy et al. "Fabrication of single-crystal lithium niobate films by crystal ion slicing". In: *Applied Physics Letters* 73.16 (1998), pp. 2293–2295.

- [13] Bing Hu et al. 2018 International Flexible Electronics Technology Conference (IFETC): 7-9 Aug. 2018. Piscataway, NJ: IEEE, 2018. ISBN: 9781538633571.

- [14] Marko Swoboda et al. "Laser Assisted SiC Wafering Using COLD SPLIT". In: *Materials Science Forum* 897 (2017), pp. 403–406.

- [15] David J. Meyer et al. "Epitaxial Lift-Off and Transfer of III-N Materials and Devices from SiC Substrates". In: *IEEE Transactions on Semiconductor Manufacturing* 29.4 (2016), pp. 384–389.

- [16] Stephen W. Bedell et al. "Layer transfer by controlled spalling". In: *Journal of Physics D: Applied Physics* 46.15 (2013), p. 152002.

- [17] J. A. Bennett et al. "Complete surface exfoliation of 4H–SiC by H+- and Si+-coimplantation". In: *Applied Physics Letters* 76.22 (2000), pp. 3265–3267.

- [18] Shifei Han et al. "Laser slicing of 4H-SiC wafers based on picosecond laser-induced micro-explosion via multiphoton processes". In: *Optics & Laser Technology* 154 (2022), p. 108323.

- [19] Jian Li et al. "Direct bonding of silicon carbide with hydrofluoric acid treatment for high-temperature pressure sensors". In: *Ceramics International* 46.3 (2020), pp. 3944–3948.

- [20] Fengxuan Wang et al. "Low-Temperature Direct Bonding of SiC to Si via Plasma Activation". In: *Applied Sciences* 12.7 (2022), p. 3261.

- [21] J. Grisolia et al. "Kinetic aspects of the growth of hydrogen induced platelets in SiC". In: *Journal of Applied Physics* 87.12 (2000), pp. 8415–8419.

- [22] L.-J. Huang et al. "Onset of blistering in hydrogen-implanted silicon". In: *Applied Physics Letters* 74.7 (1999), pp. 982–984.

- [23] R. B Gregory, O.W Holland, D.K. Thomas, T.A Wetterroth, S.R Wilson. "The effect of Damage on Hydrogen-implant-induced thin-film seperation from Bulk Silicon Carbode." In: *Mat. Res. Soc. Symp. Proc.* 572 (1999), pp. 33–38.

- [24] V. P. Amarasinghe et al. "Properties of H + Implanted 4H-SiC as Related to Exfoliation of Thin Crystalline Films". In: *ECS Journal of Solid State Science and Technology* 3.3 (2014), P37–P42.

- [25] Voshadhi Pansilu Amarasinghe. "Single Crystalline Silicon Carbide Thin Film Exfoliation for Power Device Applications". Ph.D. Dissertation. Graduate School-New Brunswick Rutgers, The State University of New Jersey, 2015.

- [26] Madan Sharma et al. "Blistering kinetics in H-implanted 4H-SiC for large-area exfoliation". In: *Current Applied Physics* 31 (2021), pp. 141–150.

- [27] Volker Häublein and Heiner Ryssel, eds. *IIT 2018 proceedings: 2018 22nd International Conference on Ion Implantation Technology, September 16-21, 2018, Congress Centrum, Würzburg, Germany.* Piscataway, NJ: IEEE, 2018. ISBN: 9781538668290.

- [28] Nidec Machine Tool Corporation. *Room Temperature Wafer Bonding Machine BOND MEISTER*. https://www.nidec.com/en/machine-tool/products/B701/M102/S100/ NMTJ-wafer bonding machine/. Accessed: 2024-08-30.

- [29] Kensuke Ide et. al. "Wafer Bonder Applicable to Devices in Various Fields, Mitsubishi Heavy Industries Technical Review Vol.48 No.1(2011)". In: *Mitsubishi Heavy Industries Technical Review* 48.1 (2011), pp. 48–52.

- [30] et. al. S. Langa. "Room Temperature bonding for Vacuum applications: Climatic and long time tests". In: (2004).

- [31] Zheng Cui. "Wafer Bonding". In: *Encyclopedia of Microfluidics and Nanofluidics*. Ed. by Dongqing Li. Boston, MA: Springer US, 2013, pp. 1–7.

- [32] J. Wong-Leung et al. "Ion implantation in 4H–SiC". In: *Nuclear Instruments and Methods in Physics Research Section B: Beam Interactions with Materials and Atoms* 266.8 (2008), pp. 1367–1372.

- [33] Manuel Belanche et al. "Aluminum channeling in 4H-SiC by high-energy implantation above 10 MeV". In: *Materials Science in Semiconductor Processing* 179 (2024), p. 108461.

- [34] Kazuya Yamamura et al. "High-Integrity Finishing of 4H-SiC (0001) by Plasma-Assisted Polishing". In: *Advanced Materials Research* 126-128 (2010), pp. 423–428.

- [35] K. Yamamura et al. "Plasma assisted polishing of single crystal SiC for obtaining atomically flat strain-free surface". In: *CIRP Annals* 60.1 (2011), pp. 571–574.

- [36] Guillaume Gelineau et al. "Evaluation of Crystal Quality and Dopant Activation of Smart CutTM Transferred 4H-SiC Thin Film". In: *Materials Science Forum* 1089 (June 2023), pp. 71–79.