# Investigation of Interface and Reliability of 3C- and 4H-SiC MOS Structures through Gate Dielectric Stacking and Post-Deposition Annealing

Submitted: 2024-09-20

Revised: 2025-08-06

Online: 2025-09-08

Accepted: 2025-08-06

Mustafa Akif Yildirim<sup>1,a\*</sup>, Vishal Ajit Shah<sup>1,b</sup>, Marina Antoniou<sup>1,c</sup>, Andrew Newton<sup>2,d</sup>, Sami Bolat<sup>3,e</sup>, Gerard Colston<sup>1,f</sup>, Andrew Graham<sup>1,g</sup>, Richard Jefferies<sup>1,h</sup>, James A. Gott<sup>4,i</sup>, Kushani Perera<sup>1,j</sup>, Michael J. Powell<sup>2,k</sup>, Peter M. Gammon<sup>1,l</sup>, Philip A. Mawby<sup>1,m</sup>, Robert Gunn<sup>2,n</sup>, Arne Benjamin Renz<sup>1,o</sup>

<sup>1</sup>School of Engineering, University of Warwick, Coventry, UK

<sup>2</sup>Oxford Instruments Plasma Technology, Bristol, UK

<sup>3</sup>Hitachi Energy Semiconductors Switzerland Ltd, Lenzburg, Switzerland

<sup>4</sup>Warwick Manufacturing Group, University of Warwick, Coventry, UK

<sup>a</sup>mustafa.yildirim@warwick.ac.uk, <sup>b</sup>Vishal.Shah@warwick.ac.uk, <sup>c</sup>Marina.Antoniou@warwick.ac.uk, <sup>d</sup>andrew.newton@oxinst.com, <sup>e</sup>sami.bolat@hitachienergy.com, <sup>f</sup>G.Colston.1@warwick.ac.uk, <sup>g</sup>Andrew.Graham.1@warwick.ac.uk, <sup>h</sup>Richard.Jefferies@warwick.ac.uk, <sup>i</sup>J.gott@warwick.ac.uk, <sup>j</sup>Kushani-Hapuhinna.Perera@warwick.ac.uk, <sup>k</sup>michael.powell@oxinst.com, <sup>l</sup>P.M.Gammon@warwick.ac.uk, <sup>m</sup>P.A.Mawby@warwick.ac.uk, <sup>n</sup>robert.gunn@oxinst.com, <sup>c</sup>Arne.Renz@warwick.ac.uk

Keywords: high-k dielectrics, atomic layer deposition, post-deposition annealing

Abstract. This study investigates the interface and reliability of metal-oxide-semiconductor capacitors (MOSCAPs) based on 3C-SiC and 4H-SiC using atomic layer deposition (ALD) and postdeposition annealing (PDA). SiO<sub>2</sub> and HfO<sub>2</sub>/SiO<sub>2</sub> were used as dielectric layers, with systematic PDA treatments conducted at 600°C, 900°C, and 1100°C in N2 or forming gas (FG, a mixture of H2 and N<sub>2</sub>) environments to evaluate the impact of the PDA conditions on the interface characteristics of SiC MOSCAPs. The flat-band voltage for 3C-SiC MOSCAPs averaged at  $0.68 \pm 0.05$  V for SiO<sub>2</sub>/3C-SiC/Si samples and  $2.35 \pm 0.01$  V for HfO<sub>2</sub>/SiO<sub>2</sub>/3C-SiC samples when MOSCAPs annealed at 1100°C in FG. PDA in forming gas also significantly reduced hysteresis, dropping from 1.75 V to 0.18 V for SiO<sub>2</sub>/3C-SiC and from 2.49 V to 0.04 V for HfO<sub>2</sub>/SiO<sub>2</sub>/3C-SiC samples. For 4H-SiC MOSCAPs, as-deposited devices exhibited high oxide charges and poor interface quality. The average flat-band voltages for SiO<sub>2</sub>/4H-SiC were  $9.01 \pm 0.15$  V, while HfO<sub>2</sub>/SiO<sub>2</sub> MOSCAPs showed  $6.65 \pm 0.02$  V. After PDA at 1100°C, the flat-band voltage improved to  $-0.65 \pm 0.035$  V for SiO<sub>2</sub>/4H-SiC and  $-0.50 \pm 0.05$  V for HfO<sub>2</sub>/SiO<sub>2</sub>/4H-SiC. Additionally, hysteresis was reduced from 0.61 V to 0.15 V for SiO<sub>2</sub>/4H-SiC and from 0.23 V to 0.05 V for HfO<sub>2</sub>/SiO<sub>2</sub>/4H-SiC samples. We propose a figure of merit (FOM) which is defined as the ratio of the breakdown field to the product of flatband voltage shift, hysteresis effect, and density of interface states. The results demonstrate that PDA significantly enhances the interface quality and electrical characteristics of the MOS capacitors (MOSCAPs), with nitrogen (N<sub>2</sub>) PDA yielding higher FOM for 4H-SiC stacks and forming FG PDA showing superior interfacial quality for 3C-SiC stacks.

#### Introduction

In 2019, emissions from transportation, including aviation fuels, accounted for 25.9% of the overall greenhouse gas emissions in the European Union-27 [1]. Transition to electric vehicles, and improving their power electronics efficiency, is one of the best choices to decelerate global warming and reduce the effects of climate change. Due to their superior physical and electrical properties, silicon carbide (SiC)-based metal oxide semiconductor field-effect transistors (MOSFETs) have become commercially competitive with silicon insulated-gate bipolar transistors (IGBTs) in power

applications requiring blocking voltages between 600V and 1700V [2, 3]. One major challenge that reduces the yield and long-term reliability, hence the further uptake of the technology, is a high density of interface states at the SiO<sub>2</sub>/SiC interface, which is typically two to three orders of magnitude higher than in Si-based counterparts [4, 5].

Although SiC is the only compound semiconductor that can form a native SiO<sub>2</sub> layer by consuming the SiC during thermal oxidation, this process differs from the thermal oxidation of Si. During the oxidation of SiC, Si reacts with O<sub>2</sub> to form SiO and SiO<sub>2</sub> products. Then the removal of the resultant carbon from the SiC must be considered. When the initially grown oxide is thin, the carbon in the matrix reacts and diffuses out in products of CO, CO<sub>2</sub> and CO<sub>x</sub>. However, as the layer becomes thicker (>25nm) the diffusion of these products through the oxide and outside the oxide/atmosphere surface becomes limited. There has been evidence showing residual carbon near or at the SiC/SiO<sub>2</sub> interface, with strong evidence of high interface densities thereby low channel mobilities of SiC MOSFETs [6, 7]. Alternative deposition methods for SiC gate dielectrics are particularly appealing, as they prevent substrate consumption and avoid leaving excess carbon atoms, effectively addressing this issue. Due to its ability to provide highly accurate control over thickness (typically within a few angstroms), uniformity, reproducibility, and conformal deposition, atomic layer deposition (ALD) has emerged as a favoured method for depositing gate dielectrics on 4H-SiC [8]. ALD operates by sequentially introducing pairs of gaseous chemical precursors into a reaction chamber.

Gauss's law expresses the electric field in an insulator to an adjacent semiconductor by the following equation:

$$E_{ins} = \frac{\kappa_s}{\kappa_{ins}} E_s$$

Eq. 1

$$C = \frac{\kappa \epsilon_o A}{t_{ox}}$$

where  $E_s$  is the electric field in the semiconductor  $\kappa_s$  and  $\kappa_{ins}$  are the dielectric constant of the semiconductor and insulator, respectively [4], [7]. The dielectric constant of SiO<sub>2</sub> is approximately 2.5 times lower than the dielectric constant of SiC. This causes the breakdown of SiO<sub>2</sub> first in SiO<sub>2</sub>/SiC-based devices hence, preventing SiC from reaching its full potential. Equation 1 suggests that using insulators with a dielectric constant similar to or greater than that of SiC would be ideal for minimizing electrical stress in SiC-based electronics. As shown in Equation 2, using a high-κ material allows for the same or even greater capacitance with a physically thicker dielectric layer. Having a thicker dielectric layer helps to reduce leakage current, which in turn improves reliability and helps maintain the desired performance. In this equation,  $\varepsilon_0$  represents the permittivity of free space, A is the area of the capacitor, and tox denotes the thickness of the dielectric layer [9]. This initiates an investigative effort into the utilization of high-k dielectrics as the gate dielectric layer in silicon carbide (SiC) based electronic devices. Some of the properties of an ideal dielectric for SiC should be as follows. The dielectric should have low fixed and mobile oxide charges and low density of fixed and mobile interface states. Moreover, the dielectric should have a high breakdown field, a large energy band gap, a high dielectric constant, and a high band offset with SiC to minimise leakage current. Despite having several reported studies of high- κ dielectrics-SiC with good electrical properties [5, 10-12]. High leakage current still is a huge hampering factor. To resolve this problem scientists proposed a high- κ material with a thin SiO<sub>2</sub> layer to have an initial large band offset in high-κ/SiO<sub>2</sub>/SiC structures.

Oxide deposition techniques such as atomic layer deposition (ALD) and low-pressure chemical vapour deposition (LPCVD) have already been shown to offer a solution to improve control of the interface and circumvent SiC-specific defects, such as carbon clusters, which are inherent in industry-standard thermal oxidation processes [8]. Post-deposition anneals (PDAs) of ALD-deposited SiO<sub>2</sub> layers in forming gas (FG) mixture of H<sub>2</sub>-N<sub>2</sub> and N<sub>2</sub> have had a positive impact on both mobility and reliability [8, 13].

In this investigation, we further explore the effect of PDAs on ALD-formed dielectric stacks on 3C-SiC and 4H-SiC MOS-capacitors (MOSCAPs). The dielectric stacks, comprising SiO<sub>2</sub> and HfO<sub>2</sub>/SiO<sub>2</sub> underwent PDAs across a temperature range from 600°C to 1100°C in either pure N<sub>2</sub> or a forming gas (5% H<sub>2</sub> in N<sub>2</sub>). The ALD as-deposited SiO<sub>2</sub>/4H-SiC and HfO<sub>2</sub>/SiO<sub>2</sub>/4H-SiC MOSCAPs exhibit a high oxide charge and poor interface quality, which are significantly enhanced after undergoing a PDA process. In contrast, the ALD as-deposited 3C-SiC MOSCAPs show slightly better initial interface characteristics compared to their 4H-SiC counterparts, and they too display notable improvements following the PDA treatment. Interface characteristic metrics such as interface state density, flatband voltage shift, hysteresis, and breakdown voltages in the annealed samples are analyzed to assess the improvements brought by the PDA process. To evaluate the overall quality of the MOSCAPs, a figure of merit (FOM) is proposed, defined as the ratio of the breakdown field to the product of the flatband voltage shift, hysteresis, and interface state density. Our analysis revealed that PDA in N<sub>2</sub> ambient produces higher figures of merit (FOM) for the 4H-SiC MOSCAPs, while FG PDA results in higher FOMs for the 3C-SiC MOSCAPs, indicating better interfacial quality in the latter.

### **Experimental Details**

4H-SiC wafers with low-doped epilayers and 3C-SiC epilayers grown on highly doped Si wafers were cleaved into approximately 1 cm x 1 cm chip-sized samples. The 3C-SiC epilayers are 3 µm thick with unintentional doping, while the 4H-SiC epilayers are 9.7 µm thick with intentional doping of 2×10<sup>15</sup> cm<sup>-3</sup>. The detailed growth process can be found here[14]. Cleaved samples then underwent a solvent clean (acetone, isopropyl alcohol and deionised water), and RCA process (Hydrofluoric acid (HF), RCA-1, HF, RCA-2 and HF). Then samples were loaded into a plasma-enhanced ALD chamber to deposit dielectrics. SiO<sub>2</sub> and HfO<sub>2</sub> were deposited using oxygen plasma at 200°C, with Bis(DiEthylAmido)Silane (BDEAS) as the silicon precursor and Tetrakis(dimethylamido)Hafnium (TDMAH) as the hafnium precursor. The growth rate for SiO<sub>2</sub> was approximately 0.05 nm per cycle, while the HfO<sub>2</sub> growth rate was around 0.1 nm per cycle. After the deposition of the dielectric or stacked dielectric layers, the samples underwent selective annealing process, to investigate the effects of different ambient conditions. Annealing was performed under 5 standard liter per meter (slm) flow of forming gas (5% H<sub>2</sub> in N<sub>2</sub>) or in a pure N<sub>2</sub> atmosphere for 1 hour at temperatures of 600°C, 900°C, and 1100°C. This process was critical for studying the impact of the PDA on the material properties, as highlighted in previous work [8]. Table 1 illustrates the fabrication matrix of SiC MOSCAPs. A standard photolithography lift-off and metal deposition processes were applied to pattern Al dots with a thickness of 200 nm. Before backside metal contact the backsides of the wafers were etched to eliminate any native oxide layer.

**Table 1.** A comprehensive overview of the substrate materials, dielectric stack compositions, and post-deposition annealing conditions employed in the fabrication of SiC MOSCAPs.

#### Post-deposition annealing Post-deposition annealing **Substrate Dielectric Stack** temperature conditions ambient conditions SiO<sub>2</sub> (30 nm) 4H-SiC As-dep As-dep 3C-SiC $HfO_2/SiO_2$ (25nm/5nm) 600°C N<sub>2</sub> 900°C Forming Gas (5 % H<sub>2</sub> in N<sub>2</sub>) 1100°C

#### **Results and Discussion**

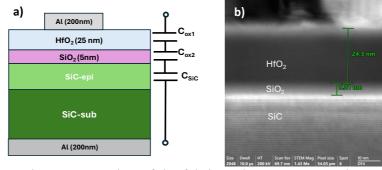

Figure 1(a) presents a schematic illustration of the fabricated HfO<sub>2</sub>\SiO<sub>2</sub>\4H-SiC MOSCAPs. The MOSCAPs with only a single SiO<sub>2</sub> layer had a 30 nm thick SiO<sub>2</sub> layer deposited, while those with HfO<sub>2</sub> included a 5 nm SiO<sub>2</sub> interfacial layer before the HfO<sub>2</sub> deposition. The thin SiO<sub>2</sub> layer is essential in reducing leakage current, as HfO<sub>2</sub> has a lower bandgap and, therefore, a smaller conduction band offset with SiC compared to SiO<sub>2</sub>, which can increase leakage. The higher conduction band offset of the SiO<sub>2</sub> layer acts as a barrier, effectively minimizing leakage while still allowing the HfO<sub>2</sub> to enhance capacitance [9, 15]. This combination significantly improves the overall performance of the MOSCAP. Figure 1(b) shows a TEM image of the thin intermediate SiO<sub>2</sub> (5.21 nm) layer and HfO<sub>2</sub> (24.3 nm) layer. MOSCAP structures.

Fig. 1. (a) Schematic representation of the fabricated MOSCAPs and associated circuitry. (b) Cross-sectional TEM image demonstrating the thickness of the HfO<sub>2</sub>\SiO<sub>2</sub> stack in the MOSCAP structures.

#### **Electrical Characterization**

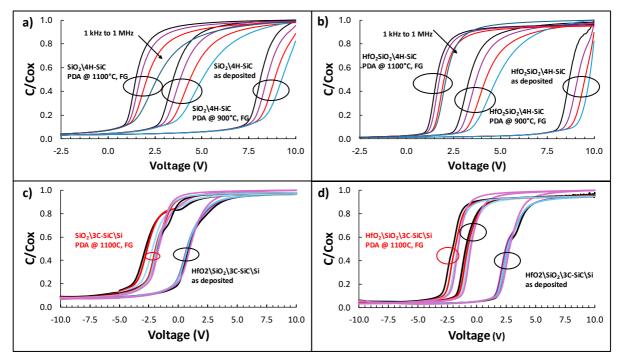

To further investigate the interface characteristics of the ALD-deposited dielectrics on 3C-SiC and 4H-SiC MOSCAPs, room temperature capacitance-voltage measurements were carried out. Figure 2 shows normalized C-V responses were taken from 12 devices at 1 kHz to 1 MHz frequencies.

**Fig. 2.** C-V curves of 4H-SiC a) and b) and 3C-SiC (c and d) MOS capacitors with different gate dielectric stacks annealed at various temperatures in FG gas ambient. The device area for each device is  $1.26 \times 10^{-3}$  cm<sup>2</sup>.

#### **4H-SiC MOSCAPs**

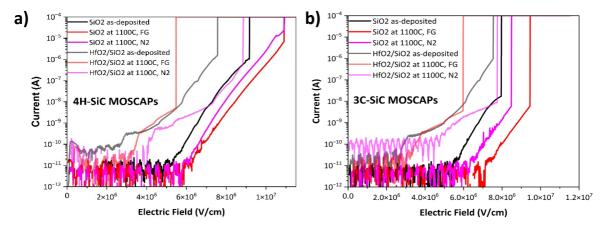

As-deposited 4H-SiC MOSCAPs with SiO<sub>2</sub> and HfO<sub>2</sub>\SiO<sub>2</sub> dielectric layers as the gate oxide typically exhibit significant quantities of net negative charge, both within the oxide and at the interface. This is reflected in their flat band voltages, with SiO<sub>2</sub> MOSCAPs averaging  $9.01 \pm 0.15$  V, while HfO<sub>2</sub>/SiO<sub>2</sub> MOSCAPs show a lower average of  $6.65 \pm 0.02$  V. Additionally, these devices do not display accumulation mode, suggesting a leaky oxide layer as it can be seen in figure 3. While the breakdown voltage of SiO<sub>2</sub> MOSCAPs improves with both FG and N<sub>2</sub> annealing, the breakdown voltage of HfO<sub>2</sub>/SiO<sub>2</sub> improves only with N<sub>2</sub> annealing. This phenomenon requires further investigation to elucidate the underlying factors influencing this behaviour. However, after annealing the devices at 600°C, 900°C, and 1100°C, the C-V curves begin to shift to the left, indicating passivation of the negative charges. Notably, after annealing, the capacitance of the device saturates entirely when they are swept into deep accumulation, further confirming improvements in the oxide quality. When annealed at 1100°C for 1 hour in forming gas (FG) ambient, the average flat-band voltages improved to  $-0.65 \pm 0.035$ V and  $-0.50 \pm 0.05$  V, reflecting a reduction in net negative charge for SiO<sub>2</sub>\4H-SiC and HfO<sub>2</sub>\SiO<sub>2</sub>\4H-SiC samples, respectively. In addition to improving the flat band voltage, annealing the 4H-SiC samples significantly reduces hysteresis. The hysteresis was notably reduced, improved from 0.61 V to 0.15 V for the SiO<sub>2</sub>/4H-SiC MOSCAPs, and from 0.23 V to 0.05 V for the HfO<sub>2</sub>/SiO<sub>2</sub>/4H-SiC MOSCAPs. Alongside the reduction in hysteresis, a low level of density of interface states (DIT) was obtained, which was extracted using the high-low C-V measurement method, with 300 Hz as low frequency and 1 MHz as high frequency. The density of interface states for 4H-SiC MOSCAPs averaged at  $1.14 \pm 0.16 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> for SiO<sub>2</sub>\4H-SiC and  $1.04 \pm 0.04 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> for HfO<sub>2</sub>\SiO<sub>2</sub>\4H-SiC at 0.2 eV below conduction band (Ec-E<sub>t</sub>=0.2 eV) after annealing at 1100°C in an N2 ambient.

## **3C-SiC MOSCAPs**

On the other hand, with a narrower band gap (2.3 eV), 3C-SiC has several advantages over 4Hand 6H-SiC: it requires a lower electric field for inversion and has a significantly lower trap density at the 3C-SiC/SiO<sub>2</sub> interface. Additionally, the high density of near-interface traps in the conduction band does not affect channel current, further improving the performance of 3C-SiC MOS structures compared to 4H-SiC. Furthermore, the larger conduction band offset at the 3C-SiC/SiO2 interface (3.7 eV), which even exceeds that of the Si/SiO<sub>2</sub> interface, suggests that 3C-SiC devices may offer greater reliability [15,16]. Consequently, as-deposited 3C-SiC samples exhibit strong accumulation, near-ideal flat band voltage, and narrower C-V curves between high and low frequencies as can be seen in Figures 2 c) and d). The flat band voltages were found to average at  $0.68 \pm 0.05$  Vand 2.35 ±0.01 V for SiO<sub>2</sub>\3C-SiC\Si and HfO<sub>2</sub>\SiO<sub>2</sub>\3C-SiC\Si samples, respectively. They showed similar behaviours compared to 4H-SiC samples post-annealing. When annealed at 1100°C for 1 hour in FG ambient, the average flat-band voltages shifted to -1.73  $\pm$  0.04 V and -1.86  $\pm$  0.06 V. Although annealing the 3C-SiC samples doesn't seem to improve the flat band voltages, it greatly reduces the hysteresis. The hysteresis effect was significantly improved, reducing from 1.75 V to 0.18 V for the  $SiO_2\3C-SiC\Si$  sample, and from 2.49 V to 0.04 V for  $HfO_2\SiO_2\3C-SiC\Si$  sample. 3C-SiC MOSCAPs, showed slightly better D<sub>IT</sub> values, achieving  $0.38 \pm 0.02 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> for  $SiO_2\3C-SiC\Si$  and  $0.85 \pm 0.05 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> for HfO<sub>2</sub>\SiO<sub>2</sub>\3C-SiC\Si at E<sub>C</sub>-E<sub>t</sub>=0.2 eV after annealing at 1100°C in an FG ambient, demonstrating enhanced interface characteristics.

**Fig. 3.** Current-Voltage Characteristics of MOSCAPs: (a) 4H-SiC and (b) 3C-SiC with SiO<sub>2</sub> or HfO<sub>2</sub>\SiO<sub>2</sub> as dielectric layer annealed at 1100°C in FG or N<sub>2</sub> ambient.

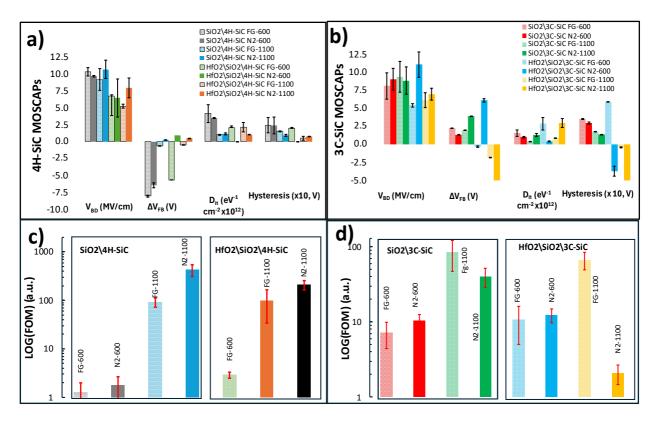

Figure 4 a) and Figure 4 b) present a summary of the extracted parameters, including the breakdown field ( $V_{BD}$ ), flatband voltage shift ( $\Delta V_{FB} = \phi_{ms}$  -  $V_{FB}$ , where  $\phi_{ms}$  is the difference between the metal and semiconductor work functions, and  $V_{FB}$  is the measured flatband voltage), hysteresis (H), and the density of interface states.

Fig. 4. a) and b) Summaries of extracted electrical parameters for the MOSCAPs, including breakdown field ( $V_{BD}$ ), flatband voltage shift ( $\Delta V_{FB}$ ), hysteresis (H), and the density of interface states ( $D_{IT}$ ). The hysteresis values scaled up 10 times. The density of interface states as measured at  $E_{C}$ - $E_{I}$ =0.2 eV c) and d) Final calculated figures of merit (FOMs) used to determine the optimal gate dielectric stack and post-deposition annealing (PDA) conditions for 3C-SiC and 4H-SiC MOSCAPs.

For an ideal dielectric or dielectric stack, certain characteristics are desired: a high breakdown field a minimal shift in flat band voltage from its ideal value, low D<sub>IT</sub>, and minimal hysteresis. To evaluate the overall quality of gate dielectrics, we propose a figure of merit (FOM) which shows the ratio of the breakdown field to the product of flat band voltage shift, hysteresis effect, and density of interface states:

$$FOM = V_{BD}/(\Delta V_{FB} * H * D_{it})$$

Eq.3

We propose this as a metric to help gauge the effectiveness of gate dielectrics. The final calculated FOMs to evaluate the optimum gate dielectric stack and PDA condition for 4H-SiC and 3C-SiC MOSCAPs are shown in Figures 4c) and 4d). In our analysis, we observed that the N<sub>2</sub> PDA yields higher figures of merit (FOM) for the 4H-SiC stacks, whereas FG PDA demonstrates higher FOMs, indicating superior interfacial quality, for the 3C-SiC stacks.

#### Conclusion

The investigation into the interface and reliability of 3C-SiC and 4H-SiC MOS structures through gate dielectric stacking and post-deposition annealing has yielded promising results. The use of ALD for depositing SiO<sub>2</sub> and HfO<sub>2</sub>\SiO<sub>2</sub> dielectrics, combined with PDA treatments, has proven to be an effective strategy for improving the quality of the SiO<sub>2</sub>\SiC interface. The optimized PDA conditions, which differ for 3C-SiC and 4H-SiC MOSCAPs, have led to a reduction in interface trap density, oxide charge, and hysteresis, while overall device performance. The proposed figure of merit (FOM) has been instrumental in determining the optimal dielectric stack and PDA conditions for each SiC polytype. The findings underscore the importance of material and process optimization in realizing the full potential of SiC technology in the fight against climate change and in the development of sustainable energy solutions.

#### Acknowledgements

The project "Innovations in Power MOSFET Gate technology through the use of ALD oxides" has received funding from Innovate UK / InnoSuisse call UK-Switzerland Bilateral: Collaborative R&D under project no. 10089219. The authors would like to thank Richard Jefferies and Andrew Graham from the cleanroom facility at the School of Engineering, University of Warwick, for their generous support during device fabrication and characterization.

#### References

- [1] Eea, "Transport and environment report 2022 Digitalisation in the mobility system: challenges and opportunities," doi: 10.2800/47438.

- [2] X. She, A. Q. Huang, O. Lucia, and B. Ozpineci, "Review of Silicon Carbide Power Devices and Their Applications," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 10, pp. 8193–8205, Oct. 2017, doi: 10.1109/TIE.2017.2652401.

- [3] C. Langpoklakpam *et al.*, "Review of Silicon Carbide Processing for Power MOSFET," Feb. 01, 2022, *MDPI*. doi: 10.3390/cryst12020245.

- [4] A. Siddiqui, R. Y. Khosa, and M. Usman, "High-k dielectrics for 4H-silicon carbide: present status and future perspectives," Apr. 21, 2021, *Royal Society of Chemistry*. doi: 10.1039/d0tc05008c.

- [5] P. Fiorenza, F. Giannazzo, and F. Roccaforte, "Characterization of SiO2/4H-SiC interfaces in 4H-SiC MOSFETs: A review," 2019, MDPI AG. doi: 10.3390/en12122310

- [6] S. T. Pantelides *et al.*, "Si/SiO<sub>2</sub> and SiC/SiO<sub>2</sub> Interfaces for MOSFETs Challenges and Advances," *Materials Science Forum*, vol. 527–529, pp. 935–948, Oct. 2006, doi: 10.4028/www.scientific.net/msf.527-529.935.

- [7] K. Zekentes and K. Vasilevskiy, "Advancing Silicon Carbide Electronics Technology II Core Technologies of Silicon Carbide Device Processing," 2020. [Online]. Available: http://www.mrforum.com

- [8] A. B. Renz *et al.*, "Development of high-quality gate oxide on 4H-SiC using atomic layer deposition," in *Materials Science Forum*, Trans Tech Publications Ltd, 2020, pp. 547–553. doi: 10.4028/www.scientific.net/MSF.1004.547.

- [9] G. D. Wilk, R. M. Wallace, and J. M. Anthony, "High-κ gate dielectrics: Current status and materials properties considerations," *J Appl Phys*, vol. 89, no. 10, pp. 5243–5275, May 2001, doi: 10.1063/1.1361065.

- [10] S. Tanimoto, "Highly reliable SiO2/SiN/SiO2(ONO) gate dielectric on 4H-SiC," *Electronics and Communications in Japan, Part II: Electronics (English translation of Denshi Tsushin Gakkai Ronbunshi)*, vol. 90, no. 5, pp. 1–10, May 2007, doi: 10.1002/ecjb.20329.

- [11] T. Hosoi *et al.*, "AlON/SiO2 stacked gate dielectrics for 4H-SiC MIS devices," in *Materials Science Forum*, Trans Tech Publications Ltd, 2009, pp. 541–544. doi: 10.4028/www.scientific.net/MSF.615-617.541.

- [12] H. Watanabe *et al.*, "(Invited) Impact of Stacked AlON/SiO 2 Gate Dielectrics for SiC Power Devices," *ECS Trans*, vol. 35, no. 2, pp. 265–274, Apr. 2011, doi: 10.1149/1.3568869.

- [13] A. B. Renz *et al.*, "Initial investigations into the MOS interface of freestanding 3C-SiC layers for device applications," *Semicond Sci Technol*, vol. 36, no. 5, May 2021, doi: 10.1088/1361-6641/abefa1.

- [14] G. Colston *et al.*, "Three-Dimensional Epitaxy of Low-Defect 3C-SiC on a Geometrically Modified Silicon Substrate," *Materials*, vol. 17, no. 7, Apr. 2024, doi: 10.3390/ma17071587.

- [15] F. Li, S. Qiu, M. Jennings, and P. Mawby, "Reliability study of mos capacitors fabricated on 3c-sic/si substrates," in *Materials Science Forum*, Trans Tech Publications Ltd, 2020, pp. 659–664. doi: 10.4028/www.scientific.net/MSF.1004.659.

- [16] A. Schöner, M. Krieger, G. Pensl, M. Abe, and H. Nagasawa, "Fabrication and characterization of 3C-SiC-based MOSFETs," *Chemical Vapor Deposition*, vol. 12, no. 8–9, pp. 523–530, Aug. 2006, doi: 10.1002/cvde.200606467.