# Impact of Silicon Nitride Stress on Defects Generation in 4H-SiC and the Effect of Sacrificial Oxidation on Defects Reduction

Submitted: 2024-09-04

Revised: 2025-08-04

Accepted: 2025-08-05 Online: 2025-09-08

Kai-Wen Hsu<sup>1,a\*</sup>, Huai-Lin Huang<sup>1,b</sup>, Chia-Lung Hung<sup>2,c</sup>, Yi-Kai Hsiao<sup>2,d</sup> and Bing-Yue Tsui<sup>1,e</sup>

<sup>1</sup>Institute of Electronics, National Yang Ming Chiao Tung University ED641, Ta-Hsueh Road, Hsinchu, Taiwan, R.O.C.

<sup>2</sup>Semiconductor Research Center, Hon Hai Research Institute, Taiwan, R.O.C.

<sup>a</sup>taroice.ee12@nycu.edu.tw, <sup>b</sup>lynnhuang3026.ee11@nycu.edu.tw, <sup>c</sup>kevin.cl.hung@foxconn.com djason.yk.hsiao@foxconn.com, <sup>e</sup>bytsui@nycu.edu.tw

**Keywords:** Schottky barrier diode, MOS Capacitor, Sacrificial Oxidation, Strain-induced damage, Silicon Nitride

**Abstract.** The impact of silicon nitride (Si<sub>3</sub>N<sub>4</sub>) stress on 4H-SiC has been investigated. Current-voltage (I-V) measurements on Schottky barrier diode show that Si<sub>3</sub>N<sub>4</sub> films thicker than 100 nm degrade both the ideality factor and Schottky barrier height. A 45-nm sacrificial oxidation effectively reduces defects from a 100-nm-thick Si<sub>3</sub>N<sub>4</sub> layer, but defects persist with films over 300 nm. Interface state density of metal oxide semiconductor capacitor with a 44-nm-thick gate oxide confirms the effectiveness of sacrificial oxidation in mitigating defects.

#### Introduction

Silicon nitride (Si<sub>3</sub>N<sub>4</sub>), renowned for its high strength, hardness, and excellent corrosion resistance, is commonly used in IC manufacturing, such as hard mask and diffusion barrier [1-2]. Previous studies have indicated that the stress induced by Si<sub>3</sub>N<sub>4</sub> at high temperatures may damage the Si surface [3]. Hence, a pad SiO<sub>2</sub> layer is deposited before the Si<sub>3</sub>N<sub>4</sub> layer to mitigate such effects, a practice also observed in SiC device fabrication [4]. However, there is scarce literature on the impact of Si<sub>3</sub>N<sub>4</sub> induced stress on SiC surfaces to support the necessity of pad SiO<sub>2</sub> on SiC. Therefore, we fabricated Schottky barrier diode (SBD) and metal oxide semiconductor capacitor (MOSCap) to assess whether Si<sub>3</sub>N<sub>4</sub> generates defects on SiC and to explore whether sacrificial oxidation can mitigate such issues.

#### **Device Fabrication**

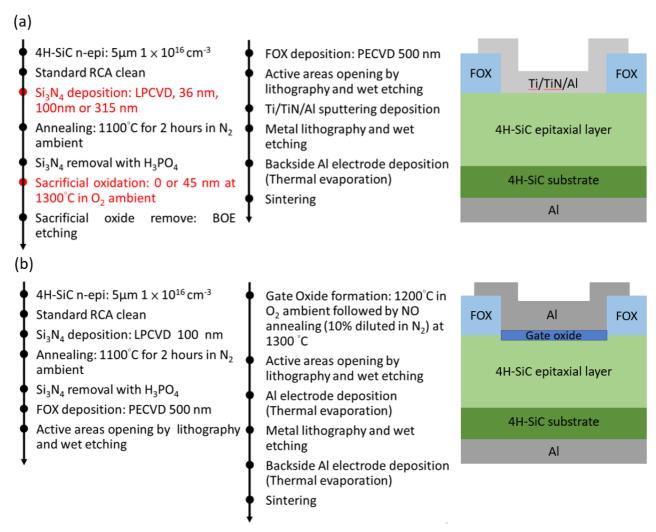

The main process flow of SBD is shown in Fig. 1(a). Sample ID and split conditions are listed in Table 1. All samples began with nitrogen-doped 4° off-axis 4H-SiC (0001) substrate with a 5.5-umthick epitaxial layer. The doping concentration of the epitaxial layer was  $1 \times 10^{16}$  cm<sup>-3</sup>. After standard RCA cleaning and a final diluted HF dip, Si<sub>3</sub>N<sub>4</sub> films with various thicknesses were deposited by a LPCVD (Low Pressure Chemical Vapor Deposition) system and subsequently annealed at 1100°C in N<sub>2</sub> ambient to simulate the LOCOSiC (LOCal Oxidation of SiC) process [5]. Some samples underwent a sacrificial oxidation (to a thickness of 45 nm) at 1300°C in O<sub>2</sub> ambient after Si<sub>3</sub>N<sub>4</sub> removal by hot H<sub>3</sub>PO<sub>4</sub>. After removing the sacrificial oxide layer, a 500-nm-thick PECVD SiO<sub>2</sub> layer was deposited as field oxide (FOX). Active areas were defined using photo lithography and wet etching processes. A Ti/TiN/Al stack was sputter-deposited, patterned and annealed at 500°C for 5minutes in vacuum to form Schottky contact for SBD [6]. We also fabricated MOSCap on samples without sacrificial oxidation. To grow gate oxide, thermal oxidation was conduct at 1200°C in O2 ambient for 140 minutes, followed by annealing at 1300°C in a NO ambient (10% NO diluted with N<sub>2</sub>). The capacitance equivalent thickness (CET) of gate oxide is approximately 44 nm. Aluminum was deposited by thermal evaporation and patterned to form the electrode for the MOS capacitor, and all samples finished with the backside aluminum electrode and 400°C sintering in N<sub>2</sub> ambient.

| Sample ID | Si <sub>3</sub> N <sub>4</sub> Thickness (nm) | Sacrificial Oxide<br>Thickness (nm) |

|-----------|-----------------------------------------------|-------------------------------------|

| Control   | 0                                             | 0                                   |

| N36S0     | 36                                            | 0                                   |

| N100S0    | 100                                           | 0                                   |

| N100S45   | 100                                           | 45                                  |

| N315S0    | 315                                           | 0                                   |

| N315S45   | 315                                           | 45                                  |

Table 1 Sample ID and split conditions

**Fig. 1** Main process flow and device structure of the (a)SBD (b)MOSCap. Red letters indicate the process step with split conditions.

#### **Experimental Results & Discussion**

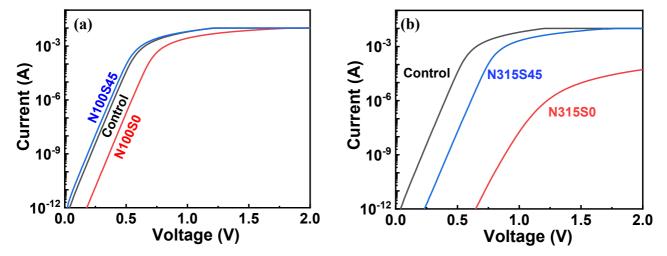

Fig. 2 shows the current-voltage (I-V) characteristics of the SBDs with 100-nm-thick and 315-nm-thick Si<sub>3</sub>N<sub>4</sub> layer, respectively. As the Si<sub>3</sub>N<sub>4</sub> layer was deposited directly on SiC substrate, thermal stress generated during the high-temperature process changed the I–V characteristics of the SBD. As shown in Fig. 2, this induced a noticeable rightward shift in the I–V curves, indicating an increase in the Schottky barrier height ( $\Phi_b$ ). The shift is more pronounced in the N315S0 sample compared to N100S0, suggesting that the extent of damage increases with increase of the thickness of the Si<sub>3</sub>N<sub>4</sub> layer. After applying a 45-nm-thick sacrificial oxidation process, the I–V curve of the N100S45 sample shifts back and closely aligns with that of the control sample, indicating that  $\Phi_b$  has returned to a level near its original value. This effective recovery indicates that the damage introduced by the

100-nm Si<sub>3</sub>N<sub>4</sub> layer was shallow enough to be removed by a 45-nm-thick sacrificial oxidation process [7-8]. However, a noticeable deviation remains between the N315S45 sample and the control sample, implying that the damage caused by the 315-nm Si<sub>3</sub>N<sub>4</sub> layer was more severe and deeper than the removal capability of the 45-nm sacrificial oxidation process.

**Fig. 2** Current-voltage characteristics of the (a) Control, N100S0, and N100S45 (b) Control, N315S0, and N315S45 SBDs.

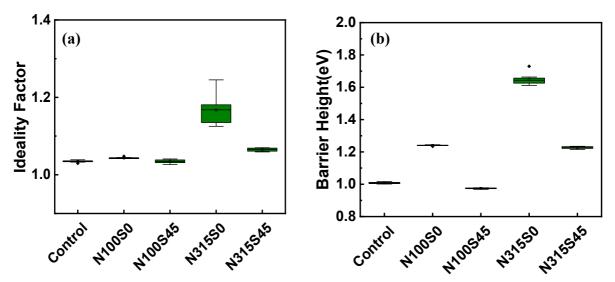

To further investigate this phenomenon, the statistical distributions of the ideality factor (n-factor) and  $\Phi_b$  are depicted in Fig. 3. As previously discussed, the 100-nm-thick Si<sub>3</sub>N<sub>4</sub> layer leads to an increase in  $\Phi_b$ , while having minimal impact on the ideality factor (n-factor). A 45-nm-thick sacrificial oxidation layer can effectively mitigate the increase in  $\Phi_b$ . In contrast, the deposition of a 315-nm-thick Si<sub>3</sub>N<sub>4</sub> layer without sacrificial oxidation results in poor n-factor and  $\Phi_b$  values, along with a broad distribution. The significant variations in both parameters suggest non-uniform stress, likely caused by the thick Si<sub>3</sub>N<sub>4</sub> layer (over 300 nm), which may crack within the layer itself, leading to uneven stress distribution [3].

**Fig. 3** Statistics of (a) ideality factor and (b) barrier height of different samples. The radius of the SBD is 100 μm. Eight SBDs were measures on each sample.

| Sample ID | N <sub>sub</sub> (cm <sup>-3</sup> ) | $\Phi_b$ (eV) |

|-----------|--------------------------------------|---------------|

| Control   | 1.05×10 <sup>16</sup>                | 1.22          |

| N36S0     | 1.07×10 <sup>16</sup>                | 1.22          |

| N100S0    | 1.19×10 <sup>16</sup>                | 2.35          |

| N315S0    | 1.19×10 <sup>16</sup>                | 4.58          |

Table 2 Doping concentration and barrier height extracted from reverse C-V curve.

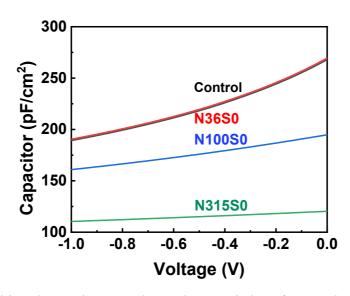

**Fig. 4** Reverse-biased capacitance-voltage characteristics of Control, N36S0, N100S0, and N315S0 SBDs.

The reverse biased capacitance-voltage (C-V) characteristics measured on SBDs without sacrificial oxidation are shown Fig. 4. The measurements were performed at a frequency of 100 kHz, with the voltage sweeping from 0 V to -1 V, and the doping concentration ( $N_{sub}$ ) and  $\Phi_b$  calculated from the C-V curves are presented in Table 2. The C-V curves show that samples N100S0 and N315S0 exhibits significantly lower capacitance compared to the control sample. This decrease in capacitance, associated with an increased Schottky barrier height, suggests the presence of defects introduced by thermal stress. Moreover, the impact on  $\Phi_b$  becomes more pronounced with increasing Si<sub>3</sub>N<sub>4</sub> thickness, consistent with our earlier observations from SBD I-V measurements. It is worth noting that the  $\Phi_b$  values obtained from the C-V curves are significantly higher than those derived from I-V measurements, implying that additional factors are involved, such as the presence of charge trapping and de-trapping in the defect layer within the SiC substrate. For all samples, the N<sub>sub</sub> calculated from the C-V curves are close to the doping concentration of the epitaxial layer used in device fabrication, suggesting that most of the epi-layer remains unaffected. However, the  $\Phi_b$  values obtained from the C-V curves are unreasonable, with the Φ<sub>b</sub> value for the N300S0 sample even exceeding the bandgap value of 4H-SiC (3.26 eV) [9]. This indicates that a large number of traps exists in the defect layer within the SiC substrate, which are generated by the stress of the thick Si<sub>3</sub>N<sub>4</sub> layer. The trapping and de-trapping of charge carriers result in a significant reduction in capacitance, leading to considerable errors in the extrapolated  $\Phi_b$ . In contrast, the C-V curve for the 36-nm-thick  $Si_3N_4$  layer (N36S0) closely overlaps with the control. The calculated  $\Phi_b$  and the  $N_{sub}$  for this sample

are nearly identical to those of the control, indicating that the 36-nm-thick Si<sub>3</sub>N<sub>4</sub> layer has minimal impact on the SiC.

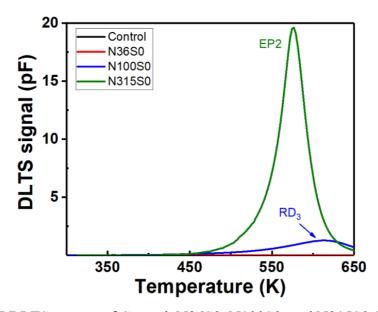

The defect characteristics introduced by  $Si_3N_4$  in SiC were investigated using Deep Level Transient Spectroscopy (DLTS), as shown in Fig. 5. The control group and the N36S0 group did not exhibit any significant defect signals. In contrast, the N100S0 group showed a peak around 600 K, with a defect level at Ec-1.01 eV and a trap concentration of approximately  $9.8\times10^{14}$  cm<sup>-3</sup>, corresponding to the RD<sub>3</sub> defect previously reported to appear in SiC after He<sup>+</sup> implantation and radiation exposure [10-11]. The presence of this defect may lead to the slight increase in  $\Phi_b$  observed in the I–V and C–V characteristics of the N100S0 group.

Fig. 5 DLTS spectra of Control, N36S0, N100S0, and N315S0 SBDs.

In comparison, the N315S0 group demonstrated a more pronounced peak around 560 K, corresponding to a deeper defect level at  $E_{C}$ –1.42 eV, associated with the well-known EP2 level, which has been suggested to be related to carbon interstitials [12]. This defect exhibited a significantly higher trap concentration of approximately  $1.1\times10^{16}$  cm<sup>-3</sup>, which likely contributes to both the notable increase in  $\Phi_{b}$  and the degradation of the n-factor in the I–V characteristics of the N315S0 group, as well as a considerable decrease in capacitance observed in the C–V measurements.

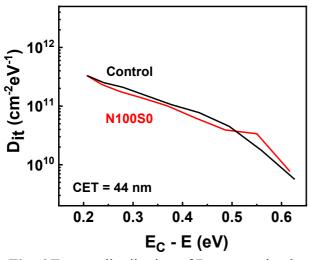

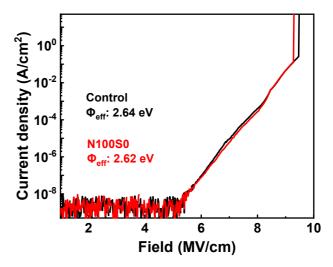

For MOSCaps, high-frequency (100 kHz) and quasi-static capacitance-voltage (C-V) measurements were conducted to calculate interface state density (D<sub>it</sub>) using the high-low frequency method [9]. The capacitance equivalent thickness (CET) of MOSCap is 44 nm. The energy distribution of D<sub>it</sub> is presented in Fig. 6. Both samples show that D<sub>it</sub> at 0.2 eV below the conduction band edge is lower than 5 ×10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup>, and they exhibit similar trends within the range of 0.2 eV to 0.6 eV below the conduction band edge. Furthermore, Time-Zero-Dielectric-Breakdown measurements on MOSCaps were conducted, and the current density-voltage (J-V) curves are depicted in Fig. 7. Both samples exhibit similar current rise trends and breakdown characteristics, showing no distinct differences.

**Fig. 6** Energy distribution of D<sub>it</sub>, extracting by high-low frequency method on MOSCaps.

**Fig. 7** Time-Zero-Dielectric-Breakdown characteristics of MOSCaps.

The rapid increase in leakage current when the electric field exceeds 6 MV/cm is attributed to Fowler-Nordheim (F-N) tunneling, which is related to the effective barrier height of the SiO<sub>2</sub>/4H-SiC interface [13]. The effective barrier height was evaluated from the J-V curves in the 6 to 8 MV/cm range using the classical expression for F-N tunneling, which can be described as

$$J_{FN} = \frac{m_0 q^3}{16\pi^2 \hbar m^* \phi_B} \times E_{ox}^2 \times exp \left[ \frac{-4\sqrt{2m^*}}{3q\hbar} \times (\phi_B)^{\frac{3}{2}} \right]$$

(1)

$$E_{ox} = \frac{V_g - V_{fb}}{T_{ox}} \tag{2}$$

where  $m_0$  is the electron effective mass in 4H-SiC (0.29 $m_e$ ),  $m^*$  is the electron effective mass in SiO<sub>2</sub> (0.42 $m_e$ ) and  $m_e$  is the free electron effective mass. The calculated barrier heights are 2.64 eV for the control sample and 2.62 eV for the N100S0 sample, both of which are slightly lower than the theoretical value of 2.7 eV. This discrepancy can be attributed to the presence of interface traps and oxide traps [13-15]. Although no sacrificial oxidation was performed on the MOSCaps, the gate oxide thickness is similar to that of the sacrificial oxide in the SBD N100S45 sample. The defects associated with the 100-nm-thick Si<sub>3</sub>N<sub>4</sub> film are nearly absent in both the D<sub>it</sub> and TZDB measurements for the MOSCaps. These findings suggest that the oxidation process is effective in mitigating the impact of the Si<sub>3</sub>N<sub>4</sub> layers.

### Summary

A Si<sub>3</sub>N<sub>4</sub> film thinner than 36 nm deposited directly on SiC generally does not impact the quality of the SiC substrate. However, a Si<sub>3</sub>N<sub>4</sub> film over 100 nm thick can introduce significant stress, damaging the SiC surface layer. The presence of defects resulting from the stress can increase both the ideality factor and the Schottky barrier height. Additionally, charge trapping in the defect layer can lead to inaccurate capacitance measurements and incorrect  $\Phi_b$  calculations. The extent of damage is related to the thickness of the Si<sub>3</sub>N<sub>4</sub> layer—a 45-nm-thick sacrificial dry oxidation was able to mitigate the effect from the 100 nm Si<sub>3</sub>N<sub>4</sub> layer but failed to eliminate defects generated from the Si<sub>3</sub>N<sub>4</sub> layer over 300 nm. Therefore, similar to Si process, it is recommended to insert a pad SiO<sub>2</sub> layer between Si<sub>3</sub>N<sub>4</sub> film and SiC.

#### Acknowledgement

This work was supported by the National Science and Technology Council, Taiwan, R. O. C. under the contract No. NSTC 112-2218-E-A49-017.

## References

- [1] G.S. May and C.J. Spanos, Fundamentals of Semiconductor Manufacturing and Process Control, Hoboken, NJ: John Wiley & Sons (2006).

- [2] Xiao Hong, Introduction to Semiconductor Manufacturing Technology, Prentice Hall Inc., New Jersey, USA (2001).

- [3] M. Tamura and H. Sunami, Jpn. J. Appl. 8, 1097 (1972).

- [4] C. -L. Hung, B. -Y. Tsui, C.-P Shih, IEEE Transactions on Electron Devices, vol. 69, no. 10, pp. 5742-5748 (2022).

- [5] B. -Y. Tsui, T. -K. Tsai, Y. -T. Lu, J. -H. Lin, C. -L. Hung and Y. -X. Wen, in IEEE Transactions on Electron Devices, vol. 68, no. 12, pp. 6644-6647 (2021).

- [6] J. -C. Cheng and B. -Y. Tsui, in IEEE Transactions on Electron Devices, vol. 65, no. 9, pp. 3739-3745 (2018).

- [7] Lanni, L., Malm, B. G., Östling, M., & Zetterling, C. M. (2014). Materials Science Forum, vol. 778–780, Trans Tech Publications, Ltd., Feb. 2014, pp. 1005–1008.

- [8] K. Kawahara, M. Krieger, J. Suda, and T. Kimoto, Journal of Applied Physics, vol. 108, no. 2, p. 023706 (2010).

- [9] T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices, and Applications, John Wiley & Sons Singapore Pte. Ltd (2014).

- [10] T. Dalibor, G. Pensl, H. Matsunami, T. Kimoto, W. J. Choyke, A. Schöner, and N. Nordell, Phys. Status Solidi A 162, 199 (1997).

- [11] Thomas Dalibor, Gerhard Pensl, Tsunenobu Kimoto, Hiroyuki Matsunami, Shankar Sridhara, Robert P. Devaty, Wolfgang J. Choyke, Diamond and Related Materials, Volume 6, Issue 10 (1997).

- [12] Katsunori Danno, Tsunenobu Kimoto, J. Appl. Phys. 15 May 2007; 101 (10): 103704.

- [13] K. Agarwal, S. Seshadri and L. B. Rowland, in IEEE Electron Device Letters, vol. 18, no. 12, pp. 592-594 (1997).

- [14] O. Aviñó-Salvadó, B. Asllani, C. Buttay, C. Raynaud and H. Morel, in IEEE Transactions on Electron Devices, vol. 67, no. 1, pp. 63-68 (2020).

- [15] R. Waters and B. V. Zeghbroeck, Appl. Phys. Lett., vol. 76, no. 8, p. 1039 (2000).