# Investigation of Poly-Si Gated, Al<sub>2</sub>O<sub>3</sub>-Based High-k Dielectrics on 4H-SiC

Submitted: 2024-09-19

Revised: 2025-02-27

Online: 2025-09-09

Accepted: 2025-02-28

Johannes Ziegler<sup>1,5,a\*</sup>, Dick Scholten<sup>2,b</sup>, Holger Bartolf<sup>1,c</sup>, Andrii Voznyi<sup>3,d</sup>, Patrick Rabinzohn<sup>3,e</sup> and Jörg Schulze<sup>4,5,f</sup>

<sup>1</sup>Robert Bosch GmbH, Mobility Electronics, 72762 Reutlingen, Germany <sup>2</sup>Robert Bosch GmbH, Corporate Research, 71272 Renningen, Germany <sup>3</sup>Beneq Oy, 02200 Espoo, Finland <sup>4</sup>Fraunhofer IISB, 91508 Erlangen, Germany

<sup>5</sup>Chair of Electron Devices (LEB), FAU Erlangen-Nürnberg, 91508 Erlangen, Germany <sup>a</sup>johannes.ziegler2@de.bosch.com, <sup>b</sup>dick.scholten@de.bosch.com, <sup>c</sup>holger.bartolf@de.bosch.com, <sup>d</sup>andrii.voznyi@beneq.com, <sup>e</sup>patrick.rabinzohn@beneq.com, <sup>f</sup>joerg.schulze@jisb.fraunhofer.de

**Keywords:** MOS capacitor, high-*k* gate dielectrics, atomic layer deposition, poly-Si gate electrode, time-dependent dielectric breakdown, transmission electron microscopy

**Abstract.** In this paper, we investigate the electrical and structural characteristics of  $Al_2O_3$ -based high-k gate dielectrics, which were integrated into a gate-first, high-temperature manufacturing process having comparable thermal budget as needed in 4H-SiC metal-oxide-semiconductor field-effect transistor (MOSFET) production. MOS capacitors were chosen as test devices to examine the electrical performance in terms of current-voltage (I-V) and capacitance-voltage (C-V) behavior. Remarkably, even after processing temperatures of up to 1,000 °C for ohmic contact formation, the  $Al_2O_3$  layers revealed highly uniform breakdown characteristics, low C-V hysteresis and a flat-band voltage (V-E) that closely aligns with the theoretical value. Time-dependent dielectric breakdown (TDDB) measurements of the  $Al_2O_3$  MOS capacitors, however, showed a clear reliability disadvantage concerning the intrinsic dielectric lifetime when comparing with the SiO2 counterpart from commercial SiC production. Finally, to better understand the electrical behavior, transmission electron microscopy (TEM) analysis was conducted, pointing out that high-temperature processing causes the  $Al_2O_3$  films to transition from an amorphous state to an ordered, polycrystalline structure.

### Introduction

Even though the SiC power MOSFET is an established product by now, there is still plenty of room for improving the transistor's performance. To exploit the full potential of the superior material properties of SiC, namely the low drift zone resistance due to the high breakdown field strength, other series resistance contributions, such as the channel resistance, must be kept as small as possible. Despite the continuous progress in improving the  $SiO_2/4H$ -SiC interface and therefore the channel mobility, the channel contribution to the overall on-state resistance ( $R_{DS,on}$ ) remains considerable for most of the SiC power MOSFET products [1].

An innovative approach to minimize the channel contribution is to utilize high-k insulators as gate dielectric material. Due to their higher dielectric constant, the induced inversion charge is increased for the same applied voltage, leading to a reduced channel resistance. Furthermore, most of the high-k dielectrics are deposited by using an atomic layer deposition (ALD) process, which is known for precise thickness control, high uniformity, conformality and reproducibility and offers unique possibilities for in-situ interfacial engineering.

However, there are still major challenges, which complicate the integration of these dielectrics into commercially available SiC power MOSFETs. One of them is the relatively low thermal stability of the commonly used high-k materials. During typical SiC power MOSFET production, temperatures up to 1,000 °C are needed for ohmic contact formation. Moreover, compatibility with poly-Si gate electrode formation must be ensured. According to literature, these processes often lead

to crystallization of the high-k layers, hampering their usage as gate dielectric due to inacceptable leakage currents and reliability issues [2].

In this work, we study the influence of the typical high-temperature processes on the electrical characteristics of poly-Si gated, Al<sub>2</sub>O<sub>3</sub>-based MOS capacitors. We have chosen Al<sub>2</sub>O<sub>3</sub> as the main gate dielectric material due to the relatively high thermal stability as well as the large conduction and valence band-offsets to 4H-SiC. We modified the interfacial properties by using gate dielectric stacks, consisting of thin interfacial layers (SiO<sub>2</sub> and AlN), followed by subsequent Al<sub>2</sub>O<sub>3</sub> deposition.

## **Experimental Details**

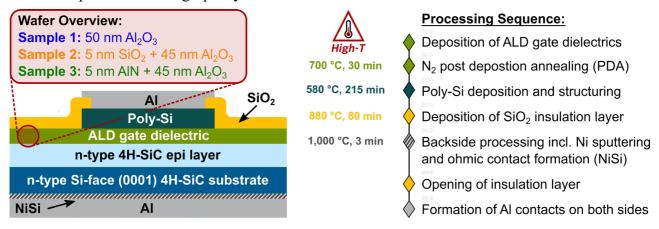

**Device Fabrication.** The MOS capacitors characterized in this work were fabricated on epitaxial n-type layers, grown on conventional 4°-off axis (0001) 4H-SiC 6" substrates. The fabrication, except the gate dielectric depositions, took place in the corporate research cleanroom of the Robert Bosch GmbH. A schematic cross-section of the devices as well as the processing sequence including the applied thermal budget is shown in Fig. 1.

Prior to the gate dielectric deposition, the SiC wafers were cleaned and subsequently etched in a diluted HF acid solution to remove any oxidized surface species. Right after, the Al<sub>2</sub>O<sub>3</sub>-based gate dielectric layers and stacks were deposited according to the wafer overview in Fig. 1 using ALD technology from Beneq TFS 200 R&D. For selected wafers, the interfacial properties were modified by depositing a 5 nm layer of either plasma-enhanced ALD (PEALD) SiO<sub>2</sub> or PEALD AlN prior to the Al<sub>2</sub>O<sub>3</sub> deposition. The Al<sub>2</sub>O<sub>3</sub> films of all samples were grown by means of thermal ALD using trimethylaluminium (TMA) and H<sub>2</sub>O as precursors. For PEALD AlN, TMA and a plasma mixture of NH<sub>3</sub> and N<sub>2</sub> was utilized. In the case of SiO<sub>2</sub> growth, Bis(diethylamino)silane and O<sub>2</sub> plasma were employed as precursors. The process temperature for all depositions was maintained at 300 °C to ensure the production of high-purity films.

Fig. 1. Process flow including the corresponding thermal budget, cross-section and wafer overview of the fabricated Al<sub>2</sub>O<sub>3</sub>-based MOS capacitors.

Except for the ALD process, all three wafers underwent exactly the same fabrication process. After post deposition annealing (PDA) in N<sub>2</sub> ambient at 700 °C for 30 min, in-situ P-doped poly-Si was deposited by means of low-pressure chemical vapor deposition (LPCVD) to form the gate electrode layer. Subsequently, a reactive ion etching (RIE) process was used to structure the poly-Si layer, followed by encapsulating the MOS stack in a high-temperature oxide (HTO), deposited via LPCVD at elevated temperature to enhance the deposition rate. This additional SiO<sub>2</sub> layer was primarily applied to attenuate the electric field strength at the edges of the poly-Si pads to make the MOS capacitor devices suitable for reliable TDDB measurements.

Forming the backside ohmic contact consists of sputter deposition of a thin Ni layer, combined with a rapid thermal annealing (RTA) process at 1,000 °C for 3 min afterwards. Finally, the Al pads were formed on the frontside and backside to contact the MOS capacitor devices during electrical characterization. As the overall applied thermal budget is comparable to SiC MOSFET fabrication, the obtained electrical results are expected to be transferable to transistor devices.

Electrical Characterization. The fabricated MOS capacitor devices were electrically characterized in a Cascade Microtech probe station equipped with different measurement instruments. For *I-V* breakdown characteristics as well as constant voltage TDDB measurements, a Keithley 2636 sourcemeter was connected to the MOS devices. Quasi-static *C-V* measurements were conducted by using a measurement setup consisting of a Keithley 6517 electrometer and a Keithley 2010 multimeter. In this configuration, the electrometer was used to measure the charge on the gate electrode while the applied, stairs-like voltage profile was traced with the additional multimeter.

**Structural Characterization.** To investigate the atomic structure of the gate dielectrics after high-temperature processing, TEM analysis was carried out in a Thermo Fisher Scientific Talos F200X equipment. All inspections were performed using an acceleration voltage of 200 kV. Electron diffraction patterns of the SiC crystal were taken to align the samples accordingly.

#### **Results and Discussion**

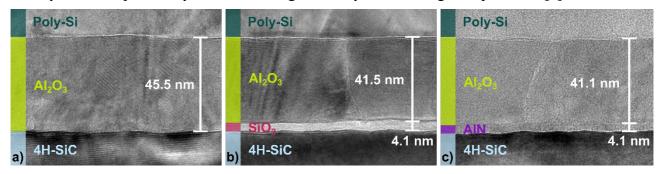

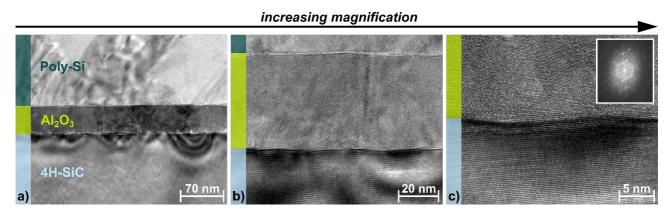

For precise evaluation of the device parameters, the final thickness of the gate dielectric layer after the fabrication process is needed. Therefore, we made TEM images of the samples, as shown in Fig. 2 a)-c). For all three samples, the ALD gate dielectrics got densified during MOS capacitor device fabrication, leading to an overall thickness decrease of approximately 10 %. Similar behavior was already observed previously when annealing Al<sub>2</sub>O<sub>3</sub> layers under high temperatures [3].

**Fig. 2.** TEM overview images of a) sample 1 (Al<sub>2</sub>O<sub>3</sub>/4H-SiC), b) sample 2 (Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC) and c) sample 3 (Al<sub>2</sub>O<sub>3</sub>/AlN/4H-SiC). The shown thickness values are averaged by using several measurements at different positions of one MOS capacitor from the middle of each wafer.

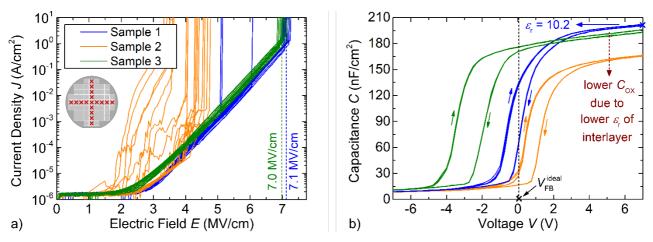

**Electrical Results.** Fig. 3 a) shows the I-V breakdown measurements, which were conducted for numerous MOS capacitor devices per sample in a cross-shape over the whole wafer. Interestingly, samples 1 and 3 show a high uniformity and a Fowler-Nordheim-shaped current increase with an average breakdown field strength  $E_{\rm BD}$  of around 7 MV/cm, whereas sample 2 depicts a much higher spread including premature breakdowns. Comparing all three samples, the only notable difference is the interfacial material in direct contact to the underlying SiC. Accordingly, the results indicate that this interfacial layer is crucial, impacting not only the interface trap density, but also the current blocking capability of the Al<sub>2</sub>O<sub>3</sub> layer.

Besides the *I-V* analysis, quasi-static *C-V* measurements were performed. The corresponding results are shown in Fig. 3 b) for five different devices per wafer. The gate voltage was swept between +7 V and -7 V to stay below the dielectric breakdown of sample 2. Especially in terms of accumulation capacitance, flat-band voltage  $V_{\rm FB}$  and hysteresis  $\Delta V_{\rm FB}$ , a clear difference between the samples is observed. Sample 1 exhibits the highest accumulation capacitance, whereas the value gradually decreases from sample 3 to sample 2 owing to the lower dielectric constant  $\varepsilon_{\rm r}$  of the interfacial AlN and SiO<sub>2</sub> layer with respect to the Al<sub>2</sub>O<sub>3</sub>. Together with the thickness data of Fig. 2 a), measuring the accumulation capacitance of sample 1 allows the  $\varepsilon_{\rm r}$  extraction of the Al<sub>2</sub>O<sub>3</sub> layer. The resulting value of  $\varepsilon_{\rm r}$  = 10.2 is comparably high and may be attributed to a crystallization of the Al<sub>2</sub>O<sub>3</sub> layer during the high-temperature processes of the fabrication sequence [4].

**Fig. 3.** a) *I-V* breakdown measurements for MOS capacitors distributed in a cross-shape over the whole wafer, b) quasi-static *C-V* measurements for five devices per wafer in up- and down-sweep direction.

Nevertheless, especially sample 1 without an intentionally modified interface reveals promising C-V characteristics with low hysteresis and a  $V_{\rm FB}$  value that closely approximates the theoretical value of a poly-Si gated dielectric on SiC. All extracted parameters from Fig. 3 a) and b) are summarized in Table 1. Compared to published analysis on Al<sub>2</sub>O<sub>3</sub> gate dielectrics on SiC [5], the results are notably promising, especially when taking the high thermal load into account, which the devices experienced during the fabrication process. Processing at such high thermal budgets typically leads to crystallization of the Al<sub>2</sub>O<sub>3</sub> layers, accompanied by deteriorated electrical characteristics, such as high leakage currents [6] and/or a large shift in  $V_{\rm FB}$  [7].

**Table 1.** Summary of the sample parameters breakdown field strength  $E_{\rm BD}$ , flat-band voltage in both sweep directions  $V_{\rm FB,low}$  and  $V_{\rm FB,high}$  and hysteresis  $\Delta V_{\rm FB}$  at the flat-band capacitance. Values are averaged and given with the respective standard deviation.  $E_{\rm BD}$  for sample 2 is not listed due to the high spread of values across the wafer.

|                                                              | Sample 1         | Sample 2        | Sample 3         |

|--------------------------------------------------------------|------------------|-----------------|------------------|

| $E_{\mathrm{BD}}\left(\mathrm{MV/cm}\right)$                 | $7.13 \pm 0.08$  | -               | $6.97 \pm 0.08$  |

| $V_{\mathrm{FB,low}}(\mathrm{V})$                            | $-0.36 \pm 0.03$ | $0.64 \pm 0.02$ | $-3.32 \pm 0.01$ |

| $V_{ m FB,high}\left({ m V} ight)$                           | $0.34 \pm 0.01$  | $1.46 \pm 0.01$ | $-1.72 \pm 0.01$ |

| $\Delta V_{\rm FB} = V_{\rm FB,high}$ - $V_{\rm FB,low}$ (V) | $0.71 \pm 0.03$  | $0.82 \pm 0.02$ | $1.60 \pm 0.01$  |

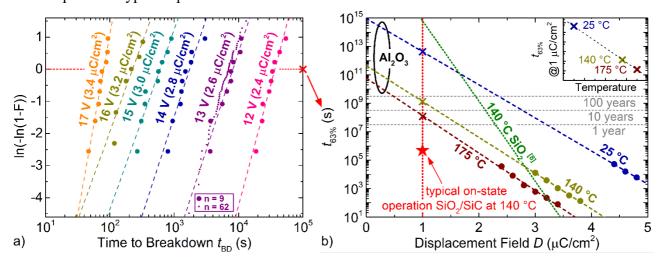

Due to the excellent uniformity of the I-V results, constant voltage TDDB measurements at three different temperatures were carried out for MOS capacitors of sample 1. The corresponding results are shown in Fig. 4. In Fig. 4 a), measurements of different devices at stress voltages between 12 V and 17 V and a temperature of 175 °C are plotted in a double-logarithmic Weibull plot. As the time to dielectric breakdown  $t_{\rm BD}$  increases exponentially with lowering the applied gate voltage, we showed only for one voltage (13 V), that stressing of 62 instead of nine devices ends up in the same Weibull slope of the intrinsic failure branch. Therefore, we conclude that a lower statistic is sufficient to obtain a reliable lifetime estimation.

To get a prognosis of the intrinsic Al<sub>2</sub>O<sub>3</sub> lifetime at typical operation conditions, the  $t_{\rm BD}$  values, at which 63 % of the devices broke ( $t_{\rm 63\%}$  lifetime), were extracted out of Fig. 4 a) and used for the lifetime extrapolation shown in Fig. 4 b). When comparing the lifetime of different gate dielectrics, it is mandatory to consider variations in the oxide thickness  $d_{\rm ox}$  as well as the  $\varepsilon_{\rm r}$  value. Therefore, the  $t_{\rm 63\%}$  lifetime is plotted over the electric displacement field strength D, which can be calculated by using the following expression.

$$D = \varepsilon_0 \varepsilon_r E = \varepsilon_0 \varepsilon_r \frac{V}{d_{ox}}. \tag{1}$$

The *D*-field value thereby describes the charge carrier density at the oxide semiconductor interface and allows for a fair comparison between the Al<sub>2</sub>O<sub>3</sub> gate dielectric of sample 1 and the SiO<sub>2</sub> counterpart, used in commercial SiC production. The extracted  $t_{63\%}$  values at different stress voltages and temperatures are extrapolated to a *D*-field of 1  $\mu$ C/cm<sup>2</sup>, which represents a typical on-state condition when assuming a SiO<sub>2</sub> gate dielectric in SiC MOSFET technology. The estimated intrinsic Al<sub>2</sub>O<sub>3</sub> lifetime at 1  $\mu$ C/cm<sup>2</sup> and a stressing temperature of 140 °C yields values in the range of 10-100 years, which is orders of magnitude below the SiO<sub>2</sub> counterpart [8]. Nevertheless, the conducted measurements are highly consistent and scale perfectly with temperature, as shown in the inset of Fig. 4 b).

Especially due to the large number of extrinsic defects in SiC technology, the  $t_{63\%}$  lifetime should lie well above the typical operation lifetime to ensure the reliability requirements for automotive applications [8]. The typical operation lifetime in on-state is represented by the red star in Fig. 4 b). The comparably lower projected lifetime of the Al<sub>2</sub>O<sub>3</sub>, therefore, leads to a reduced "safety margin" with respect to a typical operation lifetime of a SiC MOSFET.

**Fig. 4.** a) Weibull plot for constant voltage TDDB measurements of sample 1 at 175 °C, b) extracted and extrapolated  $t_{63\%}$  lifetime over *D*-field strength for sample 1 as well as a comparison with the published values of a SiO<sub>2</sub> gate oxide on planar 4H-SiC [8].

The integration of  $Al_2O_3$ -based high-k dielectrics into SiC MOSFETs, used for automotive application, would require additional effort to improve the TDDB behavior of these layers. Therefore, it is crucial to understand the reason behind the above-mentioned lifetime issue. Previously, the effect of the PDA temperature on the reliability of  $Al_2O_3$  dielectrics on GaN was investigated [9]. The published results show that the transition from an amorphous to a crystalline structure by high-temperature annealing comes along with a decrease in reliability. To check whether a similar phenomenon could explain our results, we performed TEM analysis for all three samples.

**Structural Results.** Exemplary high-resolution TEM images of sample 1 with different magnification are shown in Fig. 5. The atomic arrangement within the Al<sub>2</sub>O<sub>3</sub> layer clearly points out that crystallization happened during the MOS capacitor fabrication process. The fast Fourier transformation (FFT) pattern, represented in the inset of Fig. 5 c), supports this observation. Besides the contributions of the SiC substrate, the FFT pattern contains extra reflections, which are attributed to the crystallized Al<sub>2</sub>O<sub>3</sub> film. Furthermore, polycrystalline grains and defects are visible. These non-idealities potentially promote the formation of leakage paths, that lead to a comparably low lifetime of the Al<sub>2</sub>O<sub>3</sub> gate dielectrics.

As a result of the crystallization process, the atoms inside the Al<sub>2</sub>O<sub>3</sub> film rearrange, causing mechanical stress on the underlying SiC substrate. The effect of the stress potentially shows up in the strain fields, which are observed in Fig. 5 a) at the Al<sub>2</sub>O<sub>3</sub>/SiC interface inside the semiconductor.

Fig. 5. High-resolution TEM images of sample 1 with increasing magnification from a) to c).

Comparing the thermal budget of the fabrication process used in this work with published results regarding the annealing of Al<sub>2</sub>O<sub>3</sub> layers on SiC, it is not surprising that crystallization happened during processing. Typically, the crystallization temperature of Al<sub>2</sub>O<sub>3</sub> is reported to lie around 800-900 °C [10]. Especially the ohmic contact annealing and the insulation layer deposition process clearly exceeded this temperature (comp. Fig. 1). Additionally, several studies revealed an unintentional formation of a thin SiO<sub>2</sub> layer at the boundary between Al<sub>2</sub>O<sub>3</sub> and SiC due to an interfacial reaction during high-temperature annealing [11,12]. Such an interfacial SiO<sub>2</sub>, however, could not be observed in our studies.

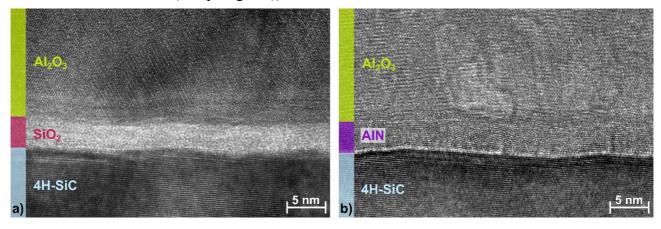

The TEM investigations of samples 2 and 3 showed similar observations in terms of crystallization and strain fields. Therefore, only TEM images at higher magnification are shown in Fig. 6. As expected, the SiO<sub>2</sub> interlayer of sample 2 in Fig. 6 a) is still amorphous, whereas the AlN interlayer of sample 3 in Fig. 6 b) shows areas that seem to have a crystalline atomic arrangement. Accordingly, the Al<sub>2</sub>O<sub>3</sub> film is only for sample 2 in vicinity of an amorphous layer. This might possibly change the onset of the crystallization transition, leading to different grain size, more leakage paths and therefore worse breakdown results (comp. Fig. 3 a)).

**Fig. 6.** High-resolution TEM images showing the interfacial arrangement of a) sample 2 (Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC) and b) sample 3 (Al<sub>2</sub>O<sub>3</sub>/AlN/4H-SiC).

## **Summary**

In this work, the influence of a typical, high-temperature SiC fabrication process on the electrical and structural properties of Al<sub>2</sub>O<sub>3</sub>-based high-*k* dielectrics was investigated. Gate-first MOS capacitors with poly-Si gate electrode and NiSi backside contact were chosen as test vehicles. Especially for Al<sub>2</sub>O<sub>3</sub> dielectrics without an interfacial layer, we showed promising electrical results, consisting of highly uniform breakdown characteristics, high dielectric constant, low *C-V* hysteresis and a nearly ideal flat-band voltage. Nevertheless, TDDB measurements revealed a rather low intrinsic lifetime at typical operation conditions when comparing with a SiO<sub>2</sub> gate dielectric from commercial SiC production. A possible root cause for the comparably low lifetime was found by performing high-

resolution TEM analysis, where all Al<sub>2</sub>O<sub>3</sub> layers turned out to be polycrystalline. Furthermore, our work underlined the crucial role of carefully designing the gate dielectric-semiconductor-interface, not only in terms of interface defects, but also for tailoring the crystallization behavior of high-*k* dielectrics.

## Acknowledgement

This work has received funding from the IPCEI ME/CT project. The IPCEI ME/CT project itself is supported by the Federal Ministry for Economic Affairs and Climate Action on the basis of a decision by the German Parliament, by the Ministry for Economic Affairs, Labor and Tourism of Baden-Württemberg based on a decision of the State Parliament of Baden-Württemberg, the Free State of Saxony on the basis of the budget adopted by the Saxon State Parliament, the Bavarian State Ministry for Economic Affairs, Regional Development and Energy and financed by the European Union – NextGenerationEU.

#### References

- [1] T. Kimoto, "High-voltage SiC power devices for improved energy efficiency", *Proceedings of the Japan Academy. Series B, Physical and Biological Sciences*, Vol. 98, p. 161-189 (2022).

- [2] R. Lo Nigro *et al.*, "Structural and Insulating Behaviour of High-Permittivity Binary Oxide Thin Films for Silicon Carbide and Gallium Nitride Electronic Devices", *Materials*, Vol. 15, no. 3 (2022).

- [3] M. Avice *et al.*, "Rearrangement of the oxide-semiconductor interface in annealed Al<sub>2</sub>O<sub>3</sub>/4H-SiC structures", *Applied Physics Letters*, Vol. 91, no. 5, p. 052907 (2007).

- [4] L. Zhang *et al.*, "Annealing of Al<sub>2</sub>O<sub>3</sub> thin films prepared by atomic layer deposition", *Journal of Physics D: Applied Physics*, Vol. 40, p. 3707-3713 (2007).

- [5] A. Siddiqui *et al.*, "High-*k* dielectrics for 4H-silicon carbide: present status and future perspectives", *Journal of Materials Chemistry C*, Vol. 9, no. 15, p. 5055-5084 (2021).

- [6] L. Liang et al., "Interface properties study on SiC MOS with high-k Al<sub>2</sub>O<sub>3</sub> gate dielectric", 13th IEEE International Conference on Solid-State and Integrated Circuit Technology, p. 67-69 (2016).

- [7] M. Avice *et al.*, "Annealing study of H<sub>2</sub>O and O<sub>3</sub> grown Al<sub>2</sub>O<sub>3</sub> deposited by atomic layer chemical vapour deposition on n-type 4H-SiC", *Physica Scripta*, p. 6-9 (2006).

- [8] T. Aichinger *et al.*, "Gate-oxide reliability and failure-rate reduction of industrial SiC MOSFETs", *IEEE International Reliability Physics Symposium*, p. 1-6 (2020).

- [9] K. Horikawa *et al.*, "Postdeposition annealing effect on the reliability of atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> films on GaN", *Journal of Vacuum Science & Technology B*, Vol. 38, no. 6, p. 062207 (2020).

- [10] L. Tian *et al.*, "Influences of annealing on structural and compositional properties of Al<sub>2</sub>O<sub>3</sub> thin films grown on 4H–SiC by atomic layer deposition", *Chinese Physics B*, Vol. 25, p. 128104 (2016).

- [11] S. Diplas *et al.*, "Interfacial studies of Al<sub>2</sub>O<sub>3</sub> deposited on 4H-SiC(0001)", *Surface and Interface Analysis*, Vol. 40, no. 3-4, p. 822-825 (2008).

- [12] M. Usman *et al.*, "Improving the quality of Al<sub>2</sub>O<sub>3</sub>/4H-SiC interface for device applications", *Materials Science in Semiconductor Processing*, Vol. 81, p. 118-121 (2018).