# C-Face Epitaxy for Enhanced SiC Device Performance: Insights from Schottky Barrier Diodes

Submitted: 2024-09-20

Revised: 2025-08-15

Online: 2025-09-09

Accepted: 2025-08-15

Voo Qin Gui Roth<sup>1,a\*</sup>, Abdul Hannan Yeo<sup>1,b</sup>, Lakshmi Kanta Bera<sup>1,c</sup>, Umesh Chand<sup>1,d</sup>, Yu-Chieh Chien<sup>1,e</sup>, Nguyen Xuan Sang<sup>1,f</sup>, Wen Dong Song<sup>1,g</sup>, Shiv Kumar<sup>1,h</sup>, Hung Ming Chua<sup>1,i</sup>, Navab Singh<sup>1,j</sup>, Surasit Chung<sup>1,k</sup>, Shane Kam<sup>2,l</sup>, Marcin Zielinski<sup>2,m</sup>, Loic Kabelaan<sup>2,n</sup>, Walter Schwarzenbach<sup>2,o</sup>, Ionut Radu<sup>2,p</sup>, Loann Boudin<sup>2,q</sup>

<sup>1</sup>Institute of Microelectronics (IME), Agency for Science, Technology and Research (A\*STAR), Singapore 138634

<sup>2</sup>SOITEC, Parc Technologique des Fontaines, 38190 Bernin, France

aroth\_voo@a-star.edu.sg, bhannan\_yeo@a-star.edu.sg, clakshmi\_kanta\_bera@a-star.edu.sg, dchand\_umesh@a-star.edu.sg, echien\_yu\_chieh@a-star.edu.sg, fnguyen\_xuan\_sang@a-star.edu.sg, gsong\_wen\_dong@ime.a-star.edu.sg, bhiv\_kumar@a-star.edu.sg, chuahm@a-star.edu.sg, inavab@a-star.edu.sg, ksurasit\_chung@ime.a-star.edu.sg, lshane.kam@soitec.com, mmarcin.zielinski@soitec.com, com, cloic.kabelaan@soitec.com, walter.schwarzenbach@soitec.com, pionut.radu@soitec.com, cloann.boudin@soitec.com

Keywords: Carbon face epitaxy, C-face 4H-SiC, Schottky Barrier Diode

**Abstract.** This study focuses on analyzing the electrical performance and characteristics of Schottky Barrier Diodes (SBDs) on the carbon face (C-face) epitaxial layer. The C-face epitaxial layer is grown on monocrystalline 4H-SiC and has a thickness of ~ 11  $\mu$ m. It displayed minimal surface roughness, with an  $R_q$  of ~ 0.3 nm. The C-face termination epitaxy was examined using grazing-angle X-ray photoelectron spectroscopy (XPS) analysis. SBDs were fabricated using a Ti/Al metal stack. Schottky Barrier Height ( $\Phi_B$ ) of about 1.2 eV was extracted from *I-V* measurements. Temperature-dependent *I-V* measurements demonstrated a forward voltage decrease as the temperature rises when the forward current is < 1  $\mu$ A. However, for forward currents > 1  $\mu$ A, the forward voltage increases with temperature. This rise in forward voltage could lead to a reduction in reverse recovery time and thus enhancing the switching speed. Additionally, the diode exhibits remarkable immunity to reverse leakage current up to 200 °C, surpassing the performance of the 6.5 kV JBS diode on Si-face 4H-SiC [1].

# Introduction

Wide-band gap (WBG) semiconductors are widely regarded as the building blocks for the future of power electronics devices. Among all WBG materials, 4H-SiC stands out as the most promising for power devices. Various types of devices fabricated on the Si-face of 4H-SiC have achieved a high level of technological maturity. However, the carbon-face  $(000\overline{1})$  crystallographic orientation offers significant advantages over the conventional Si-face, particularly in terms of enhanced thermal stability and carrier mobility [2]. The C-face of SiC exhibits fewer surface defects than Si-face.

Despite these advantages, device fabrication on C-face epitaxy has not been thoroughly explored to fully exploit the high electron mobility, superior switching characteristics, power efficiency, and expanded operational frequencies. Several factors play a part in the lack of motivation for development of C-face SiC devices such as the difficulty to achieve a reliable gate oxide layer with standard gate oxidation processes on C-face SiC due to the high oxidation rate. A poor gate oxide interface would compromise the device quality and negatively impact the performance of SiC devices. Among the different types of devices, Schottky diodes have shown remarkable performance as power diodes for fast switching applications, with minimal power loss. The overall performance of a Schottky diode is influenced by various conditions, including the semiconductor surface

characteristics, the metal work function used, and the metal-semiconductor interface [3,4]. The objective of this study is to investigate the electrical characteristics of a C-face epitaxilly grown 4H-SiC using a Ti-based Schottky diode.

# **Results and Discussion**

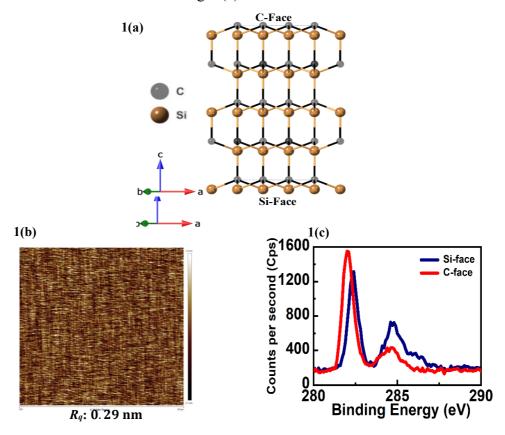

A 150 mm epi-ready n-type 4H-SiC substrate with a C-face orientation obtained from SOITEC, was used as the initial substrate for epitaxial growth. Subsequently, a 10 μm SiC epilayer was grown with C-face termination as visualized in Fig. 1(a).

**Fig. 1.** (a) C-face 3D Crystal Structure, (b) Atomic Force Microscopy (AFM) image showing the surface morphology of the C-face epitaxial layer, (c) XPS analysis (C1s peak to peak ratio).

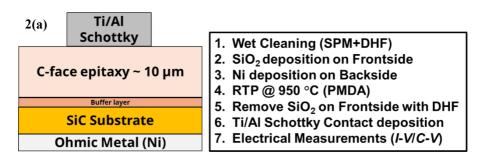

This growth utilized a standard buffer layer of approximately 0.5 µm and was performed in a commercial hot-wall chemical vapor deposition (CVD) system. Low surface roughness of the epitaxial layer with an  $R_q$  value of approximately 0.3 nm was obtained from atomic force microscopy (AFM) as shown in Fig. 1(b). To confirm the termination of the grown epitaxial layer, X-ray photoelectron spectroscopy (XPS) analysis revealed an increase in the carbon, peak-peak ratio of the two C1s peaks, indicating C-face termination outlined in Fig. 1 (c). This ratio was higher in comparison with another Si-face terminated grown epilayer. SBDs were fabricated as shown in Fig. 2 (a) with a Ti/Al metal contact. A sacrificial oxide layer was deposited on the frontside of the sample to ensure the interface remains clean when processing the backside Ni ohmic contact. A Ni ohmic backside contact was formed through PMDA at 950 °C. The sacrificial oxide layer on the frontside was then stripped with dilute hydrofluoric acid (DHF) followed by subsequent metallization right after. This maintained the integrity of the MS interface prior to metallization. SiO<sub>2</sub> was then removed with DHF, followed by Ti/Al deposition in a commercial physical vapour deposition (PVD) chamber right after. The thickness and integrity of the metal-SiC (MS) interface was observed with TEM as shown in Fig. 2 (b). An atomically smooth Ti/SiC interface layer was observed. A Ni ohmic contact was formed on the backside of the device after post-metal deposition annealing (PMDA) at 950 °C, prior to Ti/Al Schottky contact deposition [5].

Fig. 2. (a) Schematic of the Schottky Barrier Diode fabrication process, highlighting the Ti/Al metal contact and post-metal deposition annealing steps.

Fig. 2. (b) Transmission Electron Microscopy of Metal-SiC Interface.

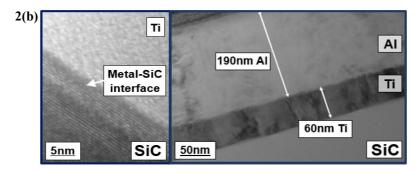

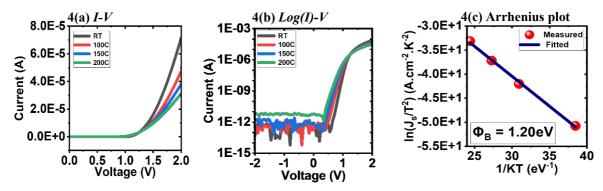

The doping concentration (9.6 x  $10^{15}$  cm<sup>-3</sup>) of the C-face epilayer was extracted electrically from the measured C-V of SBDs in Fig. 3 (a-b) [6]. C-V was measured at 1 MHz on radius 100  $\mu$ m devices. From the linearity of the  $I/C^2$  vs V plot, uniform doping can de deduced across the 150mm wafer. Table 1 shows the barrier height extracted from several SBDs using I-V techniques with good uniformity and distribution. The barrier heights correlate to the increased knee voltage ( $V_{knee}$ ) observed from I-V plots shown in Fig. 4 (a-b).

**Fig. 3.** (a) *C-V* of 5 Devices (b)  $1/C^2$  vs *V*.

**Fig. 4.** (a) Linear I-V, (b) Log(I)-V, (c) Arrhenius plot.

**Table 1.**  $\Phi_B$  obtained from 5 devices, Table 2:  $I_s$  vs Temperature.

| Table 1                          |                               |

|----------------------------------|-------------------------------|

| As Deposited/Room<br>Temperature | $\Phi_B$ [eV] from <i>I-V</i> |

| Device 1                         | 1.15                          |

| Device 2                         | 1.20                          |

| Device 3                         | 1.15                          |

| Device 4                         | 1.22                          |

| Device 5                         | 1.19                          |

| Table 2          |                                          |

|------------------|------------------------------------------|

| Temperature      | Saturation Current (I <sub>s</sub> ) [A] |

| Room Temperature | 4.6E-14                                  |

| 100°C            | 9.4E-14                                  |

| 150°C            | 3.13E-13                                 |

| 200°C            | 6.15E-12                                 |

Furthermore, from the SBDs *I-V* characterizations, we derived the barrier height from Arrhenius plots and demonstrated its strong correlation with data obtained from *I-V* extraction. Our findings closely matched those of a previous study (1.97 eV) for Ni-based materials, whereas this study, focused on Ti-based materials (1.15 eV) [3]. This variance can stem from the use of different metal stacks and doping concentrations of the C-face epi layer, which would influence the barrier height. The SBDs fabricated on C-face epitaxial layers demonstrated significantly low leakage current, less than 6pA, even at elevated measurement temperatures up to 200 °C as shown in Table 2. Forward current was observed to be lowered with increased temperature in Fig. 4(a). This change in the forward current could be caused by increased phonon scattering at high temperatures. The strong bonding force promotes large lattice vibrations, making excitation of donors difficult. Current enhancement in the subthreshold region as seen in Fig 4(b) could indicate that the thermal emission is encouraging this change. We observed a remarkable immunity to reverse leakage increase with temperature, which is superior to 6.5 kV JBS diodes fabricated on Si-face 4H-SiC [1].

#### Conclusion

In this work, we have demonstrated the electrical characteristics of SBDs on C-face epitaxy substrates with excellent mobility and slight increase in barrier height with temperature. Immunity against temperature dependent reverse leakage current was observed and attributed to the high quality C-face epitaxial grown layer as well as the clean metal-semiconductor interface before metallization. Lowered forward current with increasing temperature as a possible result of increased phonon scattering with high temperature was also observed and discussed. This work demonstrates the viability of implementing Schottky diodes on C-face epitaxial layers to exploit its excellent intrinsic material properties in comparison with Si-face devices.

# Acknowledgement

This work was supported by A\*STAR (Agency for Science, Technology and Research Singapore), under Grant No. A20H9A0242.

# References

- [1] X. Niu, Effect of Schottky annealing temperature on reverse leakage current of 6500 V 4H-SiC JBS diodes, Journal of Crystal Growth 608 (2023) 127103.

- [2] Kodigala Subba Ramaiah et al., "Growth and characterization of SiC epitaxial layers on Si- and C-face 4H SiC substrates by chemical-vapor deposition," Journal of Applied Physics, 98, no. 10 (2005).

- [3] A. Itoh, T. Kimoto, and H. Matsunami, "High performance of high-voltage 4H-SiC Schottky barrier diodes," IEEE Electron Device Letters, 16, 6 (1995) 280–282.

- [4] M. Furno, Design, Fabrication and Characterization of 1.5 mΩcm<sub>2</sub>, 800 V 4H-SiC n-Type Schottky Barrier Diodes, Materials science forum, 483–485 (2005) 941–944.

- [5] A. Hannan, The Effect of Nitrogen Plasma Treatment Process on Ohmic Contact Formation to N-Type 4H-SiC, Diffusion and defect data, solid state data. Part B, Solid state phenomena/Solid state phenomena, 359 (2024) 59–63.

- [6] Tsunenobu Kimoto and J. A. Cooper, Fundamentals of silicon carbide technology: growth, characterization, devices and applications. Singapore: John Wiley & Sons (2014).