© 2009 The Author(s). Published by Trans Tech Publications Ltd, Switzerland.

# Effect of Source and Drain Contacts Schottky Barrier on 3C-SiC Nanowire FETs I-V Characteristics

Online: 2009-03-02

Konstantinos Rogdakis<sup>1-2,a</sup>, Seoung-Yong Lee<sup>3</sup>, Dong-Joo Kim<sup>3</sup>, Sang-Kwon Lee<sup>3</sup>, Edwige Bano<sup>1</sup> and Konstantinos Zekentes<sup>2</sup>

<sup>1</sup>IMEP-LAHC/Grenoble INP, MINATEC, France

<sup>2</sup>Institute of Electronic Structure and Laser (IESL) -FORTH, Greece

<sup>3</sup>Department of Semiconductor Science and Technology,SPRC, Chonbuk National University, Jeonju 561-756, Korea

arogdakik@minatec.inpg.fr

**Keywords:** 3C-SiC, nanowire, FET, Schottky contacts, simulation

**Abstract.** In this work, SiC nanowire (NW) FETs are prepared and their electrical measurements are presented. From the samples fabricated on the same substrate, various I-Vs shapes are obtained (linear, non linear symmetric, and asymmetric). With the assistance of simulation, we show that this is a result of different values of Schottky Barrier Heights (SBH) at Source (S) / Drain (D) contacts of FETs. An origin for this might be a non uniformity in annealing, NW doping level and high interface traps density (that pins the Fermi level) as well as the high sensitivity of the metal-NW contacts to local surface contaminations.

#### Introduction

The majority of the research groups working on NW FETs use metals as S / D areas and they are trying to lower the rectifying SB [1] or even transform them to completely ohmic [2] by proper annealing step. In the first work on SiC NW FETs [2], the researchers used low work-function metal (Ti) in contact with highly n-type doped nanowire and so the initial SB was easily suppressed after the annealing leading to ohmic contacts (linear I-V for low V<sub>d</sub>). In contrast in [1], a high workfunction metal (Au) was used so the SB of the contacts was not suppressed completely after the annealing step and a non linear shape of I-Vs was obvious. Anyhow, forming SB instead of ohmic contacts might have interesting applications in nanoelectronics. In standard CMOS technology, SB-MOSFETs have recently attracted a renewed interest as an alternative to conventional MOSFETs with doped S and D contacts [3,4]. SB-MOSFET devices with metal as S and D replace S/D impurity doping with metal parts. This is due to the fact that in the near future the continued downscaling of transistor dimensions calls for highly conductive source and drain electrodes otherwise the current through the device will be limited by the contacts. There are numerous motivations for replacing doping with metal in the S/D regions, including low parasitic S/D resistance, low-temperature processing for S/D formation and inherent physical scalability which is due to the low resistance of metal and the atomically abrupt junctions formed at the metalsemiconductor interface. This picture is more stressed in the case of NW FETs due to the 1D nature of the semiconductor.

In the present work, SiC NW FETs are prepared and their electrical measurements are presented. From the samples synthesized on the same substrate using the same metal contacts and device process steps, various I-Vs characteristics shapes are obtained (linear, non linear symmetric and asymmetric). With the assistance of simulation, we show that this is a result of different values of SB heights at S/D contacts.

## **Experimental results**

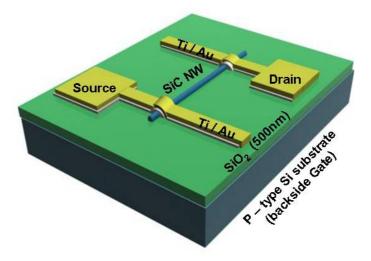

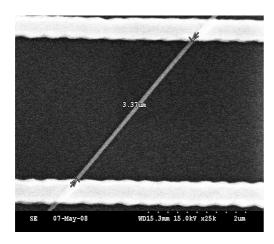

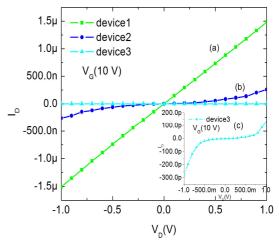

SiC NWs were grown by using a Hot-Wall Chemical Vapor Deposition (HW-CVD) system with a methyltrichlorosilane (MTS, CH<sub>3</sub>SiCl<sub>3</sub>) source precursor (see more detailed information about the synthesis and materials characteristics of cubic SiC NW in [2]). The SiC NWs had diameter less than 100nm and lengths of several microns. As-synthesized SiC NWs were prepared on a highly doped silicon wafer covered with a 500 nm-thick thermal SiO<sub>2</sub> layer on top. The highly doped (>10<sup>20</sup> cm<sup>-3</sup>) n<sup>+</sup> Si wafer was served as a back gate electrode in three-probe FET structures. Prior to the metal deposition (Ti/Au=50/150 nm) by electron-beam evaporation, the substrate was prepatterned and the SiO<sub>2</sub> was removed from the ohmic contact areas by dipping in buffered hydrofluoric acid (BHF) for 30 seconds. Then, source and drain electrodes (Ti/Au) were defined by standard e-beam lithography and lift-off process. Fig. 1 shows a schematic view of the single SiC NW FET prepared on the SiO<sub>2</sub>/n-Si wafer in three-probe FET configuration and Fig.2 shows a SEM image of the device. The I-V characteristics of three NWFETs of the same sample are shown in Fig.3. As it is obvious from the linearity of the I-V device 1 has ohmic contacts while devices 2 and 3 have non linear I-Vs. As depicted below from simulation results, the different SBs of S/D lead to these non linear I-V characteristics.

Fig. 1 Schematic view of SiC NWFET

Fig. 2. Scanning Electron Microscope view of one of the SiC NWFETs

Fig. 3. Experimental I-Vs from various NWFETs of the same sample; inset: zoom for device

#### Simulation results

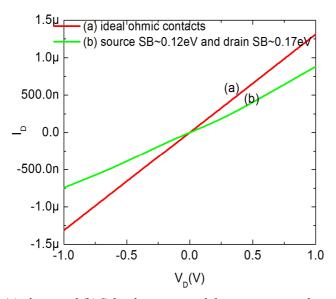

A commercial simulation tool [5] is used which solves the Boltzmann transport equation within the drift-diffusion approximation with the Poisson equation. Indeed at the micrometer scale the drift-diffusion model used in SILVACO is a well adapted tool to describe electronic transport in semiconductor devices operating within a diffusive transport regime and far away from the strong quantum regime (>10 nm) [6]. Using the same method with [6], we tried to simulate the non-linear I-Vs of the experimental devices. The simulated device has exact the same dimensions and geometry with the experiment one. By using ohmic or Schottky contacts (with a non-zero SB), we simulate the experimental behavior. As shown in Fig. 4, by applying non-zero and not equal SBs at the S/D contacts has as result the non linear I-V shape (Fig. 4 curve b). When ohmic contacts are considered at the same device, Fig. 4 curve (a), then a linear I-V is obtained. At this point we have to note down that in the case of small difference between source and drain SBs, as in case of curve (b) of Fig. 4, the accurately fitting of the experimental results with Silvaco software is not possible. When ohmic contacts are considered [6] like curve (a) of Fig.4, and when the SB difference is quite big like in [7], then accurate fitting with the experimental results is achievable.

Fig. 4. Simulated I-Vs for (a) ohmic and (b) Schottky source and drain contacts with small difference in barrier heights.

#### **Discussion and conclusions**

A qualitative analysis of S/D contacts SBs effect on the SiC NWFETs I-V characteristics is presented. Even at the same wafer with many 3C-SiC NWFETs, various I-Vs shapes are obtained (linear, non linear symmetric and asymmetric). According to simulation results, this behavior is due to different (non zero) SB at S and D contacts. The fact that the devices belong to the same wafer exclude all the other reasons such as different metal material or different fabrication process to explain this different behavior. A non uniformity in annealing, NW doping level [8,9] and high interface traps density (that pins the Fermi level) as well as the high sensitivity of the metal-NW contact to local surface contaminations [10-13] might explain the different SBs between S and D. In [11-13] the researchers noticed a similar behavior with non linear I-Vs of Carbon Nanotube (CNT) FETs. Lu *et al.* [12] used intentionally a chemical in the process of one of the two metal contacts surface of a CNTFET and they noted asymmetric I-Vs due to the different SB of S and D. Moreover, they presented some ab initio calculations and they showed the increased sensitivity of the metal work-function to these chemicals. Kim *et al.* [13] showed that remaining from the PMMA (due to imperfect development) during the lift off process step might have an impact to the SB of the contacts. More specialized experiments should be performed in order to identify the origin of

these different contacts SBs of the same device. If not, a bottleneck in the mass production of nanowire FET devices will be present.

# Acknowledgements

This work was supported by the Greek Ministry of Development (GSRT/Grants 05NON-EU-265, 11-PPK06).

### References

- [1] W. M. Zhou, F. Fang, Z. Y. Hou, L. J. Yan and Y. F. Zhang: IEEE Electron Device Letters Vol. 27 (2006), p. 463

- [2] H. K. Seong, H. J. Choi, S. K. Lee, J. I. Lee and D. J. Choi: Applied Physics Letters Vol. 15 (2004), p. 1256

- [3] E. Dubois, G. Larrieu: Journal of Applied Physics Vol. 96, (2004), p. 729

- [4] M. Fritze, C.L. Chen, S. Calawa, D. Yost: IEEE Electron Device Letters Vol. 25 (2004), p. 220

- [5] ATLAS simulation program, SILVACO International

- [6] K. Rogdakis, S. Y. Lee, M. Bescond, S. K. Lee, E. Bano and K. Zekentes: IEEE Transactions Electron Devices, Vol. 55 (2008), p. 1970

- [7] S. K. Lee, S. Y. Lee, K. Rogdakis, C. O. Jang, D. J. Kim, E. Bano and K. Zekentes: Submitted to Electronic Letters

- [8] A. Asenov, A. R. Brown, J. H. Davies, S. Kaya, and G. Slavcheva: IEEE Transactions on Electron Devices Vol. 50 (2003), p. 1837

- [9] M. Zhang, J. Knoch, Q. T. Zhao, U. Breuer and S. Mantl: Solid-State Electronics Vol. 50 (2006), p. 594

- [10]S. M. Sze and K. K. Ng: Physics of Semiconductor Devices (2007), 3<sup>rd</sup> edition

- [11]S. Moon, S. G. Lee, W. Song, J. S. Lee, N. Kim, J. Kim, and N. Park: Applied Physics Letters Vol. 90, (2007), p. 092113

- [12]C. Lu, L. An, Q. Fu, J. Liua, H. Zhang and J. Murduck: Applied Physics Letters Vol. 88, (2006), p. 133501

- [13]W. Kim, A. Javey, R. Tu, J. Cao, Q. Wang, and H. Dai: Appl. Phys. Lett. Vol. 87 (2005), p. 173101