# Effects of High Gate Voltage Stress on Threshold Voltage Stability in Planar and Trench SiC Power MOSFETs

Submitted: 2023-09-29

Revised: 2024-03-24

Online: 2024-08-21

Accepted: 2024-04-05

Ayan K. Biswas<sup>1,a\*</sup>, Daniel J. Lichtenwalner<sup>1,b</sup>, Suman Das<sup>1,c</sup>, Caleb Isaacson<sup>1,d</sup>, Satyaki Ganguly<sup>1,e</sup> and Donald A. Gajewski<sup>1,f</sup>

<sup>1</sup>Wolfspeed, Inc., 4600 Silicon Drive, Durham, NC 27703, USA

<sup>a</sup>ayan.biswas@wolfspeed.com, <sup>b</sup>daniel.lichtenwalner@wolfspeed.com, <sup>c</sup>suman.das@wolfspeed.com, <sup>d</sup>caleb.isaacson@wolfspeed.com, <sup>e</sup>satyaki.ganguly@wolfspeed.com, <sup>f</sup>don.gajewski@wolfspeed.com

**Keywords:** Threshold voltage, Gate reliability, Planar MOSFET, Trench MOSFET.

**Abstract.** Gate oxide reliability is a challenge in SiC MOSFETs particularly due to the presence of high electric field in the dielectric during device operation and blocking, and SiC/SiO<sub>2</sub> interfaces suffer from a high density of traps and defects that can cause charge trapping and threshold voltage shift. Highly accelerated gate bias testing can be used for testing gate field effects on device reliability/stability, but care must be taken that the high acceleration biases do not invoke failure mechanisms that fall outside of normal device operation conditions. In this work, we attempt to address that aspect of high voltage gate tests in terms of threshold voltage instability and perform a comparative analysis between commercially available planar and trench SiC MOSFETs.

# Introduction

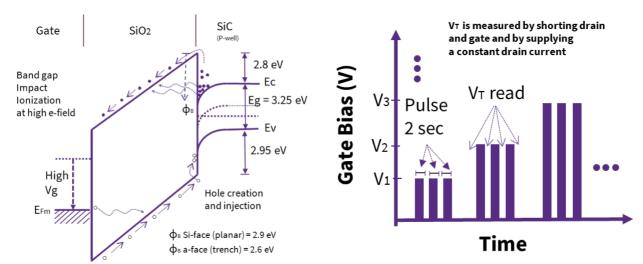

There is significant interest in high-voltage Silicon Carbide (SiC) power devices due to their ability to block higher voltage with lower conduction and switching losses compared to their silicon counterparts [1]. Thanks to their wider bandgap leading to higher critical electric field, SiC devices can achieve higher breakdown voltage with much thinner drift regions relative to Si devices. Consequently, on-resistance can be significantly lower in SiC devices resulting in substantially lower power losses. However, in devices with lower voltage ratings, channel resistance is the main contributing factor towards overall on-resistance. Channel resistance is affected by the low mobility of electrons under inversion due to trapping and scattering at the SiC/SiO<sub>2</sub> interface. Even though significant progress has been made over the last decade to passivate interface defects e.g. with NO annealing, there still exists a high density of traps and defects that can cause charge trapping and threshold voltage shift [2-4]. Moreover, SiC MOSFETs experience high electric field in the dielectric during device operation and blocking; thus, making a reliable gate oxide particularly challenging. Highly accelerated gate bias testing can be used, but careful consideration is required to choose the right bias condition so that failure mechanisms that fall outside of normal device operation conditions do not emerge [5-9]; such as current accelerated process as schematically shown in Fig. 1. In this work, a comparative analysis between commercially available planar and trench SiC MOSFETs is performed to investigate the effect of high gate voltage stress particularly on threshold voltage stability.

# Effect of High Gate Stress on V<sub>T</sub>

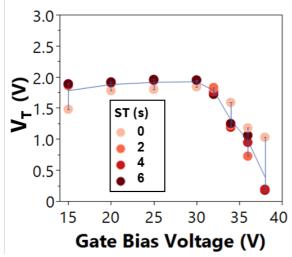

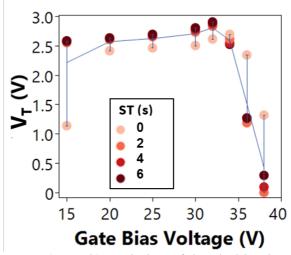

Fig. 2 depicts the diagram of a gate bias and threshold voltage (V<sub>T</sub>) measurement scheme that is performed at room temperature. A 6 s stress is applied at the gate starting with the rated gate

Fig. 1. At high electric field, hot electrons tunneled through oxide barrier with high energy tails exceeding 9eV may cause bandgap impact ionization near anode interface. This effect can be higher in trench devices due to lower  $\Phi_B$ .

**Fig. 2**. Gate stresses  $(V_{GS})$  are applied for a duration of 6 s with threshold readouts performed before the gate pulses, and at 2 s intervals.  $V_{GS}$  is then stepped to a higher value and the process is repeated.

bias  $(V_{GS})$ , while  $V_T$  is measured at time t = 0, 2, 4, and 6 s by shorting drain and gate together and by supplying a constant drain current of 1uA. This process is repeated by gradually incrementing gate bias to higher values of V<sub>GS</sub>. Fig. 3 and 4 show the results of these tests for commercial 1200V planar and trench SiC MOSFETs, respectively where V<sub>T</sub> values are plotted with respect to gate bias voltages. There exist four  $V_T$  measurements for each stress time ST = 0, 2, 4 and 6 s (from lighter circles to darker circles) at each gate bias where ST = 0 s indicates  $V_T$  measurement before any stress pulse is applied. After the application of the first pulse (ST = 2 s) at  $V_{GS}$  = 15V, the threshold voltage increases due to PBTI effects. Additional gate stress pulses (ST = 4 and 6 s) at 15V barely increase  $V_T$  further as indicated by the overlapping circles in figures 3 and 4. Gate stress is then increased from the rated value of 15V to 38V with a step of 5V (for lower stress region) and 2V (for higher stress region). V<sub>T</sub> starts to increase gradually due to PBTI effects at lower stress, but after a critical value of V<sub>GS</sub>, the threshold voltage starts to decrease. V<sub>T</sub> increment is found to be higher in trench devices than in planar devices and the critical value happens to be 30V for planar device and 32V for trench device respectively. It should be noted that from our analysis of the products tested, the trench MOSFET has a thicker gate oxide, which would affect the onset of this V<sub>T</sub> decrease behavior (oxide electric field should be more important than gate potential). At the higher voltage region above this critical value, consecutive pulses of higher V<sub>GS</sub> continue to decrease threshold even lower. At the significantly high gate stress ( $V_{GS} = 38V$ ), threshold decreases to zero in both planar and trench devices. measurement approach used here for  $V_T$  evaluation does not allow  $V_T < 0V$  to be measured; however, from I<sub>D</sub>-V<sub>G</sub> sweeps the V<sub>T</sub> is seen to fall well below 0V as the V<sub>GS</sub> pulse height is increased.

While the increase in threshold voltage happens due to PBTI effect below the critical voltage or electric field, the physics of threshold degradation above critical value is still under debate. There exist several theories that attempt to explain gate oxide breakdown under high field in Si/SiO<sub>2</sub> and one such theory can be adopted to explain threshold instability in SiC/SiO<sub>2</sub> as well. The decrease in threshold voltage at high field can be attributed to bandgap impact ionization occurring near the SiO<sub>2</sub>/gate interface. At high electric field (>9MV/cm) when a significant portion of electrons that

**Fig. 3.** (Planar) Variation of threshold voltages  $(V_T)$  with respect to the gate bias pulses.  $V_T$  is measured at t = 0, 2, 4 and 6 s for each gate bias condition. [ST = Stress Time]

**Fig. 4.** (Trench) Variation of threshold voltages  $(V_T)$  with respect to the gate bias pulses of 6 s for a trench MOSFET.  $V_T$  is measured at t = 0, 2, 4 and 6 s for each gate bias condition. [ST = Stress Time]

tunnel through the dielectric via Fowler-Nordheim (FN) mechanism gain high kinetic energy (exceeding 9eV) from the electric field while traversing through the thick oxide and create electronhole pairs due to impact ionization near the SiO<sub>2</sub>/Gate interface [10-14]. Hot holes travel back through the oxide towards SiO<sub>2</sub>/SiC interface and may get trapped during the process either in the oxide or deep energy interface states resulting in fixed oxide charges (see Fig. 1). In another scenario, when electron's energy does not exceed 9eV but high enough that upon reaching the anode, hole is generated from impact ionization at the anode. These holes tunnel into the oxide and eventually trap somewhere in the oxide while traversing towards SiO<sub>2</sub>/SiC interface. Regardless of the underlining mechanism of hole generation, holes fill in the existing traps in the oxide and the net result is a buildup of positive charge that acts like fixed charge. There can be some hole annihilation due to electron trapping, but accumulation of holes outnumbers electron trapping, resulting in a decrease in threshold voltage. In addition, hole trapping in near-interface states near the valence band may be occurring simultaneously.

# **Gate Bias Hysteresis of Drain Leakage**

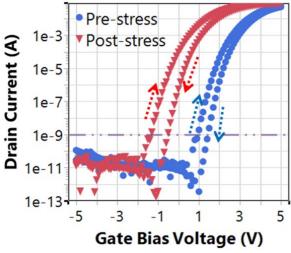

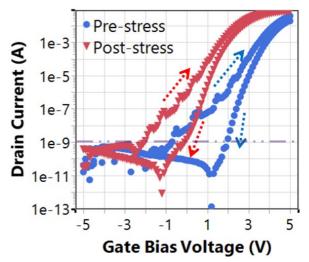

In the previous section,  $V_T$  is measured by gradually increasing gate bias and it is observed that the threshold voltage degrades significantly under high bias above a critical value. In this section, we attempt to estimate the level of degradation by measuring a low gate bias hysteresis of drain leakage. Figures 5 and 6 show drain current hysteresis for pre- and post-stress (stress applied in Fig. 2) while sweeping  $V_{GS}$  from +5V to -5V (down arrow) and vice versa (up arrow) with a step of 0.1V. Drain voltage,  $V_{DS}$  is kept at a low value of 0.1V. Both planar and trench devices show negative shifts in their  $V_T$  indicating the presence of fixed oxide charges. While the planar device shows less hysteresis overall, a larger hysteresis is observed post-stress compared to pre-stress; whereas the trench device has a larger hysteresis, but it narrows post-stress. For example, in case of the planar device,  $\Delta V_T$  (difference between down sweep and up sweep) at 1 nA drain current is increased from 0.5V to 1.0V (Fig. 5) where as  $\Delta V_T$  is decreased in trench device from 2.65V to 1.9V (Fig. 6). However, the trench device hysteresis is larger than that of the planar device for both cases. It is believed that some existing hole traps get filled in the trench device during stress, resulting in a decreased post-stress hysteresis and decreased  $\Delta V_T$ .

Fig. 5. Gate bias hysteresis of drain leakage for pre- and post- high voltage gate bias in a planar MOSFET structure.

Fig. 6. Gate bias hysteresis of drain leakage for pre- and post-high voltage gate bias in a trench MOSFET structure

## Quasi-static C-V measurement

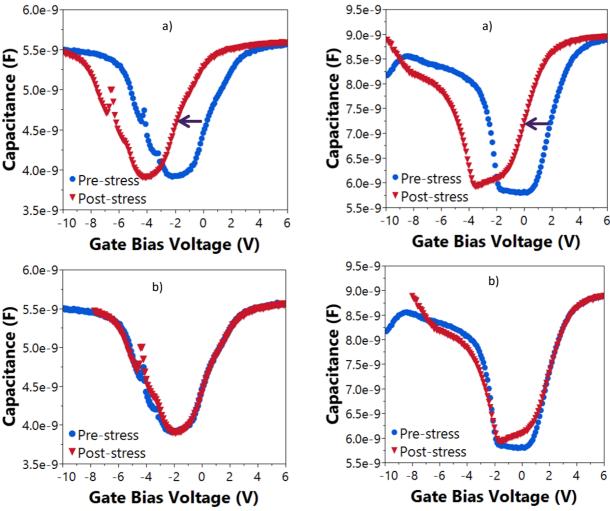

Figures 7 and 8 show quasi-static C-V characteristics for planar and trench devices pre- and post- V<sub>GS</sub> stress cycle. Gate bias voltage V<sub>GS</sub> has been swept from +6V (strong inversion) to -10V (accumulation) while capacitance values have been measured between gate and source-drain grounded together. At strong inversion with the channel fully turned on, quasi-static capacitance values are measured as 5.6 nF and 9 nF for planar and trench devices respectively and these values can be considered as gate oxide capacitance assuming there are no oxide charges. Lower capacitance values in the planar device compared to the trench can be attributed mostly to the estimated gate oxide thickness/active area difference. Figures 7a and 8a clearly show a net shift in C-V curves indicating the creation of fixed charges. The shifts in voltage have been calculated as 2.2V and 1.9V in planar and trench devices respectively by overlapping the C-V curves for pre- and post-stress conditions (see figures 7b and 8b). If we consider that there is negligible effect from interface states, one can approximate the additional fixed charge  $\Delta Q_f$  from the shift in C-V curve by using eq. 1 and 2 [15]

$$\Delta Q_f = Q_{f2} - Q_{f1} = \Delta V_{FB} C_{ox}$$

$$\Delta N_f = \Delta V_{FB} C_{ox} / Aq,$$

(1)

(2)

$$\Delta N_f = \Delta V_{FB} C_{ox} / Aq, \tag{2}$$

where  $Q_{f1}$  and  $Q_{f2}$  are fixed charges for pre- and post-stress conditions,  $V_{FB1}$  and  $V_{FB2}$  are pre- and post-flat-band voltages,  $C_{ox}$  is the oxide capacitance, A is area and q is electron charge. If we approximate  $\Delta V_{FB}$  as the net shift in C-V curve, additional fixed charge developed in planar and trench devices can be calculated using eq. 2. Thus, the additional fixed charge due to gate stress are found to be  $\Delta N_{f(P)} = 7.7 \times 10^{11} \text{cm}^{-2}$  in planar device and  $\Delta N_{f(T)} = 5.3 \times 10^{11} \text{cm}^{-2}$  in trench device. Note that these values are obtained with area and tox approximated. Similar values of added charges indicate similar mechanisms are prevalent in both planar and trench devices. In addition to fixed charges, other trap related effects are also occurring in the trench device (Fig. 8b.), as indicated by the change in shape of the C-V characteristics in the depletion portion of the curve. This change in shape infer some sort of degradation in the oxide for the trench device due to the high gate voltage stress. However, further investigation is required to understand these effects that is outside the scope of this comparative study.

**Fig. 7.** a) C-V (quasi-static) measurement of a planar MOSFET for pre- and post- high voltage gate bias. b) C-V (quasi-static) after shifting the post-stress curve horizontally to the right by 2.2V.

**Fig. 8.** a) C-V (quasi-static) measurement of a trench MOSFET for pre- and post- high voltage gate bias. b) C-V (quasi-static) after shifting the post-stress curve horizontally to the right by 1.9V [Other trap related effects into play].

## **Effect of Stress Duration and Multiple Stress Cycle**

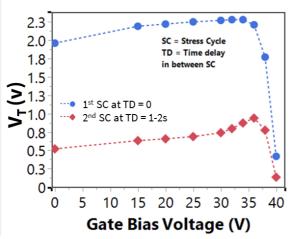

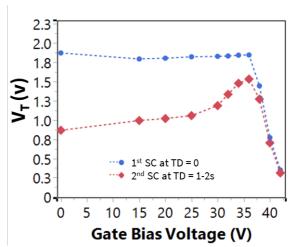

Figures 9 and 10 show the variation in  $V_T$  during multiple stress cycles ranging from 0V to 40V (planar) and 42V (trench). Every point in a particular stress cycle (SC) curve is the result of  $V_T$  measurement with a duration of 20 us after a single gate stress of 10 ms is applied. During the first stress cycle as indicated by TD = 0 in figures 9 and 10, similar PBTI related effects are observed as before and  $V_T$  trends towards higher values below the critical voltage. Albeit the gate stress pulse width is reduced from 6 s to 10 ms,  $V_T$  degrades in similar fashion above the critical voltage of the gate stress as observed in figures 3 and 4. However, critical voltage exhibits a higher value (36V for both planar and trench) as compared to a lower value (30V for planar and 32V for trench) for a 6 s stress pulse. This indicates that the degradation mechanism may also be influenced by the accumulation of total fixed charge along with the high electric field. After the first stress cycle, devices are immediately put under another SC (time delay, TD of 1-2 s) which shows some recovery in  $V_T$  after high voltage stress (first point in the SC curve at TD = 1-2 s) but

Fig. 10. (Trench) Gate bias is applied at each voltage for 10 ms and a subsequent read-out  $V_T$  is performed for 20 us in a stress cycle (SC) ranging from 0V to 42V. SC is repeated at time delay (TD)< 2s. Both SC curves follow similar pattern pointing to a single critical value at which  $V_T$  starts to decline.

follow similar trend of the first SC. In consecutive stress cycles both planar and trench devices start to show decline in  $V_T$  at the same voltage showing no shift in critical electric field even after several stress cycles.

#### **Conclusion**

To investigate the high voltage gate stress aspect of SiC MOSFETs, we study threshold voltage ( $V_T$ ) instability since the latter has been a major concern in SiC power devices. Our study shows a significant degradation in  $V_T$  under high electric field due to the creation of fixed charge at the SiO<sub>2</sub>/SiC interface in both planar and trench MOSFETs. Drain current hysteresis and quasi-static C-V have been used to approximately estimate fixed charges from the shift in hysteresis and C-V in preand post- stress measurements. We then modulate pulse duration and observe that threshold degradation may have dependency on total fixed charge accumulated in addition to the high electric field that initiates the creation of holes at the first place. In conclusion, we present the effect of high gate voltage stress on threshold voltage stability and suggest that gate bias stresses that cause excessive  $V_T$  shift should be avoided for highly accelerated gate stress tests.

## References

- [1] J. W. Palmour, L. Cheng, V. Pala, E. V. Brunt, D. J. Lichtenwalner, G-Y Wang, J. Richmond, M. O'Loughlin, S. Ryu, S. T. Allen, A. A. Burk and C. Scozzie, IEEE Int. Symp. on Power Semi. Dev. & IC's (ISPSD), 79-82 (2014).

- [2] D. J. Lichtenwalner, S.-H. Ryu, B. Hull, S. Allen, and J. W. Palmour, Materials Science Forum, 1090, 93-100 (2023).

- [3] T. Kimoto and H. Watanabe, Appl. Phys. Express 13, 120101 (2020).

- [4] G. Liu, B.R. Tuttle, and S. Dhar, Appl. Phys. Rev. 2, 021307 (2015).

- [5] D.J. Lichtenwalner, S. Sabri, E. van Brunt, B. Hull, S.-H. Ryu, P. Steinmann, A. Romero, S. Ganguly, D.A. Gajewski, S. Allen, and J.W. Palmour, IEEE International Integrated Reliability Workshop (IIRW), 1-6 (2020).

- [6] J. Berens and T. Aichinger, IEEE Int. Reliab. Phys. Symp. (IRPS), 1-5 (2021).

- [7] S. Zhu, T. Liu, L. Shi, M. Jin, H. L. R. Maddi, M. H. White, and A. K. Agarwal, IEEE Workshop on Wide Bandgap Power Dev. and Appl. (WiPDA), 1-4 (2021).

- [8] T. Watanabe, Y. Fukui, S. Hino, S. Tomohisa, N. Miura, and K. Nishikawa, IEEE Trans. on Dev. and Mat. Reliab. 23(1), 99-108 (2023).

- [9] L. Shi, T. Liu, S. Zhu, J. Qian, M. Jin, H. L. R. Maddi, M. H. White, and A. K. Agarwal, IEEE Workshop on Wide Bandgap Power Devices & Applications (WiPDA), 45-48, (2022).

- [10] S. Lombardo; J. H. Stathis; B. P. Linder; K. L. Pey; F. Palumbo; C. H. Tung, Journal of Appl. Phys. 98(12), 121301 (2005).

- [11] D. J. DiMaria, Solid-State Electr., 41(7), 957-965 (1997).

- [12] D. J. DiMaria; E. Cartier; D. Arnold, Journal of Appl. Phys. 73(7), 3367-3384 (1993).

- [13] M. V. Fischetti, D. J. DiMaria, S. D. Brorson, T. N. Theis, and J. R. Kirtley, Phys. Rev. B 31(12), 8124 (1985).

- [14] R. Singh, and A.R. Hefner, Solid-State Electr. 48, 1717-1720, (2004).

- [15] D. K. Schroder, Semiconductor materials and device characterization, 2<sup>nd</sup> edition, Wiley, (1998).