Revised: 2024-04-12 Accepted: 2024-04-15 Online: 2024-08-21

Submitted: 2023-08-02

# Design of Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> Gate Stack on Various Channel Planes for **High-Performance 4H-SiC Trench Power MOSFETs**

Linhua Huang<sup>1,a\*</sup>, Yong Liu<sup>1,b</sup>, Xin Peng<sup>1,c</sup>, Takashi Tsuji<sup>2,d</sup>, Yuichi Onozawa<sup>2,e</sup>, Naoto Fujishima<sup>2,f</sup>, and Johnny Kin On Sin<sup>1,g</sup>

<sup>1</sup>Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Clear Water Bay, Kowloon, Hong Kong, China

<sup>2</sup>Fuji Electric Co., Ltd, 4-18-1 Tsukama, Matsumoto, Nagano 390-0821, Japan

<sup>a</sup>lhunagat@connect.ust.hk, <sup>b</sup>yliueg@connect.ust.hk, <sup>c</sup>xpengaj@connect.ust.hk, dtsuji-takashi@fujielectric.com, eonozawa-yuichi@fujielectric.com, fujishima-naoto@fujielectric.com, geesin@ust.hk

Keywords: SiC trench gate power MOSFETs, high-k gate stack, interface state density, channel planes, channel mobility limiting mechanisms.

Abstract. An Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> gate stack is designed and implemented on various trench-gate channel planes for high-performance trench power MOSFETs. The designed high-k gate stack achieves a significant enhancement in the gate blocking capability (~1.73X) and maintains a low interface state density  $(D_{it})$ , in comparison to the SiO<sub>2</sub> gate. Moreover, owing to the implementation of the high-k gate stack, the high-k trench gate MOSFETs conduct a drain current of approximately 1.3 times larger than that of the SiO<sub>2</sub> trench gate MOSFETs on all 24 channel planes at the same overdrive voltage ( $V_{\rm gs}$ - $V_{\rm th}$ ) of 10 V. An analysis of the mobility limiting mechanisms on different channel planes reveals that the highest channel mobility on the  $(11\bar{2}0)$  channel plane is primarily due to its largest Coulomb scattering mobility and surface roughness scattering mobility.

# Introduction

The worldwide call for carbon neutrality has spurred a surge growth in demand for highperformance power semiconductor devices. Notably, SiC power MOSFETs have gained significant interest due to their impressive inherent material properties, including wide energy bandgap, high critical electric field, and large thermal conductivity. Despite their advantages, one vital problem preventing SiC power MOSFETs from achieving their theoretical expectations is the large channel resistance caused by the low channel mobility. One approach to lower the channel resistance is through the implementation of a trench-gate channel. However, the gate oxide at the trench bottom would experience a high electric field during reverse blocking, which causes a serious reliability concern. Fortunately, this issue can be overcome by the utilization of high-k gate dielectric [1]. Highk gate dielectric not only mitigates the electric field in the gate dielectric but also further reduces the channel resistance. A desirable high-k gate dielectric should not only have a high dielectric constant but also possess wide conduction and valence band offsets, as well as good thermal stability. However, the wide energy bandgap and high dielectric constant of a high-k material cannot be obtained simultaneously [2]. Therefore, a thin layer of SiO<sub>2</sub>, typically several nanometers thick, is usually formed before the high-k dielectric deposition to improve the suppression of gate leakage current. Al-based high-k dielectric is a possible candidate because of its high thermal stability and wide energy band gap [1]. Al<sub>2</sub>O<sub>3</sub> has been intensively investigated due to its relatively high energy band offsets and high crystallization temperature; however, it has only a moderate dielectric constant [3]. La<sub>2</sub>O<sub>3</sub> is known to be superior in terms of both the thermal dynamic stability and dielectric constant, but its valence band offset is not sufficiently high (0.9 eV) [4]. Intermixing of Al<sub>2</sub>O<sub>3</sub> with La<sub>2</sub>O<sub>3</sub> to form LaAlO<sub>3</sub> enhances the dielectric constant of Al<sub>2</sub>O<sub>3</sub>, which also maintains a relatively wide band gap and good thermal stability [4].

Based on above facts, an Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> gate stack on planar SiC MOSFETs has been demonstrated to achieve a 40% reduction in channel resistance, negligible transfer hysteresis, better threshold voltage stability, and longer short-circuit withstand time, compared to the conventional SiO<sub>2</sub> gate devices [5, 6]. In this paper, design of Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> gate stack on various channel planes for high-performance 4H-SiC trench power MOSFETs will be investigated to further explore the benefits of the high-k gate stack.

# **Experimental Details**

To design the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> gate stack for trench gates, two sets of MOS capacitors were fabricated on 4° off-axis n-type 4H-SiC (0001) Si-face wafers. The wafers had a 10-μm-thick epitaxial layer with a doping concentration of 1 × 10<sup>16</sup> cm<sup>-3</sup>. The wafers were diced into small samples and then cleaned by standard organic, Piranha, RCA cleaning and sacrificial oxidation process (1150°C dry oxidation and HF dip). The first set of four MOS capacitors had a single layer of SiO<sub>2</sub> and received different nitridation treatments. A 16-nm-thick SiO<sub>2</sub> layer was deposited and annealed at 1250°C in either 10% NO or 10% N<sub>2</sub>O ambient. The annealing durations are 30 mins, 70 mins, and 100 mins. The second set of three MOS capacitors had the same nitridation treatment but different gate dielectrics: namely SiO<sub>2</sub>, LaAlO<sub>3</sub>/SiO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> MOS capacitors. The SiO<sub>2</sub> MOS capacitor is a control sample, which is the sample built above with the NO annealing for 70 mins. The LaAlO<sub>3</sub>/SiO<sub>2</sub> MOS capacitor has a LaAlO<sub>3</sub> layer (40 nm) deposited by atomic layer deposition on the 70-min NO-annealed SiO<sub>2</sub> surface. The Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> MOS capacitor was fabricated with an additional step of O<sub>2</sub> annealing and a subsequent deposition of an Al<sub>2</sub>O<sub>3</sub> cover layer (10 nm) on top, in contrast to the LaAlO<sub>3</sub>/SiO<sub>2</sub> MOS capacitor.

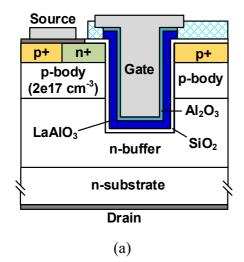

Alongside the fabrication of the MOS capacitors described above, SiC trench gate MOSFETs were also fabricated on 4° off-axis Si-face 4H-SiC wafers with an n-buffer layer and a p-type epilayer. The doping concentration and thickness of the n-buffer layer are  $5 \times 10^{18}$  cm<sup>-3</sup> and 1.5 µm, respectively. The doping concentration and thickness of the p-type epilayer are  $2 \times 10^{17}$  cm<sup>-3</sup> and 1 µm, respectively. Figures 1 (a) and (b) illustrate the structural diagram of the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> trench gate MOSFET and SEM image of the trench gate, respectively. After n+ and p+ regions were implanted and activated, the wafers were etched to form gate trenches, followed by sacrificial oxide growth and removal to reduce the lattice damages caused during the trench etching. Subsequently, the gate stack and ohmic contact were formed using the contact-first process, which was previously developed for fabricating Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> gate lateral MOSFETs [6]. It is worth noting that the ohmic contact is formed prior to the high-k gate stack formation. Particularly, the process utilized for forming the high-k gate stack of the trench gate MOSFETs is the same as the process used for building the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> MOS capacitor described above. SiO<sub>2</sub> trench gate MOSFETs were also

**Fig. 1.** (a) Structural diagram of Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> trench gate MOSFET and (b) SEM image of the trench gate.

fabricated as the control device, which had a capacitance equivalent thickness (CET) of 43 nm and received the same nitridation treatment as the  $Al_2O_3/LaAlO_3/SiO_2$  trench gate MOSFETs. The electrical properties of the MOSFETs were measured with Agilent 4156C precision semiconductor parameter analyzer. Effective electric field in the gate dielectric ( $E_{eff,ox}$ ) is calculated by ( $V_g$ - $V_{fb}$ )/CET, where  $V_{fb}$  is the flat band voltage. The gate voltage sweep rate in this study is 1 V/s. The channel length and width are 0.63  $\mu$ m and 100  $\mu$ m, respectively.

#### **Results and Discussion**

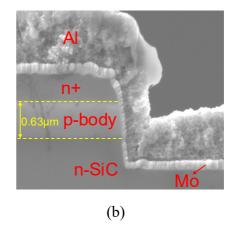

**Design of Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> gate stack.** The first set of the four MOS capacitors described above was used to optimize the deposited-SiO<sub>2</sub>/SiC interface. Figure 2 shows the interface state density ( $D_{it}$ ) for the deposited-SiO<sub>2</sub>/SiC interfaces. The MOS capacitor annealed in 10% NO for 70 mins shows the lowest  $D_{it}$  and longer duration has no further improvement on  $D_{it}$ . It is because that the 100-min 10% NO annealing provides excess nitrogen atoms diffused into the bulk SiO<sub>2</sub> layer near the interface, which degrades the interface quality [7]. Besides, the N<sub>2</sub>O annealing has an inferior passivation effect to that of the NO annealing under the same conditions on the deposited-SiO<sub>2</sub>/SiC interface. The cause for the inferior passivation effect is that the N<sub>2</sub>O annealing grows additional SiO<sub>2</sub> [8]. The additional SiO<sub>2</sub> growth at the interface generates carbon-related defects, compromising the passivation effect of the N<sub>2</sub>O annealing.

**Fig. 2.** (a) Energy distribution of  $D_{it}$  and (b) annealing duration vs  $D_{it}$ , at energy location of 0.25 eV below the conduction band edge for the four SiO<sub>2</sub> MOS capacitors.

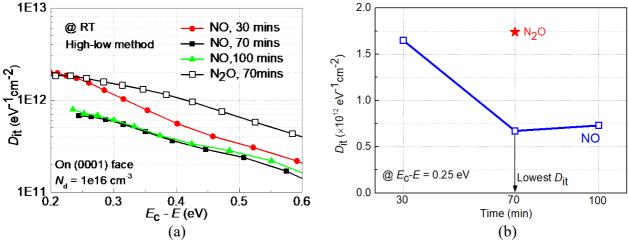

The second set of the three MOS capacitors described above was used to investigate the impact of the O<sub>2</sub> annealing on the deposited-SiO<sub>2</sub>/SiC interface. The O<sub>2</sub> annealing was employed to improve the high-k dielectric quality [5, 6]. Figure 3 (a) shows the *C-V* curves for the three MOS capacitors. The extracted dielectric constants from the *C-V* curves are 3.5, 8.2, and 21 for the SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and LaAlO<sub>3</sub>, respectively. Figure 3 (b) shows a significant enhancement in the gate blocking capability (~1.73X) achieved by employing the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> gate stack. Figure 3 (c) shows a slightly increase in *D*<sub>it</sub> for the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> MOS capacitor, which is possibly due to the additional O<sub>2</sub> annealing. Additional interface states would be generated during the O<sub>2</sub> annealing. This developed Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> gate stack was then implemented in various trench gate MOSFETs with different channel planes.

Fig. 3. (a) Bidirectional C-V curves measured at 1 MHz, (b) gate leakage current density ( $J_g$ ) plotted against  $E_{eff,ox}$ , and (c)  $D_{it}$  distribution at room temperature for the three MOS capacitors.

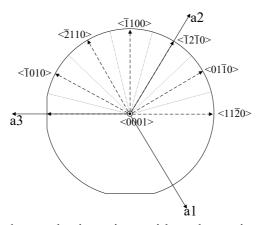

Electrical characteristics of the high-k trench gate MOSFETs. To investigate the electrical characteristics of various channel planes, the trench-gate channel planes were formed on 24 crystal orientations with each rotation being 15° apart, as shown in Fig. 4. Each trench gate MOSFET uses a single channel plane to investigate each crystal face individually.

Fig. 4. Investigated crystal orientations with each rotation being 15° apart.

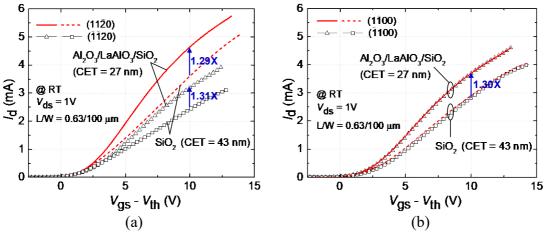

Figure 5 shows the transfer curves of the  $Al_2O_3/LaAlO_3/SiO_2$  and  $SiO_2$  trench gate MOSFETs on the four channel planes: (11 $\overline{2}0$ ), ( $\overline{11}20$ ), (1 $\overline{10}0$ ), and ( $\overline{11}00$ ). Under the same overdrive voltage ( $V_{gs-}V_{th}$ ) of 10 V, the drain current of the  $Al_2O_3/LaAlO_3/SiO_2$  trench gate MOSFET is approximately 1.3 times higher than that of the  $SiO_2$  device on the four channel planes. Among the four channel planes in either the  $Al_2O_3/LaAlO_3/SiO_2$  or  $SiO_2$  trench gate MOSFET, the largest drain current conducts on

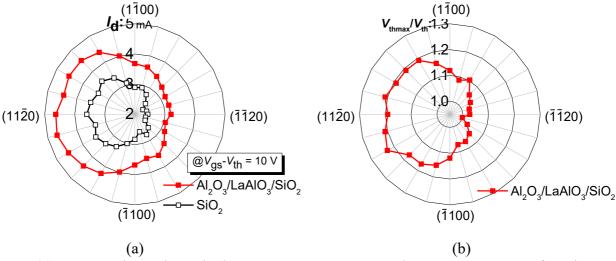

the (11 $\overline{2}0$ ) channel plane, and the (1 $\overline{1}00$ ) and ( $\overline{1}100$ ) channel planes conduct almost the same drain current at the same overdrive voltage. Figure 6 (a) shows that the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> trench gate MOSFET has enhanced drain current (~1.3X) on all 24 channel planes at the same overdrive voltage of 10 V. The channel planes near the (11 $\overline{2}0$ ) channel plane deliver a larger drain current compared to those near the ( $\overline{1}\overline{1}20$ ) channel plane. Figure 6 (b) shows the change in  $V_{\text{thmax}}/V_{\text{th}}$ , where  $V_{\text{thmax}}$  is the largest value of  $V_{\text{th}}$  among the 24 channel planes. The change in  $I_{\text{d}}$  (Fig. 6 (a)) is consistent with the change in  $V_{\text{thmax}}/V_{\text{th}}$  (Fig. 6 (b)). It is because that the larger interface state density on a channel plane would trap more electrons. The larger number of trapped electrons would cause a higher  $V_{\text{th}}$ , leading to a smaller  $V_{\text{thmax}}/V_{\text{th}}$ .

**Fig. 5.** Transfer characteristic  $I_d$  vs  $V_{gs}$ - $V_{th}$  at room temperature for four channel planes: (a)  $(11\overline{2}0)$  and  $(\overline{1}120)$ , and (b)  $(1\overline{1}00)$  and  $(\overline{1}100)$ .

**Fig. 6.** (a)  $I_{\rm d}$  on various channel planes at  $V_{\rm gs}$ - $V_{\rm th}$  = 10V and room temperature for SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> trench gate MOSFETs, and (b)  $V_{\rm thmax}/V_{\rm th}$  on various channel planes at room temperature for Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> trench gate MOSFETs.

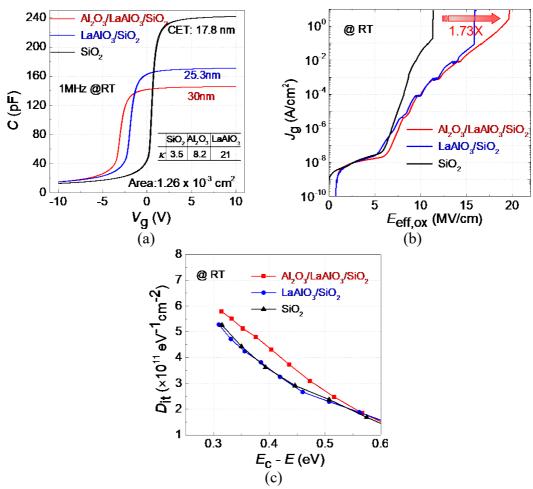

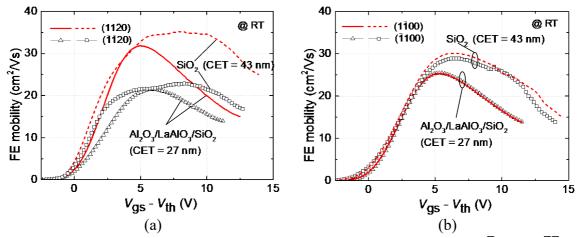

The drain current is related to both the gate capacitance and the channel mobility. To distinguish which one contributes to the higher drain current, the channel mobility of the trench gate MOSFETs is investigated. Figure 7 shows the field-effect (FE) channel mobility of the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> and SiO<sub>2</sub> trench gate MOSFETs on the four channel planes: (11\overline{2}0), (\overline{1}\overline{2}0), (1\overline{1}00), and (\overline{1}100). On the same channel plane, the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> device shows a slightly smaller peak channel mobility than that of the SiO<sub>2</sub> device. This is consistent with the  $D_{it}$  values for the two kinds of gates, as shown in Fig. 3 (c). The cause is most likely related to the O<sub>2</sub> annealing for the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> device, which can deteriorate the passivated deposited-SiO<sub>2</sub>/SiC interface and lead to a reduction in the channel mobility. Therefore, the higher drain current of the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> device is mainly

contributed by the higher gate capacitance. Nevertheless, the ( $1\bar{1}00$ ) channel plane of the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> trench gate MOSFET delivers an enhanced peak channel mobility (~1.25X) than the reported value (~20 cm<sup>2</sup>/Vs) [9] on the same channel plane, possibly due to the delicate NO annealing which helps the interface passivation. Furthermore, when comparing the channel mobility among the four channel planes in either Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> or SiO<sub>2</sub> trench gate MOSFET, the largest channel mobility exhibits on the ( $11\bar{2}0$ ) channel plane, and the ( $1\bar{1}00$ ) and ( $1\bar{1}00$ ) channel planes show almost the same channel mobility at the same overdrive voltage.

**Fig. 7**. FE mobility vs  $V_{gs}$ - $V_{th}$  at room temperature for four channel planes: (a)  $(11\overline{2}0)$  and  $(\overline{1}120)$ , and (b)  $(1\overline{1}00)$  and  $(\overline{1}100)$ .

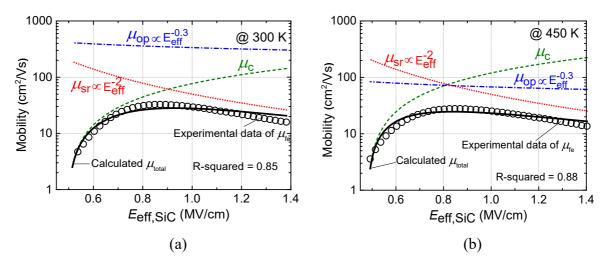

Channel mobility limiting mechanisms. To understand the channel mobility limiting mechanisms, modeling of these mechanisms is carried out. According to the reported results, the channel mobility is limited by Coulomb scattering, optical phonon scattering, and surface roughness scattering [9]. Therefore, Coulomb scattering mobility ( $\mu_c$ ), optical phonon scattering mobility ( $\mu_{op}$ ), and surface roughness scattering mobility ( $\mu_{sr}$ ), are taken into account to calculate the total mobility ( $\mu_{total}$ ) as shown below [9]:

$$\frac{1}{\mu_{\text{total}}} = \frac{1}{\mu_{\text{c}}} + \frac{1}{\mu_{\text{op}}} + \frac{1}{\mu_{\text{sr}}}$$

(1)

$$\mu_{\rm c} = \frac{\Gamma_{\rm C}T}{N_{\rm T}} \left(1 + \frac{N_{\rm S}}{N_{\rm scr}}\right)^{\zeta_{\rm C}} \tag{2}$$

$$\mu_{\rm sr} = \frac{\delta}{E_{\rm eff,SiC}^2} \tag{3}$$

$$\mu_{\text{op}} = C_{\text{op}} \cdot E_{\text{eff,SiC}}^n \cdot \left[ \exp\left(\frac{\hbar \omega_{\text{op}}}{kT}\right) - 1 \right]$$

(4)

$$E_{\text{eff,SiC}} = \frac{q}{\varepsilon_{\text{SiC}}} \cdot (N_{\text{dpl}} + \eta N_{\text{S}})$$

(5)

where  $N_{\rm T}$  is the total number of trapped charges, including fixed and interface trapped charges,  $N_{\rm S}$  is the surface carrier concentration,  $E_{\rm eff,SiC}$  is the effective field in the SiC, T is the absolute temperature,  $\hbar\omega_{\rm op}$  is the optical phonon energy, k is the Boltzmann constant,  $\varepsilon_{\rm SiC}$  is the permittivity of SiC,  $N_{\rm dpl}$  is the surface concentration of the depletion charges,  $\eta$  is taken to be 1/2 for electron mobility based on the Si mobility model, and  $\Gamma_{\rm C}$ ,  $N_{\rm scr}$ ,  $\zeta_{\rm C}$ ,  $\delta$ , n, and  $C_{\rm OP}$  are the empirical parameters [9]. The parameters used in fitting the mobilities for the four channel planes at temperatures ranging from 300K to 450K are listed in Table 1. On the (11 $\overline{2}0$ ) channel plane,  $\mu_{\rm c}$  is proportional to  $N_{\rm S}^{1.1}$ . However, on the other

three channel planes,  $\mu_c$  is proportional to  $N_{\rm S}^{1.0}$ . It means that fewer inversion carriers on the (11 $\overline{2}0$ ) channel plane would be affected by the Coulomb scattering. On the four channel planes,  $\mu_{\rm op}$  is proportional to  $E_{\rm eff,SiC}^{-0.3}$ , which is consistent with the reported result [9]. Moreover, the value of  $\delta$  of the (11 $\overline{2}0$ ) channel plane is larger than that of the other three channel planes, indicating that  $\mu_{\rm sr}$  is larger on the (11 $\overline{2}0$ ) channel plane.

**Table 1.** Parameters used in fitting the mobilities for four different channel planes at temperatures ranging from 300K to 450K

| Parameters          | Units                                                      | Channel planes |        |                 |

|---------------------|------------------------------------------------------------|----------------|--------|-----------------|

|                     |                                                            | (1120)         | (1120) | (1100) & (1100) |

| Γ <sub>C</sub>      | [K <sup>-1</sup> V <sup>-1</sup> s <sup>-1</sup> ]         | 1e10           | 5e10   | 2e10            |

| $N_{T}$             | [cm <sup>-2</sup> ]                                        | 3.4e13         | 4.8e13 | 4e13            |

| $N_{SCR}$           | [cm <sup>-2</sup> ]                                        | 1e10           | 5e10   | 1.5e10          |

| $\xi_{\rm C}$       |                                                            | 1.1            | 1.0    | 1.0             |

| δ                   | [Vs <sup>-1</sup> ]                                        | 5e13           | 3.8e13 | 4.3e13          |

| $\hbar \omega_{OP}$ | [eV]                                                       | 0.12           | 0.12   | 0.12            |

| n                   |                                                            | -0.3           | -0.3   | -0.3            |

| C <sub>OP</sub>     | [cm <sup>(n+2)</sup> V <sup>-(n+1)</sup> s <sup>-1</sup> ] | 2e2            | 2e2    | 2e2             |

**Fig. 8.** FE mobility vs  $V_{gs}$ - $V_{th}$  at room temperature for four channel planes: (a)  $(11\overline{2}0)$  and  $(\overline{1}120)$ , and (b)  $(1\overline{1}00)$  and  $(\overline{1}100)$ .

Figures 8 (a) and (b) show experimental data of the mobility on  $(11\bar{2}0)$  channel plane for the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> trench gate MOSFET at 300K and 450K, respectively. Calculated total mobility takes into account the contributions from Coulomb scattering mobility, optical phonon scattering mobility, and surface roughness scattering mobility. For all channel planes, the calculated total mobility is well agreed with the experimental data of the mobility. The values of the coefficient of determination (R-squared) for the mobility fittings are above 85% at various temperatures. The total mobility at each temperature is divided into the three components based on Equation (1), as shown in Fig. 8. At low  $E_{\text{eff,SiC}}$ , the Coulomb scattering is dominated; however, the surface roughness scattering is the limiting factor when  $E_{\text{eff,SiC}}$  is high. When the measured temperature is increased, the optical phonon scattering becomes severe.

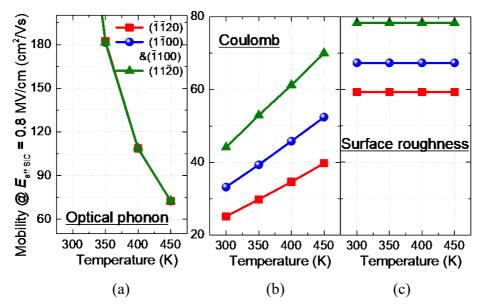

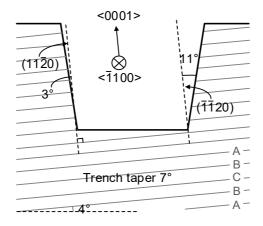

Figure 9 shows the three mobilities ( $\mu_{op}$ ,  $\mu_c$ , and  $\mu_{sr}$ ) against temperatures at  $E_{eff,SiC} = 0.8$  MV/cm for the Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> trench gate MOSFET.  $\mu_{op}$  is the same for the four channel planes, which is independent of channel faces. Among the four channel planes, the (11 $\bar{2}$ 0) channel plane has the largest  $\mu_c$  and  $\mu_{sr}$ . It is because that this channel plane achieves the least deviation from the

crystallographically accurate crystal plane [10], as shown in Fig. 10. The accurate crystal plane reduces surface roughness and dangling bonds [11]. Therefore, the taper angle of the trench sidewall can be tuned to achieve a precise  $(11\bar{2}0)$  channel plane to realize a higher channel mobility [12].

**Fig. 9.** Plots of the different mobilities against temperatures at  $E_{\text{eff,SiC}} = 0.8$  MV/cm for Al<sub>2</sub>O<sub>3</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub> trench gate MOSFET: (a) optical phonon scattering mobility, (b) Coulomb scattering mobility, and (c) surface roughness scattering mobility.

Fig. 10. Cross-sectional schematic of trench shape seen from  $<\overline{1}100>$  crystal direction.

# **Summary**

In this paper, the  $Al_2O_3/LaAlO_3/SiO_2$  gate stack was designed and implemented on various channel planes for using in trench gate MOSFETs. The passivation of the deposited-SiO<sub>2</sub>/SiC interface was first optimized, and it demonstrated that the NO annealing for 70 mins shows the lowest  $D_{it}$  and longer duration has no further improvement on  $D_{it}$ . Subsequently, the high-k gate stack on MOS capacitor was designed, which exhibits a considerable improvement in the gate blocking capability (~1.73X) and a slightly increased  $D_{it}$ , in comparison to the SiO<sub>2</sub> MOS capacitor. Finally, the high-k gate stack was implemented on various trench-gate channel planes. The high-k trench gate MOSFETs conduct a drain current ~1.3 times higher than that of the SiO<sub>2</sub> trench gate MOSFETs on all 24 channel planes at the same overdrive voltage of 10 V. Moreover, the mobility limiting mechanisms on various channel planes were discussed and analyzed. It turns out that the (11 $\bar{2}$ 0) channel plane has the largest Coulomb scattering mobility and surface roughness scattering mobility.

# Acknowledgement

The authors would like to thank the staff of Fuji Electric Company, Ltd., the staff of the Nanosystem Fabrication Facility (NFF) of HKUST, and the staff of the Materials Characterization and Preparation Facility (MCPF) of HKUST, for their technical advice and help in device fabrication and characterization. The authors appreciate the supports by Fuji Electric Company, Ltd., under Grant RDC 2021158-0, and the Research Grants Council of Hong Kong, under Research Impact Fund R6008-18.

# References

- [1] T. Hosoi, S. Azumo, Y. Kashiwagi, S. Hosaka, R. Nakamura, S. Mitani, Y. Nakano, H. Asahara, T. Nakamura, T. Kimoto, T. Shimura, and H. Watanabe, in International Electron Devices Meeting (2012), pp. 10-13.

- [2] M. Cabello, V. Soler, G. Rius, J. Montserrat, J. Rebollo, and P. Godignon, Materials Science in Semiconductor Processing, 78 (2017).

- [3] R. Suri, C.J. Kirkpatrick, D.J. Lichtenwalner, and V. Misra, Appl. Phys. Lett., 96, 042903 (2010).

- [4] M. Suzuki, T. Yamaguchi, N. Fukushima, and M. Koyama, J. Appl. Phys., 103, 034118 (2008).

- [5] L. Huang, Y. Liu, X. Peng, Y. Onozawa, T. Tsuji, N. Fujishima, and J.K.O. Sin, IEEE Trans. Electron Devices, 69, 2 (2022).

- [6] L. Huang, Y. Liu, X. Peng, T. Tsuji, Y. Onozawa, N. Fujishima, and J.K.O. Sin, IEEE Trans. Electron Devices, 70, 2 (2023).

- [7] T. Kimoto and H. Watanabe, Appl. Phys. Exp., 13, 120101 (2020).

- [8] T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology (Wiley, Singapore, 2014).

- [9] K. Kutsuki, Y. Watanabe, Y. Yamashita, N. Soejima, K. Kataoka, T. Onishi, K. Yamamoto, and H. Fujiwara, Solid-State Electronics, 157 (2019).

- [10]H. Yano, H. Nakao, H. Mikami, T. Hatayama, Y. Uraoka, and T. Fuyuki, Appl. Phys. Lett., 90, 042102 (2007).

- [11] K. Kutsuki, E. Kagoshima, T. Onishi, J. Saito, N. Soejima, and Y. Watanabe, in International Electron Devices Meeting (2019), pp. 20.3.1-20.3.4.

- [12] H. Yano, H. Nakao, T. Hatayama, Y. Uraoka and T. Fuyuki, Mater. Sci. Forum, 556-557 (2007).