24 The Author(s). Published by Trans Tech Publications Ltd, Switzerland.

Online: 2024-08-22

High Mobility 4H-SiC p-MOSFET via Ultrathin ALD B<sub>2</sub>O<sub>3</sub> Interlayer

Submitted: 2023-09-08

Revised: 2024-04-11

Accepted: 2024-04-12

# between SiC and SiO₂ Emran Ashik<sup>1,a\*</sup>, Veena Misra<sup>1,b</sup> and Bongmook Lee<sup>1,2,c</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, North Carolina State University, Raleigh NC 27606, USA

<sup>2</sup>College of Engineering, State University of New York Polytechnic Institute, Utica, NY 13502 USA <sup>a</sup>ekashik@ncsu.edu, <sup>b</sup>vmisra@ncsu.edu, <sup>c</sup>leeb1@sunypoly.edu

**Keywords:** SiC, MOSFET, Field Effect Mobility, CMOS, Atomic Layer Deposition, Transfer Characteristics, Density of Interface Traps, Threshold Voltage, Saturation Current, Leakage Current

**Abstract.** This article presents an innovative approach to achieve a high channel mobility for 4H-SiC p-MOSFET via dielectric-semiconductor interface engineering involving atomic layer deposition (ALD) of ultrathin B<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> stacks. The application of ultrathin boron oxide via ALD introduces a highly manufacturable solution for the passivation of SiC interface. The interface states near valence band reduces the channel mobility for SiC p-MOSFETs and increases the threshold voltage. The introduction of ultrathin B<sub>2</sub>O<sub>3</sub> interlayer reduces the threshold voltage and improves the field effect mobility to 12.60 cm<sup>2</sup>/Vs while the p-MOSFET without the interlayer provides the mobility of 8.91 cm<sup>2</sup>/Vs. This work also includes the optimization of the post-deposition annealing (PDA) conditions specific to ultrathin B<sub>2</sub>O<sub>3</sub> and bulk SiO<sub>2</sub> dielectric stack to obtain high field effect channel mobility for SiO<sub>2</sub>/SiC p-MOSFETs.

#### Introduction

Silicon Carbide (SiC) has emerged as a promising material for high temperature power electronics due to its capacity to function at extreme environment. The inherent capability to maintain operational efficiency at high temperature, high electric field and high radiation has spurred significant research endeavors in past few decades [1]. To address the challenges posed by extreme environments, researchers have been exploring wide bandgap materials as an alternative to traditional silicon technology for several decades [2], [3], [4], [5]. Among the various wide bandgap semiconductors, SiC stands out as having the greatest potential for achieving not only for power devices but also Complementary MOS technology and integrated power ICs for high-temperature and high voltage applications. This is mainly attributed to its capability for both p-type and n-type implantation, as well as its advanced level of process maturity. SiC's remarkable ability to function effectively at elevated and cryogenic temperatures also allows for the integration of control electronics on the wafer level alongside discrete high-power devices [6] resulting in the reduction of the need for costly cooling systems and minimizes space requirements, decreases gate driver delays, and enhances the overall stability of the system. SiC boasts significant advantages over silicon, including a higher critical electric field (approximately 10 times), a larger bandgap (roughly 3 times), and superior thermal conductivity (around 3 times). Remarkably, it maintains crystallographic similarity and bulk mobility with silicon, making SiC a more compelling option compared to other wide bandgap semiconductors. Its ability to offer low leakage currents and reduced conduction loss at high field and temperature has garnered considerable research interest in SiC CMOS technology [7], [8].

Integrated circuits (ICs) based on SiC have been successfully demonstrated on both 4H- and 6H-SiC substrates, surpassing the performance of silicon-based ICs at high temperatures [9], [10], [11], [12], [13], [14]. Nevertheless, the majority of SiC ICs rely primarily on n-MOSFETs, primarily due to the subpar performance of p-MOSFETs, which exhibit low field-effect mobility and high threshold voltage. Despite the numerous advantages offered by CMOS technology, such as faster high-to-low transitions thanks to the use of p-MOSFETs instead of load resistors, the ability to achieve pure logic zero and one, and improved noise immunity, there is a need to explore and develop high-performance p-MOSFETs. While SiC power MOSFETs are available in the market, and SiC ICs have been

demonstrated, their performance still falls short due to the presence of traps (D<sub>it</sub>) at the SiO<sub>2</sub>/SiC interface, which negatively impacts the inversion channel mobility [15]. In pursuit of this goal, several techniques have been successfully demonstrated to enhance the interface traps near the conduction band, ultimately leading to the development of high-mobility SiC n-MOSFETs or n-JFETs. These techniques and their details can be found in the review by *M. Cabello et al.* [16].

As of now, advancements in SiC p-MOSFET technology have not yielded a high-performance solution. The inherent low bulk hole mobility along with the traps near valence band is liable for poor p-MOSFET behavior. The performance of p-channel MOSFETs is heavily influenced by traps near the valence band, a characteristic that is challenging to predict using capacitance-voltage (CV) characteristics due to the extremely low inversion carrier concentration in MOS structures. Notably, the interface trap density near the valence band in SiO<sub>2</sub>/SiC MOS structures is considerably higher compared to that near the conduction band [17]. Reported literatures have very low mobility for p-MOSFETs due to aforementioned reason [2], [12], [18], [19], [20] and higher mobility has been obtained for the p-MOSFET with very low channel doping which is not feasible for CMOS application due to short channel effects. In this study, a highly manufacturable non-rare earth solution is presented, involving the use of a simple atomic layer deposition (ALD) technique to create an ultrathin boron oxide interlayer. This innovative approach has been shown to enhance the field-effect mobility and lower the threshold voltage of 4H-SiC p-MOSFETs. The results were compared to without boron oxide interlayer to emphasis on the importance of the interlayer. This report also includes the PDA parameters - annealing duration and annealing temperature optimization and establishes that 1100°C annealing for 30 minutes in diluted N<sub>2</sub>O/Ar environment for 30 minutes is the best post deposition annealing for SiO<sub>2</sub>/SiC p-MOSFET with boron oxide interlayer.

# **Experiments**

Lateral p-MOSFETs were fabricated on 4H-SiC epi layer grown 4° off-axis from 1120 plane. The epi layer doping  $3x10^{16}$  /cm³ to align with our previous CMOS results [6]. Aluminum ion implantation was performed on a 4-inch wafer to form the p+ junctions with a doping concentration of  $1x10^{19}$  /cm³ and annealed at 1700°C for 10 minutes for activation. The same wafer was then diced into 1.5 cm x

1.5 cm for gate oxide split conditions for the p-MOSFET fabrications, so they only have the oxide condition as varying parameter. The gate oxide split is shown in the table. 1. MOSCAPs were also fabricated. Unless otherwise specified, samples were cleaned with 3:1 piranha solution for 5 minutes followed by 10:1 BOE solution diluted by 50% in DI water for another 5 minutes prior to the dielectric deposition. 10 cycles of atomic layer deposition (ALD) of boron oxide were performed Tris(dimethylamino)borane at 52°C with (TDMAB) and O<sub>3</sub> precursors to form an ultrathin (0.5-0.8 nm) boron oxide followed by 300 cycles of ALD SiO<sub>2</sub> (38-40 nm) at 270°C using bis(diethylamino)silane (BDEAS) precursors. The samples were annealed at different split conditions in diluted (20%) N<sub>2</sub>O/Ar environment in a furnace.

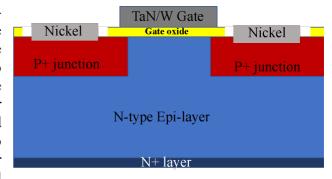

**Fig. 1**. Cross-sectional view of the p-MOSFETs presented in the report. Nickel junctions were used as source/drain and the N+ layer on the back side was used as the substrate contact. For the rest of the report, substrate and source is considered as ground (0V).

After the gate oxide formation and annealing, TaN and W were deposited to form gate electrode. The junctions were etched and 50 nm nickel was deposited to form source/drain contacts. The devices were annealed at 950°C for 45 seconds in rapid thermal annealing system for ohmic contact formation. The cross-sectional view of the p-MOSFETs is shown in Fig. 1.

| Sample #                                                                            | Piranha Clean<br>(minutes) | BOE Clean (minutes) | ALD                                              | PDA              |                    |

|-------------------------------------------------------------------------------------|----------------------------|---------------------|--------------------------------------------------|------------------|--------------------|

|                                                                                     |                            |                     |                                                  | Temperature (°C) | Duration (minutes) |

| 1                                                                                   | 5                          | 5                   | B <sub>2</sub> O <sub>3</sub> +SiO <sub>2</sub>  | 1100             | 60                 |

| 2                                                                                   |                            |                     | B <sub>2</sub> O <sub>3</sub> +SiO <sub>2</sub>  | 1100             | 30                 |

| 3                                                                                   |                            |                     | B <sub>2</sub> O <sub>3</sub> +SiO <sub>2</sub>  | 1100             | 15                 |

| 4                                                                                   |                            |                     | B <sub>2</sub> O <sub>3</sub> +SiO <sub>2</sub>  | 1000             | 60                 |

| 5                                                                                   |                            |                     | B <sub>2</sub> O <sub>3</sub> +SiO <sub>2</sub>  | 900              | 60                 |

| 6                                                                                   |                            |                     | B <sub>2</sub> O <sub>3</sub> +*SiO <sub>2</sub> | 1100             | 30                 |

| 7                                                                                   |                            |                     | SiO <sub>2</sub>                                 | 1100             | 60                 |

| 8                                                                                   |                            |                     | SiO <sub>2</sub>                                 | 1100             | 30                 |

| • Reduced physical thickness to obtain same EOT as SiO <sub>2</sub> only conditions |                            |                     |                                                  |                  |                    |

**Table 1.** Gate oxide split conditions.

#### **Results and Discussions**

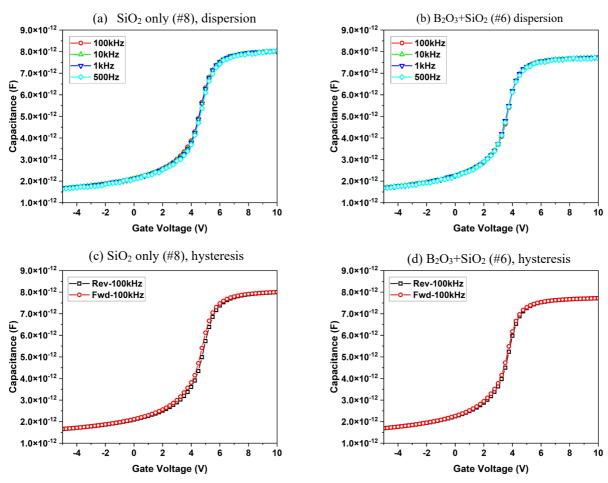

Initial Characterizations on MOS Capacitors. Metal-Oxide-Semiconductor (MOS) capacitors were fabricated in order to accurately measure the effective oxide thickness (EOT) which is very crucial for mobility calculation. Also, MOS capacitors provide a baseline for the interface quality for typical MOS structure. Fig. 2 (a) and (b) show the frequency dispersion of n-MOSCAP on SiO<sub>2</sub> only condition (#8) and ultrathin  $B_2O_3$  and SiO<sub>2</sub> bilayer condition (#6). Although both conditions show excellent frequency dispersion behavior, boron treated sample exhibits slightly better dispersion characteristics. Boron treated sample also shows less hysteresis as compared to the sample without boron incorporation. The amount of  $\Delta V_{FB}$  from the hysteresis plot (Fig. 2(c) and (d)) is 0.085 V and 0.149 V for capacitors with and without boron incorporation respectively. All measurements were performed at room temperature. CV characteristics were carried out for all the conditions presented in the study and effective oxide thickness was extracted using [21].

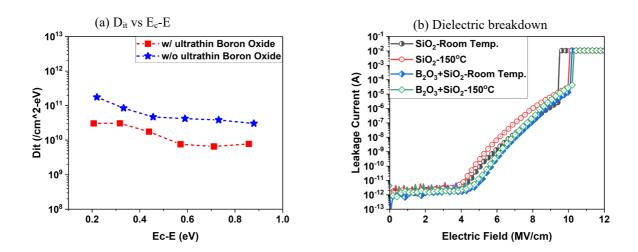

Fig. 3 (a) shows the density of interface states from the frequency dispersion data. The D<sub>it</sub> was extracted using Terman method using 100kHz frequency C-V as C<sub>HF</sub> and 500 Hz frequency C-V as C<sub>LF</sub> [22]. Although this assumption of low frequency CV underestimate the Dit value since it ignores the traps with a lifetime of 2 ms or more, it provides a good qualitative understanding about the interface quality with boron incorporation. One drawback with ALD SiO<sub>2</sub> process is the requirement of high temperature post deposition anneal (PDA) in order to densify the dielectric and anneal out all the defects inside the SiO<sub>2</sub> dielectric. This high temperature PDA process causes a growth of low quality oxide at SiO<sub>2</sub>/SiC interface [23]. Our hypothesis is that the ultrathin boron oxide prevents this low quality oxidation via SiO<sub>2</sub> and B<sub>2</sub>O<sub>3</sub> reaction which reduces the density of interface traps. This argument is further attested in Fig. 3(b) that shows the leakage current characteristics at room temperature as well as at 150°C of the MOS capacitors. Boron incorporated samples have better gate leakage characteristic compared to SiO<sub>2</sub> only conditions. Incorporation of ultrathin Boron did not alter the breakdown strength as the breakdown field is little over 10MV/cm. At higher temperature, since there are more thermally generated carriers, more interface traps get activated resulting higher Fowler-Nordheim (FN) tunneling currents [24] for all conditions.

**Fig. 2.** Room temperature Capacitance vs Voltage Characteristics. (a) and (b) are C-V characteristics at different frequencies. (c) and (d) are the hysteresis behavior conducted at 100 kHz frequency.

Fig. 3. (a) density of interface traps extracted using Terman method. (b) Gate oxide breakdown comparison for boron incorporated and SiO<sub>2</sub>-only conditions at room temperature and 150°C.

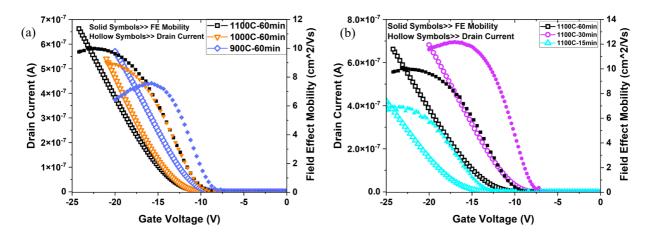

**Optimization of Post deposition annealing (PDA).** Fig. 4 (a) shows the transfer characteristics of p-MOSFET with boron incorporated sample annealed at 900°C, 1000°C, and 1100°C. The mobility of 900°C annealed sample is 7.64 cm²/V-s. This low mobility is possibly originated from lack of densification and oxygen vacancy reduction due to lower temperature [25] and the un-passivated B<sub>2</sub>O<sub>3</sub> at the interface that acts as trapping centers. As the annealing temperature increased to 1000°C,

the mobility improves to 9.01 cm<sup>2</sup>/Vs indicating better interface. 1100°C annealing improves the mobility further to 10.18 cm<sup>2</sup>/V-s. The threshold voltages for 900°C, 1000°C and 1100°C were -11.33, -13.79 and -13.97 V which is due to larger EOT formed during higher temperature oxidations. It is noted that the mobility of boron incorporated p-MOSFET reduced when annealed at 1200°C (not shown). Therefore, 1100°C PDA provides the best annealing temperature for 0.5 nm boron incorporation (10 cycle).

**Fig. 4.** (a) Transfer characteristics of 10 cycles boron oxide and 300 cycles SiO<sub>2</sub> with 900-1100°C PDA for 60 minutes (samples #1, #4 and #5). (b) Transfer characteristics of condition #1, #2 and #3. 60 minutes anneal is too long and produces low quality oxide with carbon related clusters while 15 minutes anneal is too short for the densification of SiO<sub>2</sub>

Fig. 4 (b) shows the transfer characteristics ( $I_D$  vs.  $V_{GS}$ ) of the p-MOSFET annealed at  $1100^{\circ}C$  in  $N_2O/Ar$  (20%  $N_2O$ ) with three different anneal times 15, 30, and 60 minutes). 15 minutes of anneal time is not enough as the mobility value of  $6.95~cm^2/Vs$  with a large threshold voltage of -16.51 V. The mobility of this condition ( $1100^{\circ}C$  15 minutes) is less than  $1000^{\circ}C$  60 minutes. In addition, 15 minutes of annealing time is short duration to densify  $SiO_2$ . Sample with 30 minutes anneal produces the highest mobility of  $12.23~cm^2/Vs$  and low threshold voltage of -12.23 V. It was found that 60 minutes of annealing actually decrease the mobility to  $10.18~cm^2/V$ -s and the threshold voltage increases to -13.97V. This can be explained by the fact that oxidation takes over the SiC interface and dilute the effect of boron passivation. We have observed the same effect with  $La_2O_3$  passivation on SiC [26].

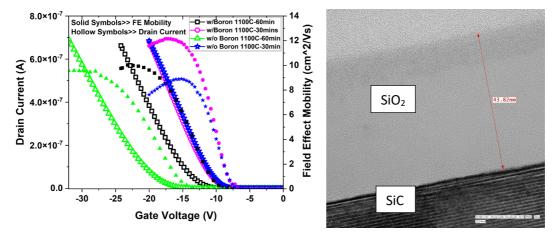

Effect of Ultrathin Boron Oxide. Since the 1100°C annealed sample is the best with 0.5nm boron incorporation, we keep our focuses on the 1100°C annealed conditions only. Fig. 5 (a) compares the mobility with and without boron oxide after 1100°C annealing. 300 cycles of ALD deposited 38nm SiO<sub>2</sub>. When PDA is done at 1100C in N<sub>2</sub>O/Ar environment, densification, N<sub>2</sub>O passivation, and oxidation occur at the same time. The longer the sample was annealed, the thicker the gate oxide. There was 4 nm increase in oxide thickness after 30 minutes of annealing (#8) at 1100°C whereas there was 17 nm increase in oxide thickness for the 60 minutes of annealing (#7). This increase in oxide thickness also increases in threshold voltage as seen in Figure 5 (a). 30 minutes of annealing is not the most optimized condition for boron-free conditions as it lacks densification of ALD SiO<sub>2</sub>. The EOTs extracted for boronated SiO<sub>2</sub> conditions are 51.66 nm (#1) and 49.76 nm (#2). The ultrathin boron oxide interlayer does not form borosilicate layer like lanthanum oxide interlayer [26] as there is no solid solubility line in the phase diagram of B<sub>2</sub>O<sub>3</sub>-SiO<sub>2</sub> [27]. According the Gibbs' free energy of formation [28] boron oxide breaks down and supply free oxygen to the SiO<sub>2</sub>/SiC interface. Oxygen further reduces the oxygen vacancies along with the N<sub>2</sub>O annealing while free boron possibly passivates  $\pi$ -bonded carbon clusters by reducing the charges of  $\pi$ -bonds. A TEM image of sample #6 is shown in Fig. 5 (b). Unlike common SiO<sub>2</sub>/SiC interfaces [29], there is a much smooth transition from SiC to SiO<sub>2</sub> which indicates the boron oxide incorporation suppresses the low-quality

oxidations. Boron was not detected due to the size of the boron atoms. The inclusion of boron oxide at the interface forms a boron-rich interfacial oxide that counteracts the SiC/SiO<sub>2</sub> interface traps and provides enhancement of FE mobility in the SiC p-MOSFETs. The FE mobility of boron-free samples are 8.91 cm<sup>2</sup>/Vs (30 minutes annealed) and 9.61 cm<sup>2</sup>/Vs (60 minutes annealed).

**Fig. 5.** (a) Mobility enhancement with ultrathin boron oxide interlayer between SiC and bulk SiO<sub>2</sub>. The transfer characteristics are compared for 30 minutes, and 60 minutes anneal devices with their corresponding boron-free devices. (b) TEM image of boron incorporated sample (1100°C-30 minute).

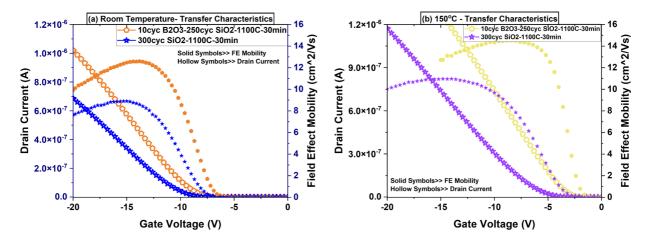

As we observe from the boron-free conditions (#7 and #8) that 300 cycles SiO<sub>2</sub> require more than 30 minutes of annealing, and 1100°C 30 minutes annealed samples with and without boron incorporation has a large EOT difference, so the bulk SiO<sub>2</sub> ALD deposition cycle was reduced from 300 (#2) to 250 (#6), which results in similar EOT as the SiO<sub>2</sub>-only conditions. The field effect mobility of boron-incorporated samples further improves as the thickness of bulk SiO<sub>2</sub> is reduced and it has enough thermal budget for densification. The highest mobility condition is thereby observed at a value 12.60 cm<sup>2</sup>/Vs with threshold voltage going to the lowest 9.15 V due to suppressed interfacial oxidation and better densification. The transfer characteristics of boron-incorporated and boron-free device with EOT-matched conditions at room temperature and 150°C measurement temperature are presented in Fig. 6. Notably, the FE mobility increases from 12.60 cm<sup>2</sup>/Vs to 14.5 cm<sup>2</sup>/Vs and the threshold voltage reduces form -9.15 V to -3.65 V for the boron-incorporated samples while similar trend is observed for all other conditions. This indicates the FE mobilities reported here are still coulombic scattering limited.

**Fig. 6.** Transfer characteristics at (a) room temperature and (b) elevated temperature (150°C). 30 minutes annealed with and without boron oxide conditions (#6 and #8) are compared. The threshold voltage decreases, and the FE mobility increases which indicates the mobility is coulombic scattering limited.

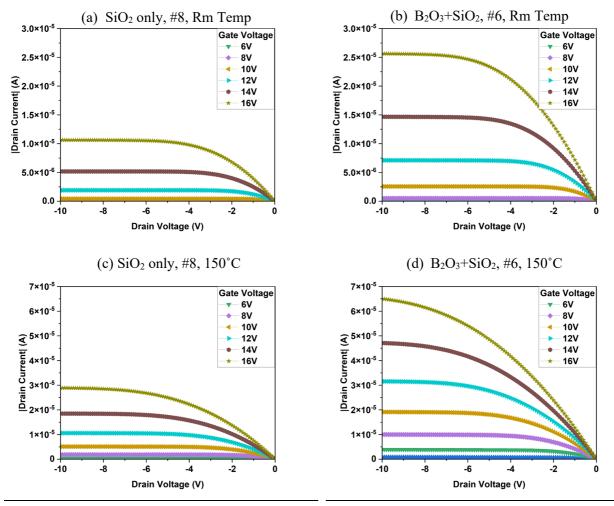

The output characteristics ( $I_D$  vs  $V_{DS}$ ) of the 30-minute annealed device with (#6) and without (#8) boron incorporation is presented in Fig. 7. The saturation current is doubled due to a combination of mobility enhancement and threshold voltage decrease with same oxide capacitance.

**Fig. 7.** The output characteristics (I<sub>D</sub> vs V<sub>DS</sub>) of 300 cycles ALD SiO<sub>2</sub>-1100°C annealed 30 minutes at (a) room temperature and (c) elevated temperature and 10 cycles ALD B<sub>2</sub>O<sub>3</sub>+250 cycles ALD SiO<sub>2</sub>-1100°C annealed 30 minutes samples at (b) room temperature and (d) elevated temperature.

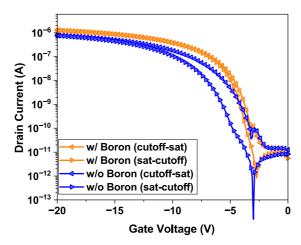

To thoroughly assess the enhancement of interface properties through the incorporation of a boron oxide interlayer, we analyzed the samples with (sample #6) and without (sample #8) this interlayer in MOSFETs' transfer characteristics. This analysis focused on observing the hysteresis of the transfer characteristics in log scale, as depicted in Fig. 8. The transfer characteristics were evaluated, transitioning from the cut-off region to the saturation region and then back from saturation to cut-off. Remarkably, the samples with the boron oxide interlayer exhibited a significantly reduced hysteresis, less than 0.3V, in contrast to those without the interlayer, which demonstrated a hysteresis greater than 1.6V. This substantial reduction highlights the efficacy of the boron oxide passivation approach in mitigating oxygen vacancies and passivating  $\pi$ -bonded carbon clusters. Consequently, this technique anticipates significant enhancement in the reliability of ALD SiO<sub>2</sub> layers for SiC MOS transistors, showcasing the pivotal role of boron oxide in interface improvement.

**Fig. 8.** The hysteresis of transfer characteristics in log scale. Samples with boron interlayer (#6) show 0.299V while samples without the interlayer (#8) show 1.6V of hysteresis in the log scale transfer characteristics in room temperature.

#### Conclusion

This paper reports a new method to boost the performance of SiC p-MOSFETs by passivation of the interface states using ultrathin boron oxide interlayer. The use of ALD boron oxide provides a practical way to incorporate SiC into CMOS technology without relying on rare-earth materials. This solution helps overcome two main issues with SiC p-MOSFETs: high threshold voltage and low channel mobility. The improved mobility due to the ultrathin boron oxide treatment suggests better interface conditions, which could help reduce instability under harsh conditions, although further research is needed in the future. Importantly, our tests at 150°C showed that the device maintains its performance avoiding any temperature related degradations.

## Acknowledgement

This work was funded by Advanced Research Projects Agency-Energy (ARPA-E) U.S. Department of Energy, under Award Number DE-AL0001028.

## References

- [1] W. J. Choyke and G. Pensl, "Physical Properties of SiC," *MRS Bull.*, vol. 22, no. 3, pp. 25–29, Mar. 1997, doi: 10.1557/S0883769400032723.

- [2] L. Yang *et al.*, "Analysis of Mobility for 4H-SiC N/P-Channel MOSFETs Up To 300 °C," *IEEE Trans. Electron Devices*, vol. 68, no. 8, pp. 3936–3941, Aug. 2021, doi: 10.1109/TED.2021.3084908.

- [3] T.-K. Nguyen *et al.*, "Highly sensitive 4H-SiC pressure sensor at cryogenic and elevated temperatures," *Mater. Des.*, vol. 156, pp. 441–445, Oct. 2018, doi: 10.1016/j.matdes.2018.07.014.

- [4] T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications. John Wiley & Sons, 2014.

- [5] A. Hassan, Y. Savaria, and M. Sawan, "GaN Integration Technology, an Ideal Candidate for High-Temperature Applications: A Review," *IEEE Access*, vol. 6, pp. 78790–78802, 2018, doi: 10.1109/ACCESS.2018.2885285.

- [6] S. B. Isukapati *et al.*, "Monolithic Integration of Lateral HV Power MOSFET with LV CMOS for SiC Power IC Technology," in *2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, May 2021, pp. 267–270. doi: 10.23919/ISPSD50666.2021.9452235.

- [7] J. O. Gonzalez, R. Wu, S. Jahdi, and O. Alatise, "Performance and Reliability Review of 650 V and 900 V Silicon and SiC Devices: MOSFETs, Cascode JFETs and IGBTs," *IEEE Trans. Ind. Electron.*, vol. 67, no. 9, pp. 7375–7385, Sep. 2020, doi: 10.1109/TIE.2019.2945299.

- [8] L. F. S. Alves, P. Lefranc, P.-O. Jeannin, and B. Sarrazin, "Review on SiC-MOSFET devices and associated gate drivers," in 2018 IEEE International Conference on Industrial Technology (ICIT), Feb. 2018, pp. 824–829. doi: 10.1109/ICIT.2018.8352284.

- [9] M. Alexandru *et al.*, "SiC Integrated Circuit Control Electronics for High-Temperature Operation," *IEEE Trans. Ind. Electron.*, vol. 62, no. 5, pp. 3182–3191, May 2015, doi: 10.1109/TIE.2014.2379212.

- [10] C.-M. Zetterling, L. Lanni, R. Ghandi, B. G. Malm, and M. Östling, "Future high temperature applications for SiC integrated circuits," *Phys. Status Solidi C*, vol. 9, no. 7, pp. 1647–1650, 2012, doi: 10.1002/pssc.201100689.

- [11] D. T. Clark *et al.*, "High Temperature Silicon Carbide CMOS Integrated Circuits," *Mater. Sci. Forum*, vol. 679–680, pp. 726–729, 2011, doi: 10.4028/www.scientific.net/MSF.679-680.726.

- [12] K. Moges, T. Hosoi, T. Shimura, and H. Watanabe, "Demonstration of 4H-SiC CMOS circuits consisting of well-balanced n- and p-channel MOSFETs fabricated by ultrahigh-temperature gate oxidation," *Appl. Phys. Express*, vol. 14, no. 9, p. 091006, Aug. 2021, doi: 10.35848/1882-0786/ac1c43.

- [13] P. G. Neudeck *et al.*, "Extreme temperature 6H-SiC JFET integrated circuit technology," *Phys. Status Solidi A*, vol. 206, no. 10, pp. 2329–2345, 2009, doi: 10.1002/pssa.200925188.

- [14] W. Xie, J. A. Cooper, and M. R. Melloch, "Monolithic NMOS digital integrated circuits in 6H-SiC," *IEEE Electron Device Lett.*, vol. 15, no. 11, pp. 455–457, Nov. 1994, doi: 10.1109/55.334665.

- [15] A. M. Vidarsson, J. R. Nicholls, D. Haasmann, S. Dimitrijev, and E. Ö. Sveinbjörnsson, "Detection of near-interface traps in NO annealed 4H-SiC metal oxide semiconductor capacitors combining different electrical characterization methods," *J. Appl. Phys.*, vol. 131, no. 21, p. 215702, Jun. 2022, doi: 10.1063/5.0086974.

- [16] M. Cabello, V. Soler, G. Rius, J. Montserrat, J. Rebollo, and P. Godignon, "Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review," *Mater. Sci. Semicond. Process.*, vol. 78, pp. 22–31, May 2018, doi: 10.1016/j.mssp.2017.10.030.

- [17] E. K. Ashik *et al.*, "Bias Temperature Instability on SiC n- and p-MOSFETs for High Temperature CMOS Applications," in *2022 IEEE International Reliability Physics Symposium (IRPS)*, Mar. 2022, p. 3B.4-1-3B.4-8. doi: 10.1109/IRPS48227.2022.9764565.

- [18] M. Okamoto, M. Tanaka, T. Yatsuo, and K. Fukuda, "Fabrication of 4H-SiC p-Channel MOSFET with High Channel Mobility," *Mater. Sci. Forum*, vol. 527–529, pp. 1301–1304, 2006, doi: 10.4028/www.scientific.net/MSF.527-529.1301.

- [19] H. Nemoto *et al.*, "Conduction mechanisms of oxide leakage current in p-channel 4H-SiC MOSFETs," *Jpn. J. Appl. Phys.*, vol. 59, no. 4, p. 044003, Mar. 2020, doi: 10.35848/1347-4065/ab7ddb.

- [20] M. Florentín, "Irradiation impact on optimized 4H-SiC MOSFETs," Doctoral thesis, Universitat Politècnica de Catalunya, 2016. Accessed: Nov. 01, 2022. [Online]. Available: https://upcommons.upc.edu/handle/2117/96353

- [21] J. R. Hauser and K. Ahmed, "Characterization of ultra-thin oxides using electrical C-V and I-V measurements," *AIP Conf. Proc.*, vol. 449, no. 1, pp. 235–239, Nov. 1998, doi: 10.1063/1.56801.

- [22] D. K. Schroder, Semiconductor Material and Device Characterization. John Wiley & Sons, 2015.

- [23] P. Fiorenza, F. Giannazzo, and F. Roccaforte, "Characterization of SiO2/4H-SiC Interfaces in 4H-SiC MOSFETs: A Review," *Energies*, vol. 12, no. 12, Art. no. 12, Jan. 2019, doi: 10.3390/en12122310.

- [24] R. Kies, C. Papadas, G. Pananakakis, and G. Ghibaudo, "Temperature Dependence of Fowler-Nordheim Emission Tunneling Current in MOS Structures," in *ESSDERC '94: 24th European Solid State Device Research Conference*, Sep. 1994, pp. 507–510.

- [25] X. Yang, B. Lee, and V. Misra, "Electrical Characteristics of SiO2 Deposited by Atomic Layer Deposition on 4H–SiC After Nitrous Oxide Anneal," *IEEE Trans. Electron Devices*, vol. 63, no. 7, pp. 2826–2830, Jul. 2016, doi: 10.1109/TED.2016.2565665.

- [26] M. S. Kang, K. Lawless, B. M. Lee, and V. Misra, "Effect of High Temperature Forming Gas Annealing on Electrical Properties of 4H-SiC Lateral MOSFETs with Lanthanum Silicate and ALD SiO2 Gate Dielectric," *Mater. Sci. Forum*, vol. 924, pp. 482–485, 2018, doi: 10.4028/www.scientific.net/MSF.924.482.

- [27] M. A. Azim, B. Gorr, H.-J. Christ, M. Heilmaier, U. Koch, and M. Engelhard, "Characterization of Oxidation Kinetics of Mo–Si–B-Based Materials," *Oxid. Met.*, vol. 87, no. 1, pp. 89–108, Feb. 2017, doi: 10.1007/s11085-016-9659-3.

- [28] J. G. Speight, Ed., *Lange's Handbook of Chemistry*, 17th Edition. McGraw-Hill Education, 2017. Accessed: Mar. 19, 2024. [Online]. Available: https://www.accessengineeringlibrary.com/content/book/9781259586095

- [29] T. Zheleva, A. Lelis, G. Duscher, F. Liu, I. Levin, and M. Das, "Transition layers at the SiO2/SiC interface," *Appl. Phys. Lett.*, vol. 93, no. 2, p. 022108, Jul. 2008, doi: 10.1063/1.2949081.