# Increasing 4H-SiC Trench Depth by Improving the Dry Etch Selectivity towards the Oxide Hard Mask

Submitted: 2023-09-15

Revised: 2024-05-08

Online: 2024-08-22

Accepted: 2024-05-09

Oleg Rusch<sup>1, a\*</sup>, Kevin Brueckner<sup>1, b</sup> and Tobias Erlbacher<sup>2, c</sup>

<sup>1</sup>Fraunhofer Institute for Integrated Systems and Device Technology IISB, Erlangen, Germany <sup>2</sup>Chair of Electron Devices, University of Erlangen-Nuremberg, Erlangen, Germany

aoleg.rusch@iisb.fraunhofer.de, bkevin.brueckner@iisb.fraunhofer.de, ctobias.erlbacher@fau.de

Keywords: 4H-SiC, Trench, Dry Etching, ICP, Selectivity, TrenchMOS, FIB

**Abstract.** This work presents the results of process development for trench formation in SiC power devices to increase the trench depth by improving SiC/SiO<sub>2</sub>-selectivity of the dry etch process. Motivation behind this development is to further improve the electrical properties of conventional devices like SiC MOSFETs by implementing a trench geometry, allowing the cell pitch to be increased, leading to a reduced on-resistance of SiC TrenchMOS devices. Trench etching was performed on 4H-SiC substrates by utilizing an oxide hard mask, patterned by photolithography and dry etching. The SiC trench profile was analyzed by cross-section preparation via FIB and SEM imaging. The highest SiC/SiO<sub>2</sub>-selectivity achieved was 7.9, with SiF<sub>4</sub> gas flow being the most decisive parameter for it. With that, the selectivity of the standard SiC trench etch process was increased by nearly five times. SiC trenches with depths of 5 μm could be demonstrated. However, then the structural fidelity was deteriorated, with micro-trenching and sidewall bowing being the largest limitations regarding applicable trench depth in SiC power devices.

#### Introduction

Minimization of power losses is key for continuous improvement of power devices to exploit the full physical potential of SiC and to meet the requirements for power density, efficiency, robustness as well as costs. Semiconductor devices based on SiC like MOSFETs are major components in power electronics and thus are widely established on the market. Due to its material properties, SiC enables the fabrication of fast switching power devices with simultaneously low power losses compared to their Silicon counterparts. However, SiC semiconductor devices are comparatively new, so there is still great potential for improvement in both device and process technology. Research into novel device concepts is intended to improve the performance and efficiency of existing devices and enables applications beyond the conventional performance limits, counteracting the high material costs and tackling nowadays challenges in digitalization and the transition to renewable energy sources [1-3].

One approach towards further development of conventional SiC power MOSFETs is to introduce vertical instead of horizontal channels by implementing a trench structure in the active region of the devices, thereby fabricating SiC TrenchMOS devices. Due to the reduced cell pitch by eliminating the JFET region, integration density can be increased. Moreover, the formation of the channel on the trench sidewall can also improve the mobility of the channel, leading to a reduction in on-resistance and therefore contributing to higher device efficiency, chip area savings, and ultimately a reduction in cost per component. Additionally, deep trenches in SiC may be used for the implementation of super-junction patterns in power devices and deep trench isolation in SiC CMOS technology [1-3].

Due to the device architecture of the TrenchMOS, one of the parameters that inevitably affects the channel length is the trench depth. Since a minimum channel length is required for the desired transistor characteristics, a minimum trench depth is mandatory. However, due to the physical hardness and chemical inertness of the semiconductor material, trench implementation in SiC proves to be challenging. For SiC TrenchMOS fabrication, a trench topography is created via plasma dry etching. Although wet chemical approaches for etching SiC could be demonstrated, they are not

suitable for the reliable generation of trenches due to the difficult-to-control process parameters. However, proper trench geometry is crucial for the functionality of the corresponding device [1-3].

In general, etching processes are used in semiconductor technology to remove layers over the entire surface or to transfer lithographically patterned structures. The type of etching process has a significant influence on the resulting etching profile and the over-etching into the substrate beneath. Wet chemical etching processes are generally characterized by high selectivity. The etching rates can be controlled by matching the etching chemicals and selecting the appropriate etching masks, respectively. This ensures a high selectivity and thus protects the substrate surface. However, wet etching processes usually exhibit an isotropic, i.e. direction-independent etching effect and thus a homogeneous material removal in all spatial directions, which results in an under-etching of the etching mask and consequently a loss of resolution. The high isotropy of wet-chemical etching processes therefore prevents dimensionally stable pattern transfer in sizes of a few micrometers and thus limits their possible applications for semiconductor device fabrication because of the ever-increasing miniaturization of structure sizes. In contrast to this, dry etching processes generally etch strongly anisotropic, i.e. strongly directional with no or almost no under-etching of the etching mask. As a result of the directional etching attack, the to be etched material ideally is transferred in conformity with the patterned mask without loss of structure [3-6].

In the context of this work, wet chemical etching processes were only used for the removal of already patterned photoresist or oxide masks over the entire surface, which acted as protective masks for the oxide or SiC trench etching. The structuring of the utilized oxide hard mask as well as the SiC structuring itself was carried out by dry etching due to the high resolution, sidewall angles and aspect ratios that can be achieved. The purpose of this work was to investigate the influence of dry etching parameters on the SiC/SiO<sub>2</sub>-selectivity of the dry etching process for trench formation in SiC. Based on previous results, SiC trench etching can be limited by the low selectivity between the SiO<sub>2</sub> hard mask and SiC. Therefore, the main focus was to increase the selectivity towards the oxide hard mask in order to increase the potential trench depth in SiC without compromising the trench geometry.

### **Dry Etching**

Dry etching processes are based on material removal by plasma-activated, i.e. ionized gas, generated at low pressures. This so-called gas discharge can occur in a variety of ways and, together with the utilized dry etching process, is characteristic for the resulting etch profile, usually being anisotropic. The material can be removed physically by bombardment with accelerated ions or chemically by reaction with reactive species from the plasma. Usually, the material removal is based on a combination of both physical and chemical components. This allows the advantages of both etching mechanisms to be combined, enabling dry etching processes with relatively high anisotropy due to the physical and relatively high selectivity due to the chemical component [4, 5]. The selectivity S describes the ratio between the etching rates of the to be etched material  $r_1$  and the etching mask  $r_2$ . The etching rate r is defined as the material removal  $\Delta z$  per etching time  $\Delta t$  [5].

$$r = \frac{\Delta z}{\Delta t}.\tag{1}$$

$$S = \frac{r_1}{r_2}. (2)$$

In order to achieve high structural fidelity, it is of utmost importance to select a suitable etching mask that is removed more slowly than the material to be structured, i.e. that  $r_2$  is as small as possible compared to  $r_1$ . In general, the higher the selectivity, the deeper the substrate material can be etched without jeopardizing the structural conformity. With that, finding a suitable combination of etching process, material to be etched and etching mask is key for selective dry etching processes.

One major parameter for dry etching is the etching gas composition. The decisive factor in the choice of etching gas is that gaseous, volatile reaction products are formed under real process

conditions, i.e. at moderate temperatures and pressures. Thus, their boiling point should ideally be at temperatures below 100 °C at a pressure above 1 Pa. Highly selective etching processes can result from suitable matching of the process gases to the materials to be etched. For example, photoresists, i.e. organic polymers with the main constituents C, H and N, can react extremely easily with Oxygen to form e.g. CO and CO<sub>2</sub> already at low temperatures. Etching of SiO<sub>2</sub> is usually based on a chemical reaction with F to form SiF<sub>4</sub>. Also in the etching of Si and SiC, F-based etching gases have prevailed over e.g. Cl- or Br-containing etching gases, since F forms gaseous compounds with Si and C at much lower temperatures (approx. -100 °C), which could also be a reason for the higher achievable etching rate in F-based etching processes. Usually, Ar or O<sub>2</sub> are added to F-based etch gases to increase the number of reactive etch species or to facilitate the removal of carbon. A special feature of SiC etching is the use of S- and Si-containing gases (SF<sub>6</sub> or SiF<sub>4</sub>) [3-6].

In this context, it is worth mentioning that for dry etching of SiC, SiO<sub>2</sub> is usually used as the masking material in front-end-of-line processing. A photoresist mask is not suitable here since the removal of C in SiC requires etching gases which would also attack the photoresist and thus reduce the selectivity. Significantly higher selectivities could be achieved with metal-containing masks such as Al or Ni [3]. However, since metal contamination before the first metallization process usually must be avoided in semiconductor manufacturing, this option was not investigated here.

Besides the utilized etching gases, the predominant etching mechanism heavily depends on the type of reactor used. Common dry etching systems feature the Inductively Coupled Plasma (ICP) reactor type, where the plasma is activated by an electric field oscillating in all spatial directions, allowing a high-density plasma at low pressures. The substrate is positioned on the cathode onto which positive ions of the plasma are accelerated by applying radiofrequency (RF) power. With increasing RF power, the energy of the accelerated ions increases, resulting in a predominantly physical etching characteristic with relatively high material removal of the substrate as well as the mask, consequently limiting the selectivity of the process. Hence, a high etch rate, a low selectivity and an anisotropic etch profile are typical for physical etching. The increase in RF power, however, is limited by the thermal budget, i.e. the allowable heating of the etched materials over a given period of time. For example, too long ion bombardment with too high energies can lead to progressive deformation, cross-linking or decomposition of the photoresist mask during SiO<sub>2</sub> etching, used as a hard mask for SiC trench etching. To avoid a negative influence on the pattern transfer fidelity for the following SiC dry etching, the photoresist temperature during the SiO<sub>2</sub> hard mask etching process should not exceed approx. 100 °C. The ICP power determines the plasma density, which primarily affects the etching rate, leading to increasing etch rates with increasing ICP power. At moderate RF power, the chemical etch fraction of the process can be controlled by the ICP power, which in principle can have a positive effect on selectivity, but also favors an isotropic etch profile. If, on the other hand, the RF power is too high at the same time, the opposite effect can be achieved [4-6].

In summary, the main advantage of an ICP dry etch reactor is that the generation of reactive species can be controlled independently of the acceleration energy of the ions onto the substrate. While the physical etching part can be controlled by the RF power, the chemical part is significantly influenced by the applied ICP power. In chemical-physical dry etching both ablation mechanisms are combined in one process. Furthermore, the chemical etching reaction can be triggered or supported by the kinetic energy of the impacting ions. The material removal can be initiated by ion bombardment by breaking the bonds of the surface atoms, so that chemical reactions of plasma-activated gases can take place more effectively. The additional energy supply can also make it easier to overcome the energy barrier for a chemical reaction on the surface, thus promoting it. By combining chemical and physical etching attack in one process, the advantages of both etching mechanisms can be obtained, resulting in anisotropic, selective etching processes and allowing deep, structurally conformal etching profiles to be realized. As a result of the superior etching characteristics in terms of etch rate, selectivity and anisotropy, corresponding etching processes form the basis for structure generation in microelectronics and thus are applied for SiC etching for semiconductor devices [3-7].

#### **Fabrication**

In this work, the NE-550EXa ICP dry etching system from Ulvac was used for SiC trench etching on commercial 4H-SiC substrates with standard specifications. Prior to trench etching, a  $1.0\pm0.1~\mu m$  PECVD oxide hard mask was deposited and etched, using a suitable oxide dry etching process on the same ICP system and a resist mask which was patterned by UV step-and-repeat photolithography. After oxide hard mask etching via dry etching, the resist was removed, using a combination of plasma ashing in a barrel reactor and subsequent wet etching in Piranha acid. Eventually, SiC trench etching was performed and the results were investigated before removal of the oxide hard mask.

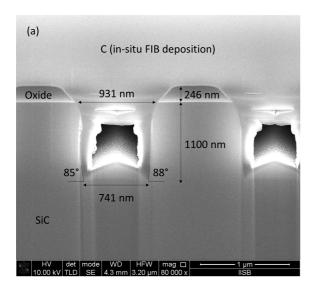

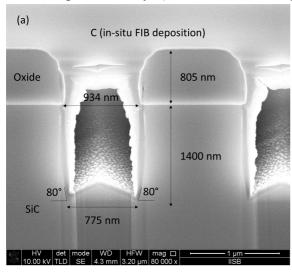

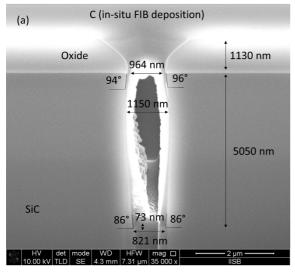

Focus of the process development presented in this work was to increase the SiC/SiO<sub>2</sub>-selectivity of the standard SiC trench etch process at IISB, while also considering that the SiC trench profile must not be compromised. Table 1 contains all process variations with its results. For each recipe, the etched SiC trench profile was analyzed by cross-section preparation via FIB (Focused Ion Beam) and SEM imaging. Having a SiC/SiO<sub>2</sub>-selectivity of approx. 1.6 (see Table 1, recipe V1), the potential SiC trench depth is limited to approx. 1  $\mu$ m under otherwise identical conditions like oxide hard mask type or thickness. The cross-sectional SEM (Scanning Electron Microscopy) image in Fig. 1 (a) shows that, when using the V1 standard process and a  $1.0 \pm 0.1~\mu$ m PECVD oxide hard mask, upper trench corner rounding already occurs at 1.1  $\mu$ m trench depth, jeopardizing the steep and linear SiC trench profile necessary for device functionality and performance [2, 3, 7].

**Table 1.** Overview of process parameters of each dry etch recipe used for SiC trench etching with their results in terms of SiC/SiO<sub>2</sub>-selectivity, micro-trench height and trench profile sidewall angles. The standard SiC trench etch process V1 acted as reference and starting point. The modified parameters were the ICP power, the RF power as well as the SiF<sub>4</sub> gas flow, as these parameters were identified as most crucial for the SiC/SiO<sub>2</sub>-selectivity of the SiC trench process. As the values of the individual process parameters are confidential, each parameter is specified in high ( $\uparrow$ ), medium ( $\rightarrow$ ) or low ( $\downarrow$ ), representing one certain value within the feasible parameter range of the tool. It is to be noted that a total of six different parameter values were examined for the SiF<sub>4</sub> flux, resulting in a multiple number of arrows that correlate with the magnitude of each parameter value. Other key parameters as the chamber pressure, the SF<sub>6</sub> as well as the O<sub>2</sub> gas flow were not modified.

| - ·    | Process parameter |               |                                  | Selectivity              | Micro-trench | Trench profile |

|--------|-------------------|---------------|----------------------------------|--------------------------|--------------|----------------|

| Recipe | ICP [W]           | RF [W]        | SiF <sub>4</sub> [sccm]          | SiC/SiO <sub>2</sub> [-] | [nm]         | [°]            |

| V1     | $\rightarrow$     | $\rightarrow$ | $\uparrow \uparrow$              | 1.6                      | 0            | 85 - 88        |

| V1.1   | <b>↑</b>          | $\rightarrow$ | $\uparrow \uparrow$              | 1.3                      | 0            | 89             |

| V1.2   | <b>↑</b>          | $\downarrow$  | $\uparrow \uparrow$              | 1.5                      | 53           | 87             |

| V2.1   | <b>↑</b>          | $\downarrow$  | $\rightarrow$                    | 2.6                      | 0            | 82 - 84        |

| V2.2   | $\rightarrow$     | $\rightarrow$ | <b>↑</b>                         | 1.8                      | 0            | 82 - 83        |

| V2.3   | $\rightarrow$     | $\rightarrow$ | $\rightarrow$                    | 2.2                      | 0            | 87             |

| V2.4   | $\rightarrow$     | $\rightarrow$ | <b>\</b>                         | 3.0                      | 0            | 81 - 84        |

| V2.5   | $\rightarrow$     | $\rightarrow$ | $\downarrow\downarrow$           | 4.0                      | 0            | 81 - 82        |

| V2.6   | $\rightarrow$     | $\rightarrow$ | $\downarrow\downarrow\downarrow$ | 4.0                      | 0            | 84             |

| V3.1   | <b>↑</b>          | <b>↑</b>      | $\downarrow\downarrow\downarrow$ | 5.1                      | 0            | 84 - 85        |

| V3.2   | $\downarrow$      | <b>↑</b>      | $\rightarrow$                    | 2.7                      | 0            | 85             |

| V3.3   | <b>↑</b>          | $\downarrow$  | $\rightarrow$                    | 2.4                      | 0            | 82             |

| V3.4   | <b>↑</b>          | $\downarrow$  | $\downarrow\downarrow\downarrow$ | 7.9                      | 36           | 80             |

| V3.5   | $\downarrow$      | $\downarrow$  | $\downarrow\downarrow\downarrow$ | 3.8                      | 64           | 85 - 86        |

| V3.6   | $\downarrow$      | <b>\</b>      | $\rightarrow$                    | 3.0                      | 0            | 81 - 86        |

| V3.7   | $\downarrow$      | <b>↑</b>      | $\downarrow\downarrow\downarrow$ | 3.1                      | 0            | 82 - 87        |

| V3.8   | $\uparrow$        | $\uparrow$    | $\rightarrow$                    | 2.0                      | 0            | 78 - 82        |

| V3.9   | $\uparrow$        | $\uparrow$    | $\overline{}$                    | 4.8                      | 0            | 78 - 81        |

The design of experiments was divided into three phases. In the first phase, the main influence of ICP and RF power on the SiC/SiO<sub>2</sub>-selectivity were investigated. During the second phase, focus was put mainly on the variation of the SiF<sub>4</sub> gas flow. Within the third phase, combinations of ICP and RF power as well as SiF<sub>4</sub> flux were tested, based on the outcome of the previous experiments. All following references to recipes in the upcoming paragraphs refer to Table 1.

By increasing the ICP power, the selectivity of the process is reduced (see recipe V1.1). Therefore, a higher activation rate of the plasma, which simultaneously leads to an increased number of reactive etch species, results in a significant increase in etching rate of the oxide compared to SiC with otherwise equal process parameters, indicating the oxide being more prone to chemical etching. When simultaneously reducing the RF power, the selectivity increases (see recipe V1.2), indicating that the oxide is less susceptible to physical material removal than SiC. Another observation that can be made is that with reduced RF power micro-trenching occurs. One factor that has significant influence on the etch profile, especially in dry etching of deep trenches in SiC, is the formation of differential charges in the etched structures. As a result of the directional acceleration, positively charged etch species predominantly strike the bottom of the structure. In contrast, electrons, which can follow the oscillating electric field more easily and are thus more direction independent, hit the sidewalls of the etched structure. Therefore, the sidewalls are negatively charged compared to the bottom, leading to a potential difference within the etched structure and ultimately resulting in a deflection of the flight path of positive ions, which thus experience a horizontal motion component towards the sidewall. This results in a locally higher etch rate where the bottom is etched deeper near the sidewalls. The lower the RF power, the lower the acceleration energy, leading to a stronger horizontal deflection of an ion when reaching the trench bottom and hence, a more pronounced micro-trenching. With that, the aspect ratio is an important factor for trench shape and micro-trenching [6].

Next, when reducing the SiF<sub>4</sub> gas flow while maintaining an increased ICP and decreased RF power, SiC/SiO<sub>2</sub>-selectivity can be increased from 1.5 to 2.6 (see recipe 2.1 in comparison to recipe 1.2). However, the trench sidewall angle is significantly reduced, counteracting the formation of a trench with vertical sidewalls. It is to be noted that, when two values are presented for the trench profile in Table 1, the geometry of the trench is not symmetrical, showing different angles on the left and the right sidewall. Nevertheless, in terms of increasing selectivity, this observation served as a starting point for the investigation of several variations of SiF<sub>4</sub> gas flow, with all other process parameters remaining as in the standard recipe V1. Finally, a clear correlation between decreasing SiF<sub>4</sub> gas flow and increasing SiC/SiO<sub>2</sub>-selectivity could be observed (see recipes V2.2 – V2.6). Apart from recipe V2.3, all variations within the second phase led to comparably flat trench sidewall angles.

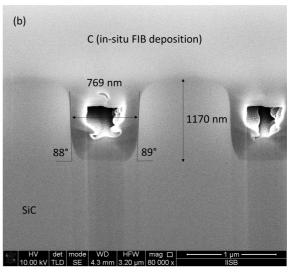

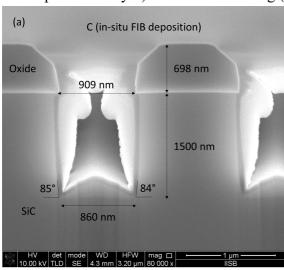

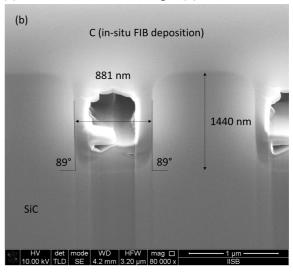

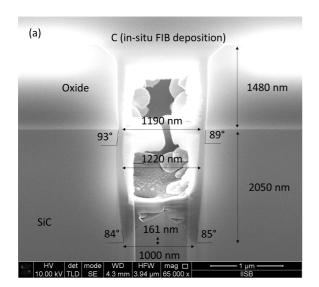

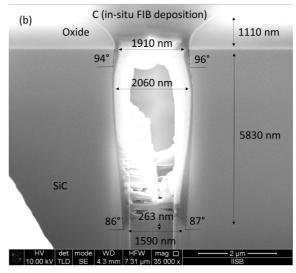

Last, based on the investigations and results of the first and second phase, variations of SiF<sub>4</sub> gas flow were combined with different ICP and RF power parameters to determine the process window. With increasing ICP power and decreasing SiF<sub>4</sub> gas flow, especially in combination with decreasing RF power, the SiC/SiO<sub>2</sub>-selectivity increases significantly (see recipes V3.1 and V3.4 as well as Fig. 2 (a) and 3 (a)). This correlation can be explained by the increase of reactive species in the plasma due to the increased ICP power as well as the reduced acceleration energy of charged etch species to the substrate due to the reduced RF power, reaffirming a pronounced material dependency of the physical etching due to ion bombardment. Within the third phase, a distinct increase in SiC/SiO<sub>2</sub>-selectivity was obtained by every tested parameter set. The data indicates that the most decisive parameter change is the reduction of the SiF4 gas flow, which can be explained by a lower O<sub>2</sub> consumption and SiO<sub>2</sub> formation when the SiF<sub>4</sub> gas flow is also reduced. Eventually, with a SiC/SiO<sub>2</sub>-selectivity of 7.9, recipe V3.4 with high ICP power, low RF power and very low SiF<sub>4</sub> gas flow proves to be the best combination of the given parameters with regards to high selectivity, though compromising the steepness of the trench profile. As it can be seen in Fig. 3 (a), the trench sidewalls are curved. Due to the deflection of ions towards the sidewalls, differential charging can cause this so-called bowing. The lateral etching component creates a curved profile where the distance between the sidewalls in the trench is greater than its opening width at the surface. This effect can be enhanced by the reflection of ions from sloped mask edges. Since lateral deflection is less pronounced with increasing acceleration, this effect can be reduced by increasing the RF power [6].

**Fig. 1**. SEM cross-section image of trench profile V1 (prepared via FIB and covered by insitu deposited C layer) after trench etching (a) and after trench reshape (b).

**Fig. 2.** SEM cross-section image of trench profile V3.1 (prepared via FIB and covered by in-situ deposited C layer) after trench etching (a) and after trench reshape (b).

**Fig. 3.** SEM cross-section image of trench profile V3.4 (prepared via FIB and covered by in-situ deposited C layer) after trench etching (a) and after trench reshape (b).

Another observation is the occurrence of micro-trenching with low RF power and very low SiF4 gas flow, especially in combination with low ICP power (see recipes V3.4 and V3.5). With reduced ion acceleration energy, fewer reactive species potentially enhance the effect of micro-trenching due to a bigger fraction of total reactive species being deflected. In addition to the extent of micro-trenching, the trench corner sharpness in general is crucial for SiC TrenchMOS performance and reliability, where the trench bottom should be rounded to reduce electric field enhancement in the gate oxide at sharp corners during blocking operation. In addition, vertical sidewalls and their roughness are of utmost importance to reduce interface states between the gate oxide and the SiC sidewall and to obtain a high electron mobility along the inversion channel formed on the trench sidewalls [3, 5, 7]. For that reason, a high temperature annealing process at 1400 °C for so-called trench reshape was performed, rounding the trench corners and smoothening the sidewalls, as it can be seen in Fig. 1 (b), 2 (b) and 3 (b). Moreover, this annealing step can compensate for different trench profiles. After trench reshape, the profiles formed with recipes V1, V3.1 and V3.4 feature comparable characteristics in terms of corner rounding, sidewall angles and bowing.

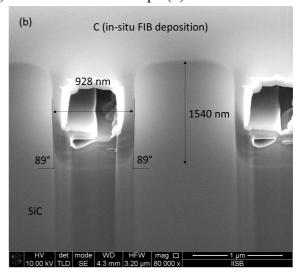

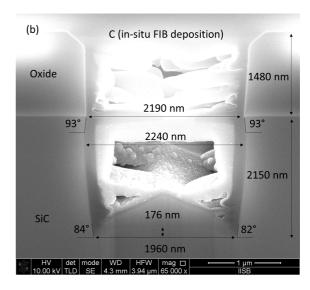

To investigate and exploit the potential of the SiC trench etch recipe V3.4 with the highest SiC/SiO<sub>2</sub>-selectivity, trenches with targeted depths of 2 and 5  $\mu$ m were etched in SiC, utilizing oxide masks with thicknesses of approx. 1.8  $\mu$ m. The results are presented in Fig. 4 and 5.

Fig. 4. SEM cross-section image of trench profile V3.4 (prepared via FIB and covered by in-situ deposited C layer) with a targeted trench depth of 2  $\mu$ m and trench width of 1  $\mu$ m (a) and 2  $\mu$ m (b).

**Fig. 5.** SEM cross-section image of trench profile V3.4 (prepared via FIB and covered by in-situ deposited C layer) with a targeted trench depth of 2  $\mu$ m and trench width of 1  $\mu$ m (a) and 2  $\mu$ m (b).

In the cross-sectional SEM images of the etch trial with a targeted SiC trench depth of 2 µm, presented in Fig. 4, a good agreement is observed between the width at the trench bottom and the feature size given by the mask design, which was 1 µm in Fig. 4 (a) and 2 µm in Fig. 4 (b), generally showing a high structural fidelity of the process, yet with a certain extent of bowing. However, considering the results, a trench reshape could counteract the curved, unsymmetrical sidewalls and result in a trench profile with nearly vertical sidewalls, as presented in Fig. 1 (b), 2 (b) and 3 (b). In case of the targeted 5 µm trench depth, structural fidelity suffers, significantly affected by the pronounced bowing, as shown in Fig. 5 (a) for 1 µm and Fig. 5 (b) for 2 µm trench width. However, the extent of bowing seems to not be influenced by the width. Furthermore, the inhomogeneity of the trench depth increases with increasing width and especially with increasing depth, as it can be seen in Fig. 5 (a) and (b). Also, a difference in micro-trenching, which increases with increasing trench width, can be observed. Main reason for this is that as the etch depth increases, the angle of incidence of directional ions must become steeper to reach the bottom of the etched structure. In turn, this reduces the vertical etch rate. Hence, the smaller the opening width of the trench, the more limited the suitable angle of incidence and thus the number of incident ions, which further limits the etch depth. In addition, the flux of ions is affected by the charge difference within the etched structure, so that fewer ions arrive at the bottom for small structure diameters. All these mechanisms lead to a decrease in the net ion flux at the bottom of the etched structure, causing the etch rate to decrease as the aspect ratio increases [5, 6]. Nevertheless, the impact of SiF<sub>4</sub> gas flow on sidewall roughness also must be considered. At given time, the sidewall roughness was determined by optical inspection via SEM of the trench sidewalls. Qualitative measurement techniques are currently evaluated at IISB.

## **Summary**

In this work, the SiC/SiO<sub>2</sub>-selectivity of the standard dry etch process for trench formation in SiC was improved up to 7.9, increasing the selectivity of the standard reference process by nearly 5 times. With that, trenches of 2  $\mu$ m depth with an adequate structural fidelity could be fabricated, whereby the average etch rate decreases with decreasing width. Future work will focus on improving the structural fidelity for trench depths between 2 and 5  $\mu$ m, extending the potential trench depth in SiC up to 10  $\mu$ m, establishing qualitative characterization methods for surface roughness measurements on trench sidewalls and investigating different trench reshape parameters for sidewall smoothening. The results will be used for the development of SiC super-junction devices in the future.

#### References

- [1] J. Millan, P. Godignon, X. Perpina, A. Perez-Tomas, J. Rebollo, A Survey of Wide Bandgap Power Semiconductor Devices, IEEE Trans. Power Electron. 29 (2014) 2155.

- [2] F. Udrea, G. Deboy, T. Fujihira, Superjunction Power Devices, History, Development, and Future Prospects, IEEE Trans. Electron Devices 64 (2017) 713.

- [3] T. Kimoto, J.A. Cooper, Fundamentals of Silicon Carbide Technology, first ed., Wiley, Singapore, 2014.

- [4] S.M. Sze, M.K. Lee, Semiconductor Devices, Physics and Technology, third ed., Wiley, New York, 2012.

- [5] D. Widmann, H. Mader, H. Friedrich, Technologie hochintegrierter Schaltungen, second ed. Springer, Berlin, 1996.

- [6] N. Posseme, Plasma Etching Processes for CMOS Device Realization, London, Kidlington Oxford: ISTE Press Ltd; Elsevier Ltd, 2017.

- [7] B.J. Baliga, Silicon Carbide Power Devices, first ed., World Scientific Publishing Co, Singapore, 2005.