# High-Quality SiC Crystal Growth by Temperature Gradient Control at Initial Growth Stage

Submitted: 2023-09-30

Accepted: 2024-04-15

Online: 2024-08-27

Chae Young Lee<sup>1,a</sup>, Seung Jun Lee<sup>1,b</sup>, Jong Hwi Park<sup>1,c</sup>, Jung Woo Choi<sup>1,d</sup>, Jung Gyu Kim<sup>1,e</sup>, Kap Ryeol Ku<sup>1,f</sup>, Jun Hyuck Na<sup>2,g</sup>, Min Gyu Kang<sup>2,h</sup>, and Won Jae Lee<sup>2,i\*</sup>

<sup>1</sup>Senic, 17-15, 4sandan 7-ro, Jiksan-eup, Seobuk-gu, Cheonan-si, Chungcheongnam-do, Korea <sup>2</sup>Department of Advanced Materials Engineering, Dong-Eui University, 176, Eomgwang-ro, Busanjin-gu, Busan, Korea

acylee@senic.co.kr, bsjlee@senic.co.kr, cjhpark@senic.co.kr, jwchoid@senic.co.kr, ejgkim@senic.co.kr, fkrku@senic.co.kr, gmjna21x@naver.com, hkminq980@gmail.com, ileewj@deu.ac.kr

Keywords: 4H-SiC, C/Si ratio, Initial growth stage, High-quality SiC

**Abstract.** A modified process condition has been proposed for the growth of high-quality 6-inch 4H-SiC single crystal. Temperature gradient ( $dT[^{\circ}C] = T_{bottom}-T_{upper}$ ) was controlled by changing coil position in order to investigate the effect of the temperature gradient on the SiC crystal quality. SiC ingot surface and etch pit density (EPD) of etched SiC wafer were investigated according to different dT conditions at the initial stage of SiC crystal growth. The surface of SiC crystal ingots grown with different dT for 10h were observed by OM and etched SiC wafers were prepared from SiC crystal ingots after main growth step for 100h. Different dT conditions in the initial growth stage resulted in dramatically different surface images and the crystal quality evaluated by EPD.

### Introduction

Silicon carbide (SiC) is a wide-bandgap semiconductor material and has been the subject for intense research as a promising material suitable for various power devices designed specifically for highvoltage, high-temperature applications. A physical vapor transport (PVT) process, and recent marked development of the PVT growth technology has contributed not only to the realization of SiC single crystals with much improved crystal quality but also to astonishing demonstration of 150 mm SiC single crystals [1]. However, the quality of the SiC wafer needs further improvement implying the reduction of defect density. Various kinds of defects have been known to exist in the grown SiC crystals [2]. This status is basically due to the lack of full knowledge of defect formation mechanisms in SiC crystal growth. Therefore, further insight into the PVT growth process is necessary to increase the crystal diameter and length as well as the crystallization rate of SiC boules in order to push the commercialization of SiC based devices [3]. To achieve high quality SiC crystal growth, we focus on the temperature gradient of initial stage. Since Si-rich gas (Si, Si<sub>2</sub>C) among source gases could provide damage on seed surface in the initial growth stage, various dT in the initial stage of growth were set and then changed into different dT condition having constant C/Si ratio during the main growth process. Various crystal properties of SiC crystals grown with modified process condition have been systematically investigated in this study.

## **Experiments**

6-inch 4H-SiC boules growth was carried out on 4° off-axis C-face substrates by the PVT method. A modified process condition of initial growth stage has been proposed. The growth temperature was set at 2300-2400°C under pressure 5-20 torr in nitrogen and argon atmosphere. The 6-inch 4H-SiC wafers were fabricated by standard semiconductor machining process. SiC wafers prepared according to different dT conditions at the initial stage of SiC crystal growth were etched for 14min at 600°C for defect evaluation. Optical microscope (OM) was used to measure the surface etch pit density

(EPD). High resolution X-ray Diffraction (XRD) system was used to measure full width at half maximum (FWHM) values and the mapping image of 6-inch SiC crystal wafer.

#### **Result and Discussion**

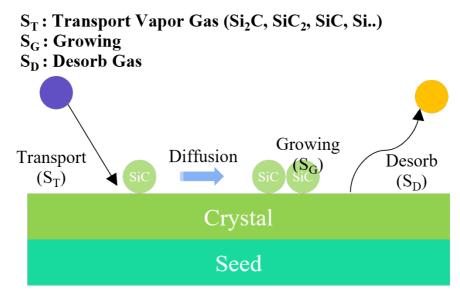

In order to generally achieve high quality SiC single crystal, to use high purity SiC powder source, to carefully control C/Si ratio and to maintain constant growth temperature/pressure are required. Furthermore, it is also very important to minimize the seed loss and to suppress defect formation on seed surface in the initial stage of growth for growing high quality SiC crystal. Fig. 1 exhibited schematic diagram of the growth mechanism for SiC crystal growth in this study. As shown in Fig. 1, vapor  $gas(S_T)$  transport to a seed surface and then diffuse on the seed surface for growing crystal. Some part of  $gas(S_T)$  not to participate in the growth desorbs from the crystal surface. Since the growth proceeds when  $(S_G)$  amount exceeds  $gas(S_D)$  amount on seed surface, the growth temperature range was investigated to find suitable ratio of  $gas(S_G)/gas(S_D)$  by changing RF heating coil during the growth process.

Fig. 1. Schematic diagram of the growth mechanism for SiC crystal growth in this study.

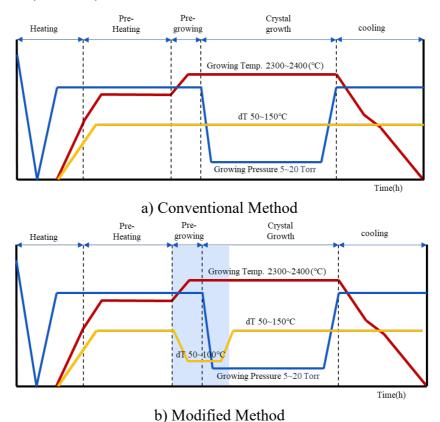

Fig. 2 exhibited schematic diagram of the process condition for SiC crystal growth in this study. The growth temperature and pressure for typical growth process were  $2300\sim2400^{\circ}\text{C}$  and  $5\sim20$  Torr, respectively. Temperature gradient during the growth process was maintained to be  $dT=50\sim150^{\circ}\text{C}$  ((a) Conventional Method). Sometimes, inhomogeneous supply of source gases (Si<sub>2</sub>C, SiC<sub>2</sub>, Si) could generate stacking fault, polytype inclusion indicating a degradation of the crystal quality. Therefore, smaller  $dT(=50\sim100^{\circ}\text{C})$  was carefully controlled at the initial stage of growth by changing RF coil position, and then moved to  $dT=50\sim150^{\circ}\text{C}$  for main bulk growth process ((b)Modified Method). In order to control  $dT(dT[^{\circ}\text{C}] = T_{bottom} - T_{upper}$ ), the upper temperature was varied from 2270°C, 2250°C, 2200°C, to 2150°C with fixed bottom temperature of 2300°C. Optical microscope (OM) images of SiC ingot surface prepared according to different  $dT[^{\circ}\text{C}]$  conditions were shown in Table 1.

The defect density of SiC ingot surface at initial stage dT=50°C after 10h growth was observed to be definitely lower than those at dT=30°C and dT=150°C. In case of dT=30°C, too small dT in the initial stage of growth could induce seed loss resulting in defect formation. And too high dT in the initial stage of growth could generate unstable supersaturation resulting in the polytype inclusion, defect formation due to high vacancy concentration. However, if dT in the initial stage of growth could be optimized, high quality crystal growth could be enabled by minimizing initial defect formation. Since the defect density of SiC ingot surfaces after 100h growth was observed to be similar result like defect density after 10h growth, an attempt to reduce defect formation in the initial stage of growth was definitely important step to obtain high quality SiC crystal.

Wafers prepared from crystal ingots grown for 100h were etched to investigate defect density of SiC crystal, as shown in Table 2. While EPD values of SiC crystals grown with initial stage dT=30°C and dT=150°C were measured to be 35,880/cm<sup>2</sup> and 25,660/cm<sup>2</sup>, respectively, SiC crystal grown with optimized condition (dT=50°C) exhibited much lower value, EPD value of 8,560/cm<sup>2</sup>.

Fig. 2. Schematic diagram of the process condition for SiC crystal growth in this study.

**Table 1.** OM images of SiC ingot surface prepared according to different dT[°C] conditions.

| <b>Table 1.</b> OM images of SiC ingot surface prepared according to different d1[°C] conditions. |                                        |      |      |      |      |  |

|---------------------------------------------------------------------------------------------------|----------------------------------------|------|------|------|------|--|

| Initial                                                                                           | Stage dT[°C]                           | 30   | 50   | 100  | 150  |  |

| Upper Temperature[°C]                                                                             |                                        | 2270 | 2250 | 2200 | 2150 |  |

| Bottom '                                                                                          | Temperature[°C]                        | 2300 | 2300 | 2300 | 2300 |  |

| OM                                                                                                | Ingot surface<br>[As grown for<br>10h] |      |      |      |      |  |

| Image                                                                                             | Ingot surface [As grown for 100h]      |      |      |      |      |  |

| _                                      |                                        |        | _     | , ,    |        |

|----------------------------------------|----------------------------------------|--------|-------|--------|--------|

| Initial Stage dT[°C]                   |                                        | 30     | 50    | 100    | 150    |

| OM<br>Image                            | Etched wafer<br>[As grown for<br>100h] |        |       |        |        |

| Etch Pit Density [ea/cm <sup>2</sup> ] |                                        | 35,880 | 8,560 | 18,620 | 25,660 |

**Table 2.** This table contained OM images and etch pit density on etched SiC wafer prepared according to different dT [°C] conditions at the initial stage of SiC crystal growth.

Full width at half maximum (FWHM) values and mapping image of SiC crystals grown with varying initial stage dT[°C] were presented in Table 3. SiC crystal grown with optimized dT=50°C had average FWHM value of 18.6 arcsec, which was lower than that of crystals with different dT conditions.

**Table 3.** This table contained full width at half maximum (FWHM) values and mapping image prepared according to different dT[°C] conditions at the initial stage of SiC crystal growth.

| Initial dT[°C]         | 30                                         | 50 100                                          |      | 150                                        |  |

|------------------------|--------------------------------------------|-------------------------------------------------|------|--------------------------------------------|--|

| XRD<br>Mapping<br>Data | (a)  10  10  10  10  10  10  10  10  10  1 | (b)  (c)  (d)  (v)  (d)  (v)  (d)  (v)  (d)  (d | CC)  | (d)  10  10  10  10  10  10  10  10  10  1 |  |

| Max.<br>[arcsec]       | 252.9                                      | 34.4                                            | 42.4 | 101.8                                      |  |

| Min. [arcsec]          | 60.0                                       | 16.8                                            | 20.2 | 72.1                                       |  |

| Avg. [arcsec]          | 122.4                                      | 18.6                                            | 29.8 | 89.4                                       |  |

## **Summary**

Temperature gradient ( $dT[^{\circ}C] = T_{bottom}-T_{upper}$ ) was controlled by changing coil position in order to investigate the effect of the temperature in the initial stage of growth on SiC crystal quality. The defect density of SiC ingot surface grown with the initial stage  $dT=50^{\circ}C$  after 10h growth was observed to be definitely lower than those at  $dT=30^{\circ}C$  and  $dT=150^{\circ}C$ . SiC crystal grown with optimized  $dT=50^{\circ}C$  had average FWHM value of 18.6 arcsec, which was much lower than that of SiC crystal with other growth conditions.

# Acknowledgements

This work was supported by Technology Innovation Program (RS-2022-00154720) and the Technology Innovation Program (Project Number: 20022843, Project Name: Development of automated inspection equipment capable of high speed high precision analysis of large diameter SiC bare and Epi wafers) funded by the Ministry of Trade, Industry(MOTIE, Korea), 2023 and by the Energy and Korea Institute for Advancement of Technology(KIAT) grant funded by the Korea Government(MOTIE, P0012451, The Competency Development Program for Industry Specialist).

## References

- [1] Tatsuo Fujimoto, Noboru Ohtani: ECS J. Solid State Sci. Technol Vol. 2 (8) 2013, p. N3018

- [2] L N Zhu, Heqing Li, B Q Hu, X Wu and X L Chen: J. Phys. Condens. Matter Vol. 17 (2005), p. L85

- [3] D. Hofmann, E. Schmitt, M. Bickermann: Mater. Sci. Eng. B61-62 (1999), p. 48