# Investigation on Bipolar Degradation Caused by Micropipe in 3.3 kV SiC-MOSFET

Submitted: 2024-09-20

Revised: 2025-08-05

Online: 2025-09-05

Accepted: 2025-08-05

Hiroki Niwa<sup>1,a\*</sup>, Takanori Tanaka<sup>2,b</sup>, Kazuya Ishibashi<sup>2,c</sup>, Hiroyuki Amishiro<sup>1,d</sup>, Akifumi Imai<sup>1,e</sup>, Yasuhiro Kagawa<sup>2, f</sup>, Katsutoshi Sugawara<sup>1,g</sup>, and Tatsuro Watahiki<sup>1, h</sup>

<sup>1</sup>Advanced Technology R&D Center, Mitsubishi Electric Corp., Tsukaguchi-Honmachi 8-1-1, Amagasaki, Hyogo, 661-8661, JAPAN

<sup>2</sup>Power Device Works, Mitsubishi Electric Corp., Imajuku-Higashi 1-1-1, Nishi-ku, Fukuoka, 819-0192, JAPAN

<sup>a</sup>Niwa.Hiroki@dp.MitsubishiElectric.co.jp, <sup>b</sup>Tanaka.Takanori@cb.MitsubishiElectric.co.jp, <sup>c</sup>Ishibashi.Kazuya@ak.MitsubishiElectric.co.jp, <sup>d</sup>Amishiro.Hiroyuki@cb.MitsubishiElectric.co.jp, <sup>e</sup>Imai.Akifumi@ys.MitsubishiElectric.co.jp, <sup>f</sup>Kagawa.Yasuhiro@cj.MitsubishiElectric.co.jp, <sup>g</sup>Sugawara.Katsutoshi@ea.MitsubishiElectric.co.jp, <sup>h</sup>Watahiki.Tatsuro@dx.MitsubishiElectric.co.jp

**Keywords:** Body diode, Bipolar degradation, Leakage current degradation, Micropipe, BPD, Failure analysis, PL imaging

**Abstract.** In this study, high current stress was applied to the body diode of SiC-MOSFETs, and chips exhibiting leakage current degradation due to the bipolar degradation phenomenon were analyzed to identify the crystal defects responsible for the abnormal leakage current. Failure analysis and defect inspection during the device fabrication process revealed that abnormal leakage occurred at the periphery of extended stacking faults originating from or near the micropipe itself. As these extended stacking faults also increase the forward voltage drop of MOSFETs, these results suggest that micropipe are critical defects in SiC-MOSFETs inducing both forward voltage and leakage current degradation in the bipolar degradation phenomenon.

## Introduction

For decades, the bipolar degradation phenomenon has been a key issue faced by SiC-MOSFETs [1–5]. This phenomenon involves two types of degradation: an increase in the forward voltage drop ( $V_{\rm DSon}$  of the MOSFET and  $V_{\rm SDon}$  of body diode (BD)) and an increase in the leakage current of MOSFETs in blocking mode ( $I_{\rm DSX}$ ). Such degradation can cause MOSFET characteristics to deviate from datasheet values during operation, raising reliability concerns. The impact of bipolar degradation is particularly pronounced in high-power applications, where chips have large active areas and/or thick epitaxial layers to handle high currents and voltages. Therefore, careful consideration of this phenomenon is crucial for devices used in these applications.

Screening MOSFETs degraded by high current stress to the BD (BD stress) is the most direct and reliable method for managing this degradation. Consequently, this approach has been applied for many years in the screening process for some of high-voltage SiC-MOSFETs in mass production [6, 7]. However, because this method is relatively time-consuming, various alternative methods have been proposed to control this degradation mode [8–13]. Despite these efforts, fundamental studies on the bipolar degradation phenomenon itself are becoming increasingly important for addressing this issue more competitively. Although numerous studies on  $V_{\rm DSon}$  degradation have been conducted over the years, research on  $I_{\rm DSX}$  degradation remains limited [3–5, 7], and the defects responsible for this degradation are still unclear. Therefore, to fully understand the bipolar degradation phenomenon in SiC, studies focusing on  $I_{\rm DSX}$  degradation are essential.

In this study, high current stress was applied to the BD of many 3.3 kV SiC-MOSFETs, and *I*<sub>DSX</sub> degraded chips were identified. These degraded MOSFETs were then analyzed in detail, and the crystal defects responsible for this degradation phenomenon were identified.

# **Experimental**

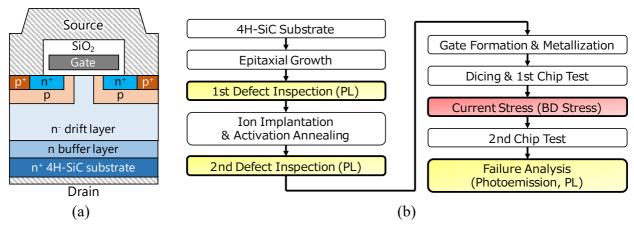

Figure 1(a) shows the planar-type 3.3 kV SiC-MOSFET fabricated on an n<sup>+</sup>-type 4H-SiC substrate in this study. The size of the MOSFET was approximately  $9\times8$  mm<sup>2</sup>. During device fabrication, defect inspection using photoluminescence (PL) was performed after epitaxial growth and activation annealing. Figure 1(b) illustrates the experimental flow of this study. After the device fabrication process, an initial chip test was conducted to select "good" chips for the BD experiment. At this stage, these "good" chips exhibited no abnormal *I-V* characteristics or signs of degradation. Subsequently, a high current stress of 300 A/cm<sup>2</sup> at ~175°C was applied to the BD of each chip. In the following chip test, chips with increased leakage current compared to the initial test were characterized as " $I_{DSX}$  degraded chips", while those showing only an increase of  $V_{DSon}$  (without  $I_{DSX}$  degradation) were characterized as " $V_{DSon}$  degraded chips". Furthermore, some of the  $I_{DSX}$  degraded chips were selected for failure analysis.

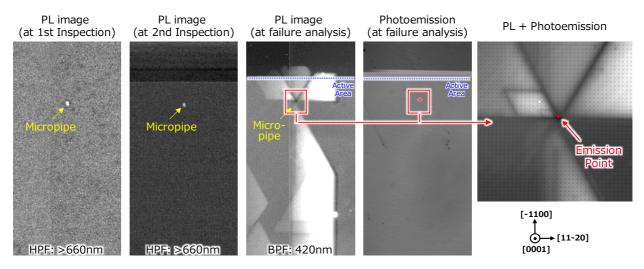

In the failure analysis, the points of abnormal leakage in the  $I_{\rm DSX}$  degraded chips were first identified using photoemission microscopy from the backside of the chip after removing the backside electrode. Following this, the frontside electrodes and gate structures were removed, and PL imaging was performed to analyze the expanded single Shockley stacking fault (1SSF). The result of photoemission microscopy and PL imaging were then overlaid to identify the crystal defects causing abnormal leakage. In addition, defect inspection results from the device fabrication process were reviewed, and the crystal defects responsible for the degradation were determined.

**Fig. 1.** (a) Schematic cross-section of the planar-type 3.3 kV SiC-MOSFET investigated in this study. (b) Flow-chart of the experimental procedure. During failure analysis, photoemission microscopy and PL imaging were conducted to identify the crystal defects.

## Analysis of *I*<sub>DSX</sub> Degraded Chips

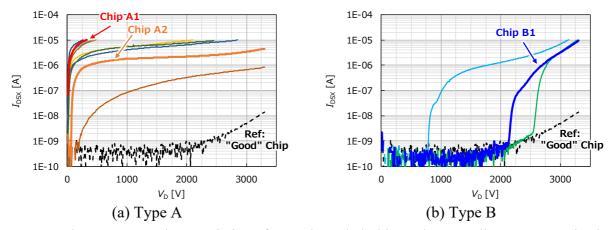

BD stress was applied to more than 1,500 chips, and out of the 159 degraded chips, 45 showed  $I_{\rm DSX}$  degradation. Figure 2 shows the leakage current characteristics of the  $I_{\rm DSX}$  degraded chips (n=13) selected for failure analysis. Compared to the passing chip, a clearly abnormal leakage current was observed. Two types of leakage current characteristics were identified: chips with abnormal leakage starting at a relatively low drain voltage ( $V_{\rm D}$ ) are referred to as Type A (Fig. 2 (a)), while those with leakage starting at a high  $V_{\rm D}$  are categorized as Type B (Fig. 2 (b)).

Fig. 2. Leakage current characteristics of  $I_{DSX}$  degraded chips. The compliance current in the measurement was set to  $10\mu A$ . (a) Type A: Chips with abnormal leakage starting at low  $V_D$ . (b) Type B: Chips with abnormal leakage starting at high  $V_D$ .

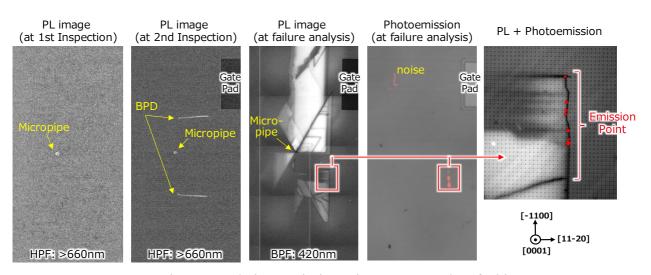

**Type A.** Figure 3 shows the PL image and the results of photoemission microscopy for Chip A1, as shown in Fig. 2 (a). In the initial PL image taken during defect inspection (after epitaxial growth), a white dot was detected, identified as a micropipe [12]. After activation annealing, basal plane dislocations (BPDs) propagated from the micropipe, and 1SSFs expanded from the propagated BPDs and micropipe itself (more precisely, from the BPDs surrounding it) after the high current stress. Notably, the strain associated with the micropipe generates a BPD cluster around the micropipe in the epitaxial layer [14]. Overlaying the photoemission and PL image revealed abnormal leakage near the periphery of the expanded 1SSF originating from the BPDs.

**Fig. 3.** PL images and photoemission microscopy results of Chip A1.

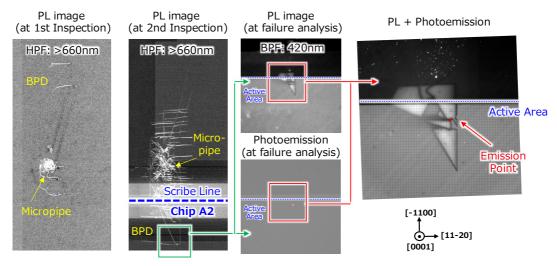

Figure 4 shows the analysis results for Chip A2 shown in Fig 2 (a). In this chip, BPDs also propagated after activation annealing, and photoemission was observed near the periphery of the expanded 1SSFs originating from these BPDs. Notably, the micropipe itself is in a neighboring chip, not within Chip A2. This indicates that the micropipe does not directly cause  $I_{DSX}$  degradation; rather, the propagated BPDs are responsible for the  $I_{DSX}$  degradation in Chip A2. Although failure analysis was not conducted on the neighboring chip containing the micropipe, it was categorized as an  $I_{DSX}$  degraded chip after BD stress. This finding further supports the idea that BPDs propagate from the micropipe, leading to  $I_{DSX}$  degradation.

Analysis of other Type A chips, as shown in Fig. 2 (a), revealed that abnormal leakage in all such chips occurred similarly at the periphery of the expanded 1SSFs. In each case, the origins of the expanded 1SSFs were BPDs either propagating from the micropipe inside the chip or from a neighboring chip, indicating that these BPDs around the micropipe are the primary cause of the degradation observed in Type A chips.

Fig. 4. PL images and photoemission microscopy results of Chip A2.

**Type B.** In Type B, abnormal leakage begins at a high  $V_D$ , unlike Type A. Figure 5 shows the analysis results for Chip B1 to determine if this type of degradation is also caused by the BPDs propagating from the micropipe, similar to Type A. The results in Fig. 5 show that 1SSF expanded from a micropipe, as observed in Type A; however, photoemission was detected near the micropipe itself. Unlike Type A, BPDs did not propagate from the micropipe after activation annealing in Chip B1, although BPDs are expected to be present around the micropipe since the 1SSF expanded following BD stress. This suggest that the specific BPDs causing  $I_{DSX}$  degradation in Type A may remain around the micropipe even after activation annealing, leading to degradation near the micropipe after BD stress. Similar results were observed for other Type B chips, as shown in Fig. 2 (b), where BPDs did not propagate from the micropipe after activation annealing. Thus,  $I_{DSX}$  degradation in both Types A and B is believed to be caused by similar BPDs around the micropipe.

Fig. 5. PL images and photoemission microscopy results of Chip B1.

The difference in I-V characteristics can be discussed by the photoemission point: the periphery of 1SSF in Type A and near the micropipe in Type B. In Type A, emission is observed near the periphery of 1SSF, especially at the surface side of the chip. This indicates that the defective area causing  $I_{DSX}$  degradation is near the surface of the chip, requiring a very low  $V_D$  to create a high electric field sufficient to initiate abnormal leakage. In contrast, for Type B, the defective area causing abnormal leakage is likely near the starting point of 1SSF around the micropipe. Since the starting point of 1SSF is deep within the drift layer, a high  $V_D$  is needed to achieve a sufficiently strong electric field to induce abnormal leakage at that depth. Thus, although the I-V characteristics of Types A and B are different, the underlying physical mechanisms of the leakage current may be similar, with the observed differences attributed to the varying depths of the defective areas.

#### **Discussion**

Analysis of all chips shown in Fig. 2 revealed that  $I_{DSX}$  degradation was associated with BPDs around the micropipe. To estimate the origin of other  $I_{DSX}$ -degraded chips identified in this study, defect inspection results from the device fabrication process were examined to confirm whether a micropipe was present in each chip. Table 1 shows the number of degraded chips due to BD stress and those containing micropipes. Among the 45  $I_{DSX}$  degraded chips, 43 contained micropipes. The two chips without micropipes were similar to Chip A2, where BPDs propagating from a micropipe in a neighboring chip caused  $I_{DSX}$  degradation. These results suggest BPDs around the micropipe were responsible for  $I_{DSX}$  degradation in all cases studied, as shown in Figs. 3–5.

Notably,  $I_{\rm DSX}$  degradation is not caused by all micropipes. Table 1 shows that nearly twice as many  $V_{\rm DSon}$ -degraded chips contained micropipes, without  $I_{\rm DSX}$  degradation. PL analysis of these  $V_{\rm DSon}$  degraded chips revealed the presence of expanded 1SSFs originating from the micropipe, similar to those in  $I_{\rm DSX}$ -degraded chips shown in Fig. 3–5. In addition, 34  $V_{\rm DSon}$ -degraded chips without micropipes were associated with conventional 1SSFs, such as a bar-shaped 1SSFs originating from BPDs in the substrate [15], or triangular-shaped 1SSFs from BPDs that did not convert to threading-edge dislocations (TEDs) during epitaxial growth. This suggest that most BPDs frequently observed in past studies do not induce 1SSFs with abnormal leakage. Instead, a specific structure of "killer" BPDs is likely responsible for  $I_{\rm DSX}$  degradation. These "killer" BPD may occur within micropipe or in the half-loop arrays observed in previous studies [4]. Identifying these structures is crucial for better understanding the bipolar degradation phenomenon and enhancing the reliability of SiC-MOSFETs. The high probability that such BPDs arise from the presence of a micropipe indicates that micropipes are a major crystal defect responsible for  $I_{\rm DSX}$  degradation. Since expanded 1SSFs also cause  $V_{\rm DSon}$  degradation, micropipes are critical for contributors to both  $V_{\rm DSon}$  and  $I_{\rm DSX}$  degradation in the bipolar degradation phenomenon.

**Table 1.** Result of high current stress testing (BD stress) and the number of degraded chips containing micropipes.

| Test<br>Chips<br>[pcs] | After High Current Stress      |                                |                                     |                                        |                |

|------------------------|--------------------------------|--------------------------------|-------------------------------------|----------------------------------------|----------------|

|                        | $I_{ m DSX}$ Degradation [pcs] |                                | V <sub>DSon</sub> Degradation [pcs] |                                        | Total<br>[pcs] |

| >1500                  | 45                             |                                | 114                                 |                                        | 159            |

|                        |                                | ,                              | ,                                   |                                        |                |

|                        |                                | $I_{ m DSX}$ Degradation [pcs] |                                     | V <sub>DSon</sub> Degradation<br>[pcs] |                |

| w/ Micropipe           |                                | 43                             |                                     | 80                                     |                |

| w/o Micropipe          |                                | 2*                             |                                     | 34                                     |                |

<sup>\*</sup>Degradation due to micropipe in the neighborhood chip

#### **Summary**

To further understand the bipolar degradation phenomenon in SiC,  $I_{DSX}$  degraded SiC-MOSFETs after BD stress were analyzed in detail. The findings suggested that micropipes was the root cause of all  $I_{DSX}$  degradation observed in this study. BPDs propagating from the micropipe after activation annealing led to  $I_{DSX}$  degradation in many chips, and even BPDs from neighboring chips could cause  $I_{DSX}$  degradation, despite the absence of micropipes in the degraded chips themselves. Given the micropipes can also induce  $V_{DSOn}$  degradation, they must be considered as one of the most critical crystal defects in the bipolar degradation phenomenon.

## References

- [1] A. Galeckas, J. Linnros, and P. Pirouz, Appl. Phys. Lett., vol.81 (2002), p. 883.

- [2] M. Skowronski and S. Ha, J. Appl. Phys., vol. 99 (2006) 011101.

- [3] A. Agarwal, H. Fatima, S. Haney, and S.-H. Ryu, IEE Electron Device Lett., vol. 28 (2007), p. 587.

- [4] R. Stahlbush, Q. Zhang, A. Agarwal, and N. A. Mahadik, Mater. Sci. Forum, vol. 717-720 (2012), p. 387.

- [5] S. A. Mancini, S. Y. Jang, Z. Chen, D. Kim, J. Lynch, Y. Liu, B. Raghothamachar, M. Kang, A. Agarwal, N. Mahadik, R. Stahlbush, M. Dudley, and W. Sung, Proc. IRPS 2022, p. 62-1

- [6] S. Yamamoto, Y. Nakao, N. Tomita, S. Nakata, and S. Yamakawa, Mater. Sci. Forum, vol. 778-780 (2014), p. 951.

- [7] T. Ishigaki, T. Murata, K. Kinoshita, T. Morikawa, T. Oda, R. Fujita, K. Konishi, Y. Mori, and A. Shima, Proc. ISPSD 2019, p. 259.

- [8] M. Uchida, N. Horikawa, K. Tanaka, K. Takahashi, T. Kiyosawa, M. Hayashi, M. Niwayama, O. Kusumoto, K. Adachi, C. Kudou, and M. Kitabatake, IEDM Tech. Dig., (2011), 26.6.1.

- [9] T. Tawara, T. Miyazawa, M. Ryo, M. Miyazato, T. Fujimoto, K. Takenaka, S. Matsunaga, M. Miyajima, A. Otsuki, Y. Yonezawa, T. Kato, H. Okumura, T. Kimoto, and H. Tsuchida, J. Appl. Phys., vol. 120 (2016), p. 115101-1.

- [10] S. Hino, H. Hatta, K. Sadamatsu, Y. Nagahisa, S. Yamamoto, T. Iwamatsu, Y. Yamamoto, M. Imaizumi, S. Nakata, and S. Yamakawa, Mater. Sci. Forum, vol. 897 (2017), p. 477.

- [11] Y. Ebihara, J. Uehara, A. Ichimura, S. Mitani, M. Noborio, Y. Takeuchi, and K. Tsuruta, Proc. ISPSD 2019, p. 35.

- [12] K. Ishibashi, H. Amishiro, T. Tanaka, N. Tomita, A. Imai, Y. Nakao, H. Watanabe, Y. Kagawa, and A. Furukawa, Proc. PCIM Europe 2023, p. 167.

- [13] M. Kato, O. Watanabe, T. Mii, H. Sakane, and S. Harada, Sci. Rep., vol. 12 (2022) 18790.

- [14] R. Stahlbush, N. Mahadik, P. Bonanno, J. Soto, B. Odekirk, W. Sung, and A. Agarwal, Proc. IRPS 2022, p. 65-1

- [15] K. Konishi, S. Yamamoto, S. Nakata, Y. Nakanishi, T. Tanaka, Y. Mitani, N. Tomita, Y. Toyoda, and S. Yamakawa, J. Appl. Phys., vol. 114 (2013), p. 014504.