# Suppression and Analysis of Bipolar Degradation in 4H-SiC PiN Diodes through Proton Implantation

Submitted: 2024-09-20

Revised: 2025-03-20

Online: 2025-09-05

Accepted: 2025-04-03

Atsushi Shimbori<sup>1,a\*</sup>, Ryota Wada<sup>2,b</sup>, Nobuhiro Tokoro<sup>2,c</sup>, Takashi Kuroi<sup>2,d</sup>, Hiu Yung Wong<sup>3,e</sup> and Alex Q. Huang<sup>1,f</sup>

<sup>1</sup>J.J. Pickle Research Center, The University of Texas at Austin, Bldg. #160, 10100 Burnet Rd. Austin, TX 78758, USA

<sup>2</sup>Nissin Ion Equipment Co., LTD., 75 Nishikujo Higashihieijo-cho, Minami-ku, Kyoto, Japan

<sup>3</sup>San Jose State University, One Washington Square, San José, CA 95192, USA

<sup>a</sup>ashimbo@utexas.edu, <sup>b</sup>wada\_ryota@nissin.co.jp, <sup>c</sup>tokoro\_nobuhiro@nissin-gr.com,

<sup>d</sup>kuroi takashi@nissin.co.jp, <sup>e</sup>hiuyung.wong@sjsu.edu, <sup>f</sup>aqhuang@utexas.edu

**Keywords:** SiC PiN Diode, Bipolar Degradation, Proton Implantation, Forward Voltage Drop, TCAD, Basal Plane Dislocation, Stacking Fault, Minority Carrier Lifetime, and Electroluminescence

**Abstract.** In this paper, a method for suppressing bipolar degradation through proton implantation was investigated. Previous work suggests implantation applied to the full thickness of the epi layer [1], which results in unwanted defects leading to a deterioration in performance. In this work, proton implantation to the buffer layer was successful in reducing the forward-voltage drift  $\Delta V_F$  of the fabricated SiC PiN diode by 85% at a current density of  $800 \text{A/cm}^2$ , when applying room temperature (RT) proton irradiation at a dose of  $1 \times 10^{16}$  cm<sup>-2</sup>. Irradiation solely to the buffer layer keeps the deterioration of forward current performance to a minimum, while the fabricated SiC PiN diodes are more robust against bipolar degradation at higher current density. In addition, RT proton irradiated PiN diodes show full recovery from their bipolar degraded characteristics within 2.5 h of annealing at 350 °C under vacuum. This indicates proton irradiation alters the crystal structure for the stacking fault (SF) to "shrink" back with ease to their initial basal plane dislocations (BPD) state.

## Introduction

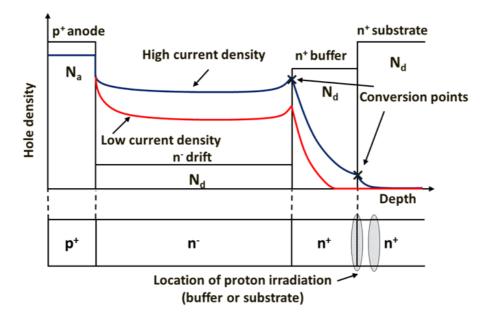

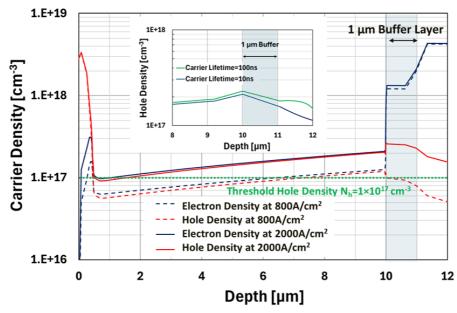

Long-term reliability of 4H-SiC MOSFETs has always been a concern, and one major issue is the increase of its body diode's  $V_F$  (forward voltage drop) from bipolar degradation phenomenon. This is caused by the expansion of SFs that originated from BPDs in the SiC substrate. Inserting a buffer layer with a short carrier lifetime is one way to prevent electron-hole recombination from triggering SFs growth [2]. However, at higher current density, the hole concentration can be much higher and reach the n-buffer/n<sup>+</sup> substrate interface where BPD-TED (threading edge dislocation) conversion points are present (Fig. 1).

**Fig. 1**. Hole density distribution of the 4H-SiC PiN diode and the location of proton irradiation

This threshold hole density is estimated to be around  $1\times10^{17}$  cm<sup>-3</sup>, where we start to observe  $V_F$  drifts within the 2 h accelerated stress evaluation period. Proton irradiation hinders the recombination-enhanced dislocation glide motion and is implemented for the suppression of SF expansion. In addition, proton implantation through the buffer layer creates a tail of recombination centers, i.e.  $Z_{1/2}$  centers, which are known to be carrier lifetime killers (Fig. 2b). Because of these recombination centers, an even shorter minority carrier lifetime ( $\tau$  <10ns) is achieved, leading to less injected holes reaching the buffer layer/substrate interface (Fig. 6).

#### **Fabrication**

An epitaxial layer, with a thickness of 10μm and a nitrogen doping concentration of 9×10<sup>15</sup> cm<sup>-3</sup>, was grown by the CVD method with a high growth rate of 30μm/hr. BPD density was further decreased by fast epitaxy as well as adding a buffer layer with a thickness of 1μm and a doping concentration of 2×10<sup>18</sup> cm<sup>-3</sup>. The wafers were irradiated at 200°C and RT with 170keV or 50keV protons at a dose of 1×10<sup>15</sup> cm<sup>-2</sup> and 1×10<sup>16</sup> cm<sup>-2</sup>, before and after the epitaxial growth of the 1μm buffer layer. The anticipated hydrogen distribution profiles were confirmed through SRIM simulation (Fig. 2a), ensuring maximum peaks occurring at the buffer layer/substrate interface or in a 300nm depth of the substrate surface. For PiN diode fabrication, the anode region with a concentration of 8.0×10<sup>19</sup> cm<sup>-3</sup> was formed through high temperature Al implantation at 400°C, and then an activation anneal was performed at 1700 °C for 30 min. Circular Al-based metal contact stacks (Ti/Al/Ti/Au=70nm/100nm/5nm/120nm) were patterned on the anode region, and Ni-based metal contact stacks (Ti/Ni/Ti/Au=20nm/90nm/5nm/120nm) were deposited on the back side of substrate for cathode electrode. Post metallization annealing was performed at 950°C for 90 sec.

**Fig.2.** SRIM simulation of the hydrogen implantation profile ((a) Linear plot shows H<sup>+</sup> profile of 170keV with a dose of  $1\times10^{16}$  cm<sup>-2</sup> to the buffer layer and H<sup>+</sup> profile of 50keV with a dose of  $1\times10^{16}$  cm<sup>-2</sup> to the substrate. (b) Log plot shows a long tail of hydrogen ions within the buffer layer from implantation at 170keV with a dose of  $1\times10^{16}$  cm<sup>-2</sup>)

#### **Results and Discussion**

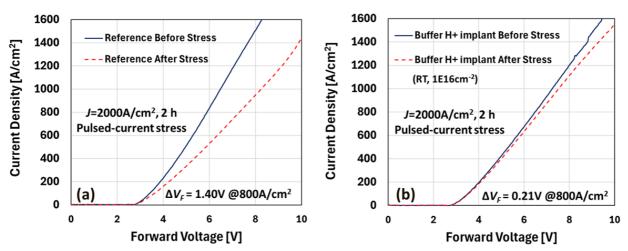

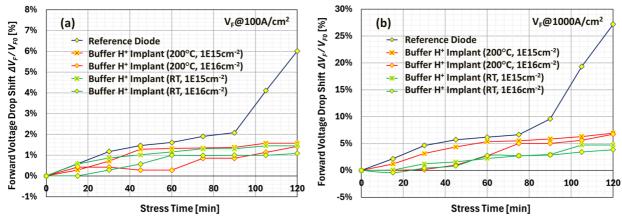

For the bias stress, a 1-ms-long 11V voltage pulse, equivalent to roughly ~ 2000 A/cm<sup>2</sup> in current density, was injected at a frequency of 3.33 pulses/s for 2 h to observe bipolar degradation. The duty cycle was kept low to prevent thermomechanical failure from elevated junction temperature. While the reference PiN diode without proton implantation showed forward-voltage drift  $\Delta V_F$  of 1.40V after 2 h stress, RT proton implantation at a dose of 1×10<sup>16</sup> cm<sup>-2</sup> to the buffer layer was successful in reducing the forward-voltage drift  $\Delta V_F$  of the fabricated SiC PiN diode by 85% ( $\Delta V_F$  =0.21V) at a current density of 800A/cm<sup>2</sup> (Fig.3). Additionally, by comparing the before stress *I-V* characteristics of reference PiN diode and PiN diode with proton implantation to the buffer layer, it is apparent that irradiation solely to the buffer layer keeps the deterioration of forward current performance to a minimum. On the other hand, proton implantation onto the substrate did not significantly influence the suppression of bipolar degradation, exhibiting comparable levels of decline in forward current performance. Finally, the amount of forward voltage drop shift was expressed in percentage increase from the original value  $(\Delta V_F/V_{F0})$  [%]) to compare the performance degradation between different irradiation conditions within the 2 h accelerated stress evaluation period. Figure 4a shows an increase in  $V_F$  which was observed at current density of 100A/cm<sup>2</sup>, while Figure 4b shows an increase in  $V_F$ observed at current density of 1000A/cm<sup>2</sup>. As shown in Fig. 4, when the proton dose increases

**Fig. 3.** Bipolar degradation comparison of (a) reference PiN diode and (b) PiN diode with proton implant to the buffer layer (RT, dose of  $1 \times 10^{16}$  cm<sup>-2</sup>)

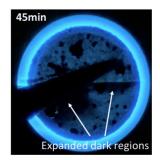

$(1\times10^{15} \text{ cm}^{-2}=>1\times10^{16} \text{ cm}^{-2})$ , it becomes more difficult for the partial dislocations to move, which results in less  $V_F$  drifts. It is also worth mentioning that room temperature implant has more effect on suppressing bipolar degradation over 200°C heated implant, indicating the additional damage created introduces an increased number of point defects such as proton impurities, vacancies, and interstitials which all play a significant role in hindering the dislocation glide motion. The forward voltage drop shift does not show an immediate rise, but it involves an initial activation phase up to 90 min of stress time. This activation time is dependent on the stress current density. In other words, the higher the value, the faster the bipolar degradation occurs with less activation time [3]. This suggests that there exists a specific threshold for hole density, as well as a total cumulative energy requirement from the electron-hole recombination process that must be met for bipolar degradation to commence. Electroluminescence (EL) images were additionally obtained under identical stress to a mesa-isolated PiN diode without proton implantation capturing an expansion of dark regions originating from the glide of stacking faults (Fig. 5).

**Fig. 4.** Plots of stress time vs forward voltage drop shift in percentage, showing forward biased performance degradation (a)  $V_F@100A/cm^2$ , (b)  $V_F@1000A/cm^2$

Fig. 5. Time evolution of electroluminescence microscopy images under bias stress, capturing expansion of stacking faults

## **Simulation and Numerical Analysis**

The carrier density distribution of the designed 4H-SiC PiN diode was calculated at different current densities through TCAD simulation to estimate the hole concentration present at the buffer layer/substrate interface when bipolar degradation starts to occur. The simulation model was set having a P<sup>+</sup> anode region with a depth of 0.5μm and a peak hole density of 3.5×10<sup>18</sup> cm<sup>-3</sup>, a drift layer in the thickness of 10µm and doping concentration of 9×10<sup>15</sup> cm<sup>-3</sup>, and a buffer layer with a thickness of 1 µm and a doping concentration of 2×10<sup>18</sup> cm<sup>-3</sup>. Carrier density distributions were plotted with two different current density conditions (800A/cm<sup>2</sup> and 2000A/cm<sup>2</sup>), just below and above the trigger current density when bipolar degradation starts to occur. The estimated threshold hole density is calculated to be around  $1\times10^{17}$  cm<sup>-3</sup>, where we start to observe  $V_F$  drifts within the 2 h accelerated stress evaluation period [4]. Furthermore, it is assumed that the carrier lifetime reduction was caused by the introduction of  $Z_{1/2}$  centers through the hydrogen implantation tail in the buffer layer. From referencing past publications on carrier lifetime dependence on proton dose, the estimated carrier lifetime  $\tau$  is less than 10 ns,  $1/10^{th}$  of the original value ( $\tau = 100$ ns), in the irradiated buffer layer with the proton dose of 1×10<sup>16</sup> cm<sup>-2</sup> [5]. The simulation indicates this reduction of carrier lifetime may also play a role in suppressing SF expansion, as enhanced recombination in the buffer layer further reduces the holes from reaching the buffer layer/substrate interface [6].

**Fig. 6.** Carrier density distribution of the designed 4H-SiC PiN diode with  $10\mu m$  thick epi layer with doping concentration of  $9\times10^{15}$  cm<sup>-3</sup> and  $1\mu m$  thick buffer layer with doping concentration of  $2\times10^{18}$  cm<sup>-3</sup>

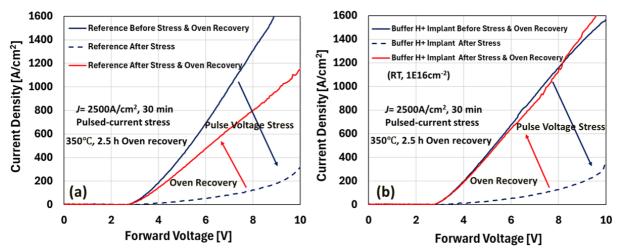

**Fig. 7.** Forward *I-V* characteristics of the fabricated PiN diodes before and after 2.5 h of stressing at 2500 A/cm<sup>2</sup> pulse current and recovery behavior observed through annealing at 350 °C under vacuum

#### **Reversal of Forward-Voltage Drift**

Reversal of the forward voltage drifts has been reported in the past by ways of low temperature annealing [7],[8], and, through the following experiment, the effects of proton implantation in the recovery process have been investigated. Both the reference PiN diode and proton implanted diode were stressed in a similar manner, applying 1-ms-long 12V voltage pulse, equivalent to roughly~ 2500 A/cm<sup>2</sup> in current density, and were injected at a frequency of 3.33 pulses/s for 30min. A current density of 2500 A/cm<sup>2</sup> is associated with a hole density value that is significantly higher than the threshold value (N<sub>h</sub>=1×10<sup>17</sup> cm<sup>-3</sup>). At this level of stress, the BPDs located in deeper region, beyond the effective range of the hydrogen implant profile, and within the substrate, are presumably being activated. This activation leads to both the reference diodes and those implanted with H<sup>+</sup> to exhibit comparable levels of bipolar degradation [9]. Both fabricated PiN diodes were then annealed at 350 °C under a vacuum pressure of 4×10<sup>-5</sup> bar for 2.5 h and slowly cooled to room temperature. Subsequently, to assess the impact of annealing on the degraded forward *I-V* characteristics of the stressed PiN diodes, electrical characteristics were measured once more. The RT proton irradiated PiN diode showed full recovery from their bipolar degraded characteristics within 2.5 h of annealing (Fig. 7b), while the reference PiN diode was only midway of full recovery (Fig. 7a). This indicates proton irradiation alters the crystal structure for the stacking fault (SF) to "shrink" back with much ease to their initial basal plane dislocations (BPD) state.

## **Summary**

In conclusion, this study investigated the method for suppressing bipolar degradation through proton implantation. Proton implantation to the buffer layer was successful in reducing the forward-voltage drift  $\Delta V_F$  of the fabricated SiC PiN diode by 85% at a current density of 800A/cm², by applying room temperature proton irradiation at a dose of  $1\times10^{16}$  cm<sup>-2</sup>. Implantation at higher dose  $(1\times10^{16}$  cm<sup>-2</sup> over  $1\times10^{15}$  cm<sup>-2</sup>) and RT over 200°C heated implant was more effective in suppressing stacking fault expansion, indicating the additional damage created hindered the recombination-enhanced dislocation glide motion, resulting in less  $V_F$  drifts. Furthermore, it is assumed that the carrier lifetime degradation is due to the introduction of  $Z_{1/2}$  centers associated with the hydrogen implantation tail across the whole thickness of the buffer layer. The estimated carrier lifetime  $\tau$  in the buffer layer is less than 10 ns and this reduction in lifetime may also have played a role in suppressing SF expansion. The estimated threshold hole density through TCAD simulation is to be around  $1\times10^{17}$  cm<sup>-3</sup>. In addition, RT proton irradiated PiN diodes showed full recovery from their bipolar

degraded characteristics within 2.5 h of annealing at 350°C under vacuum. This indicates proton irradiation alters the crystal structure for the stacking fault (SF) to "shrink" back with much ease to their initial basal plane dislocations (BPD) state.

## Acknowledgements

The authors of this paper would like to thank Nissin Ion Equipment Co. Ltd for their support in the implantation process.

#### References

- [1] Kato, M., Watanabe, O., Mii, T., Sakane, H., and Harada, S., "Suppression of stacking-fault expansion in 4H-SiC PiN diodes using proton implantation to solve bipolar degradation", Sci Rep 12, 18790 (2022), doi: 10.1038/s41598-022-23691-y.

- [2] T. Kimoto et al., "Understanding and reduction of degradation phenomena in SiC power devices," 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2017, pp. 2A-1.1-2A-1.7, doi: 10.1109/IRPS.2017.7936253.

- [3] Long, Y., Chen, Y., Wang, P., Hou, B., and He, H., "A Novel Insight Into the Mechanism of Bipolar Degradation in 4H-SiC MOSFET," in IEEE Electron Device Letters, vol. 46, no. 3, pp. 464-467, March 2025, doi: 10.1109/LED.2025.3528065.

- [4] Mii, T., Sakane, H., Harada, S., and Kato, M., "Analysis of carrier lifetime in a drift layer of 1.2-kV class 4H–SiC devices toward complete suppression of bipolar degradation" Materials Science in Semiconductor Processing (2023), doi: 153. 107126. 10.1016/j.mssp.2022.107126.

- [5] Harada, S., Mii, T., Sakane, H., and Kato, M., "Suppression of stacking fault expansion in a 4H-SiC epitaxial layer by proton irradiation", Sci Rep 12, 13542 (2022), doi:10.1038/s41598-022-17060-y

- [6] Li, T., Sakane, H., Harada, S., and Kato, M., "Suppression of stacking-fault expansion in 4H-SiC diodes by helium implantation", Applied Physics Express, vol. 17, no. 8, Art. no. 086503, IOP, 2024, doi:10.35848/1882-0786/ad6be5

- [7] V. Veliadis *et al.*, "Degradation and Full Recovery in High-Voltage Implanted-Gate SiC JFETs Subjected to Bipolar Current Stress," in *IEEE Electron Device Letters*, vol. 33, no. 7, pp. 952-954, July 2012, doi: 10.1109/LED.2012.2196674.

- [8] Caldwell, J.D., Stahlbush, R.E., Hobart, K.D., Glembocki, O.J., and Liu, K.X., "Reversal of forward voltage drift in 4H-SiC p-i-n diodes via low temperature annealing," Appl. Phys. Lett., vol. 90, no. 14, pp. 143 519–143 522, Apr. 2007, doi: 10.1063/1.2719650

- [9] Hayashi, S., Yamashita, T., Senzaki, J., Kato, T., Yonezawa, Y., Kojima, K., and Okumura, H., "Relationship between depth of basal-plane dislocations and expanded stacking faults by application of forward current to 4H–SiC p-i-n diodes", Applied Physics Express, vol. 12, no. 5, Art. no. 051007, IOP, 2019, doi: 10.7567/1882-0786/ab1305